Phase noise in DDS

advertisement

Phase noise in DDS

C. E. Calosso❖, Y. Gruson★, E. Rubiola★

❖ INRIM, Torino, Italy

★ CNRS FEMTO-ST, Besancon, France

Outline

• A short introduction

• Theory

• Experiments

home page http://rubiola.org

2

Basic DDS scheme

integer: nk = (nk 1 + N ) mod D

complex: zk = zk 1 exp(j⌘)

phase: ✓k = (✓k 1 + ⌘) mod 2⇡

quantity

state variable

output

D-type

register

DAC

adder

control

word

DAC

N

z plane

D = 2m

2⇡

={z}

N

⌫0 = ⌫s

D

cos

1

✓k

✓k

1

time

clock freq. ⌫s

N

D

k, 0, 1, 2, . . . t = k/⌫s

N

output freq. ⌫0 = ⌫s

D

N

⌘ = 2⇡

The contents n of the m-bit register

is interpreted as a complex number

zk

zk

increment

<{z}

carry

sin

modulo

k

<{z}

time t = k/⌫c

={z}

clock

n

analog

n

✓ = 2⇡

D

z = ej✓

assoc. complex

LUT

⌫s

digital

k

3

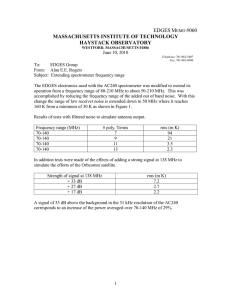

AD9912, a popular fast DDS

48 bit accumulator, 14 bit DAC, 1 GHz clock

48

D=2

N

48-BIT ACCUMULATOR

48

48

48

DAC I-SET

REGISTERS

AND LOGIC

PHASE

OFFSET

AD9912

16

D Q

19

19

DAC_RSET

ANGLE TO

14

AMPLITUDE

CONVERSION

DAC_OUT

DAC SYSCLK PLL

Multiplier

(14-BIT)

DAC_OUTB

When the SYSCLK

PLL multiplier path is employed, the

frequency applied to the SYSCLK input pins must be limited so

as not to exceed the maximum input frequency of the SYSCLK

fS phase detector. A block diagram of the SYSCLK generator

PLL

appears in Figure 45.

06763-032

FREQUENCY

TUNING WORD

(FTW)

AD9912

look-up

table

Figure 40. DDS Block Diagram

is a 48-bit FTW that provides the accualue. On each cycle of fS, the accumulator

FTW to the running total of its output.

FTW = 5, the accumulator counts by 5s,

fS cycle. Over time, the accumulator

of its capacity (248 in this case), at which

aining the excess. The average rate at which

over establishes the frequency of the

DAC

SYSCLK PLL MULTIPLIER

ICP

clock (125µA, 250µA,

375µA) K

VCO

(HI/LO)

multiplier

2

is internally connected to a virtual voltage reference of 1.2 V

FROM current

nominal, so the reference

can beCHARGE

calculated by

PHASE

SYSCLK

INPUT

I DAC _ REF

1.2

R DAC _ REF

FREQUENCY

DETECTOR

VCO

PUMP

1GHz

~2pF

÷N

DAC

SAMPLE

CLOCK

÷2

33)

μA, which

Note that the recommended value of IDAC_REF(N =is2 TO120

LOOP_FILTER

of 10 kΩ.

leads to a recommended value for RDAC_REF

Figure 45. data

Block Diagram

of theFig.

SYSCLK45

PLL

AD9912

sheet,

The scale factor consists of a 10-bit binary number (FSC)

06763-037

AD9912 data sheet, Fig. 40

100 MHz parallel 8-bit programming

3.3 V single supply

Multiple power-down functions

Single-ended or differential input reference clock

Small 80-lead LQFP

Ultrahigh speed comparator, 3 ps rms jitter

Excellent dynamic performance

80 dB SFDR at 100 MHz (±1 MHz) AOUT

4× to 20× programmable reference clock multiplier

Dual 48-bit programmable frequency registers

Dual 14-bit programmable phase offset registers

12-bit programmable amplitude modulation and

shaped on/off keying function

Single-pin FSK and BPSK data interfaces

PSK capability via input/output interface

Linear or nonlinear FM chirp functions with single-pin48

frequency hold function

Frequency-ramped FSK clock

D-type

<25 ps rms

in clock generator mode

clock

in total jittermultiplier

4

AD9854, a popular DDS

APPLICATIONS

48 bit accumulator,

300

MHz

clock,

Agile, quadrature LO frequency synthesis

clock generators

12 bit DAC, I-Q output, Programmable

AM/PM/FM

capability

FM chirp source for radar and scanning systems

Test and measurement equipment

Commercial and amateur RF exciters

D=2

register

FUNCTIONAL BLOCK DIAGRAM

SYSTEM

CLOCK

MUX

48

48

48

17

17

14

INV

SINC

FILTER

BIDIRECTIONAL

INTERNAL/EXTERNAL

I/O UPDATE CLOCK

12-BIT

I

DAC

12

ANALOG

OUT

DAC RSET

12-BIT

Q DAC OR

CONTROL

DAC

ANALOG

OUT

3

MUX

MUX

MUX

12

DELTA

FREQUENCY

RATE TIMER

2

48 SYSTEM

CLOCK

DELTA

FREQUENCY

WORD

SYSTEM

CLOCK

48

FREQUENCY

TUNING

WORD 1

MODE SELECT

SYSTEM

CK

CLOCK

Q

D

INT

EXT

48

14

ANALOG

IN

PROGRAMMABLE

AMPLITUDE AND

RATE CONTROL

12

CLOCK

OUT

PROGRAMMING REGISTERS

÷2

SYSTEM

CLOCK

AD9854

OSK

BUS

INTERNAL

PROGRAMMABLE

UPDATE CLOCK

GND

I/O PORT BUFFERS

WRITE

SERIAL/

PARALLEL

SELECT

digital

interface

Figure

1.

quadrature

DAC

COMPARATOR

12

I AND Q 12-BIT

FREQUENCY

FIRST 14-BIT

SECOND 14-BIT

12-BIT DC

TUNING

PHASE/OFFSET PHASE/OFFSET AM MODULATION CONTROL

WORD 2

WORD

WORD

READ

AD9854 data sheet, Fig. 1

14

12

6-BIT ADDRESS

OR SERIAL

PROGRAMMING

LINES

+VS

8-BIT

PARALLEL

LOAD

MASTER

RESET

00636-001

modulation

FM / PM / AM

DEMUX

Q

FSK/BPSK/HOLD

DATA IN

12

SYSTEM

CLOCK

12

in-phase

DAC

DIGITAL MULTIPLIERS

MUX

I

INV

SINC

FILTER

MUX

4× TO 20×

REF CLK

MULTIPLIER

12

MUX

DIFF/SINGLE

SELECT

REF

CLK

BUFFER

DDS CORE

PHASE

ACCUMULATOR

ACC 2

REFERENCE

CLOCK IN

FREQUENCY

ACCUMULATOR

ACC 1

SYSTEM CLOCK

MUX

≤ 300 MHz

look-up

table

PHASE-TOAMPLITUDE

CONVERTER

N

amplitude

control

5

Theory

• Simple gearbox model

• Quantization noise

• Sampling theorem

• Spurs

• [PLL clock multiplier]

The noise-free synthesizer

jitter xout = xin

phase 'out = N

D 'in

jitter xin

phase 'in

!out

!in

!out

N teeth

N

= !in

D

D teeth

• The noise-free synthesizer propagates the jitter x (phase time)

• So, it scales the phase φ as N/D,

• and the phase spectrum Sφ as (N/D)2

• Notice the absence of sampling

6

7

The Egan model

for phase noise in frequency dividers

S' (f )

(N/D)2

(N/D)2

input

input

stage

output

stage

× N/D

noise-free

synthesizer

output

input signal

actual output

output stage

(N/D)2

noise-free synth output

f

For N/D <<1, the scaled-down noise hits the output-stage limit

W.F. Egan, Modeling phase noise in frequency dividers, TUFFC 37(4), July 1990

8

Quantization noise

W. R. Bennett, Spectra of quantized signals, Bell System Tech J. 27(4), July 1948

Analog-to-digital conversion introduces a

quantization error x [–VLSB/2 ≤ x ≤ +VLSB/2]

v(t)

error

x

VLSB

n-bit conversion: VLSB

t

sampling point

p(x)

1

2

2

VLSB

=

12

VLSB

S(f )

Wiener–Khintchine theorem: in ergodic

systems, interchange time / ensemble

The noise can be calculated with statistics

2

VLSB

= NB

B = 12 ⌫s (Nyquist)

2

VFSR

=

12 ⇥ 22n

V

2

1/12 –> –10.8 dB

22n –> 6 dB/bit

Parseval theorem: Energy (power) calculated

in time and in frequency is the same

N

2

VFSR

= n

2

B f

2

VFSR

N=

6 ⇥ 22n ⌫s

V2 /Hz

Quantization and PM noise

The maximum power is

1 2

P0 = VFSR

8

VFSR

RF

f

Recall the

quantization noise

N=

6

s

S' (f )

S(f )

N

2

VFSR

⇥ 22n ⌫

In the presence of white noise N,

the PM noise is

PM noise

P0

V2

b0

N

b0 =

P0

f

rad2 /Hz

The white PM noise is

4

1

b0 =

3 22n ⌫s

rad2 /Hz

Example:

14 bit, 1 GHz –> –173 dB

14 bit , 400 MHz –> –169 dB

12 bit, 300 MHz –> –156 dB

9

Is b0 (white PM) affected by ν0?

• Consider two synthesized signals, ν0 < ν1 (i.e., ν1 = n ν0 )

• Same sampling frequency νs >> ν1

• ν0 has factor-n more samples-per-period than ν1

• Does ν0 have lower PM noise than ν1 ?

• The answer is NO!

• Analyzing at the Fourier frequency ƒ with a resolution

bandwidth B, the measurement time is ≈ 1/B

• The degrees of freedom are νs/B, regardless of νout

• Accordingly, b0 (white PM noise) at ν0 and ν1 is the same

10

11

Phase noise sampling

in

out

active edge

D Q

ck

t

t

equivalent sampling function

• The input noise is sensed only during the rising edges

• This is equivalent to sampling at the at the clock frequency

• The phase noise in the full input bandwidth is “aliased” to

half the clock frequency

12

Phase noise sampling in dividers

in

out

÷D

synchronous divider

input sampling frequency ⌫c

t

in

jitter is discarded

jitter is

transmitted

jitter is discarded

jitter is

transmitted

jitter is discarded

jitter is

transmitted

jitter is

transmitted

t

out

output sampling frequency ⌫0 =

1

D ⌫c

• The output jitter results from sampling the input jitter at the

frequency ν0 = νc / D

• Aliasing increases the white part of Sφ by a factor of D

(S' )out

1

= (S' )in

D

• The 1/D2 law still holds for autocorrelated noise (flicker, walk)

13

State-variable truncation

nk = (nk

1

m

⌫c

clock

D = 2m

+ N ) mod D,

p

LUT

q

D-type

register

carry

m

q

DAC

adder

N

m

m

DAC

output

sin

N

⌫0 = ⌫c

D

cos

2m visible

states

control word

2m 2p

hidden states

m

• Only quantization shows up

with full m-bit conversion

• Technology –> q max

• Why p > q

• Slow pseudorandom beat,

3d 6h 11m 15s @ 1 GHz, 48 bit

• Spurs –> next

total D = 2

pitch

N

⌫0 = ⌫s

D

se

pha

or

t

c

e

v

2⇡

states

2⇡

rad

2m

k

t=

⌫s

✓

N

rad

D

t=

visible pitch

2⇡

rad

2p

error

⇡

± q rad

2

k

1

⌫s

mber of Overflows = GRR/(Capacity/ETW) = 2048/(4096/1422) = 711

14

Truncation generates spurs

h this information it is possible to visualize the behavior of the truncation word as shown in

ure 4.8 below.

Period of

Sawtooth

Amplitude

Analog Devices, A technical tutorial on digital signal synthesis, 1999

2B

1

2

3

711

2m visible

states

1

0

⌫0 =

Clock Cycles

1

2

3

4

5

6

7

8

9

2046

2047 2048

2050

total D = 2m states

Grand Repitition Rate

Amplitude

Figure 4.8. Behavior of the Truncation Word

pitch

2⇡

rad

2m

t=

Spectral lines of sawtooth waveform.

e that the truncation word accumulates up to a maximum value of 2B. It has the shape of a

wtooth waveform with a period of 4096/1422 clock cycles. It should be apparent that the

wtooth shape results from the overflow characteristic of the accumulator. Also note that the

mplete sequence of truncation word values repeats after a period of 2048 clock cycles. Since

0 the truncation word is periodicF sin the time domain, then its fourier

2 F s transform is

behavior of

iodic in the frequency domain. Also, the truncation word sequence is a real sequence, so the

rier transform may be represented by half as many frequency points as there are periodic time

Amplitude

of spectral

due to aliasing

main points

(because the fourier transform ofRemapping

a real time

domainlines

sequence

is symmetric about

origin in the frequency domain). Hence, there will be 1024 discrete frequencies associated

h the behavior of the truncation word, and these frequencies constitute the truncation spurs.

thermore, the spectrum of the truncation word sequence will be related to that of a sawtooth

veform. The fundamental frequency of the sawtooth is Fs x (ETW/Capacity) or 0.3472 Fs for

example given. The spectrum of a sawtooth waveform is comprised of harmonics of its

F s discrete frequencies associated

2 F s with the

damental.0 Since we know that there are 1024

ncation word sequence, then the spectrum consists of triangle waveform with 1024

quencies spaced at intervals of 0.3472Fs. This spans a frequency range of 355.5Fs. This, of

Amplitude

rse, results

in aliasing of the higher order harmonics into the Nyquist bandwidth, Fs/2. Figure

Remapped

spurs

below illustrates

thistruncation

phenomenon.

The power

of spurs comes at expenses of white noise

t=

visible pitch

2⇡

rad

2p

k

⌫s

✓

ctor

e

v

se

pha

N

2⇡

rad

D

2m 2p

hidden states

2051

N

⌫s

D

error

⇡

± q rad

Frequency

2

3Fs

Frequency

3Fs

– yet not as one-to-one

k

1

⌫s

Nonlinearity generates spurs

15

non-linearity

rd

harmonic distortion

Analog Devices, A technical tutorial

on digital signal synthesis, 1999

from ½Fs to Fs. The 3 Nyquist zone is from Fs to 1.5Fs, and so on. Frequencies

st

Nyquist zones map directly onto the 1 Nyquist

zone, while frequencies in the EV

aliasing

st

ist zones map in mirrored fashion onto the 1 Nyquist zone. This is shown pictori

spurs

e 4.10.

f

Nyquist

Zone

Mapping

0

1st

2nd

3rd

4th

5th

6th

7th

Direct

Mirror

Direct

Mirror

Direct

Mirror

Direct

0.5Fs

Fs

1.5Fs

2Fs

2.5Fs

3Fs

3.5Fs

LOOP FILTER

AVDD

When the SYSCLK PLL multiplier path is employed, the

16

R1

FERRITE

frequency applied to the SYSCLK input pins must be limited so

C2 reduce the cost

another existing system clock. They permit simplified BEAD

applications and

as not to exceed the maximum input frequency of the SYSCLK

C1

supplying a high frequency clock oscillator.

PLL phase detector. A block diagram of the SYSCLK generator

LOOP_FILTER

appears in Figure 45.

The REFCLK Multiplier feature is not the optimum solution

application

thou

29 for26every 31

•

On-Silicon

LC

oscillator

is a tradeoff in terms of output signal quality whenever REFCLK frequency multiplicat

SYSCLK PLL MULTIPLIER

~2pF noise within the PLL l

involved. Multiplication will• degrade

oscillator

phase

(also reference

used inCHARGE

other AD

devices)VCO

ICP

by 20 LOG (Fout/Fclk), where Fout isPUMP

the multiplied output frequency and F

(125µA, 250µA, 375µA) bandwidth

KVCO

Literature

suggests

≈ 5…10

(HI/LO)

AD9912

PLL

reference clock. For•example,

a 6X clock

multiplier will Q

degrade

the input clock p

2

noise of a –110 dBc/Hz oscillator

by 15.5 fdB =

which

resultsMHz

in a –94.5 dBc/Hz reference

• Leeson

50–100

L

Figure

46. External Loop Filter for SYSCLK PLL

FROM

phase noise. Furthermore,

the PLL loop filter characteristics may cause “peaking” of th

PHASE

DAC

CHARGE

SYSCLK

FREQUENCY

VCO response SAMPLE

noise

near cutoff.• Figure

5-4PLL

demonstrates

typicalLoop

DDS Filter

outputValues

phase noise

de

PUMP

Tight

is needed

Table

5. Recommended

for a N

INPUT

DETECTOR

CLOCK

in1GHz

the AD9851 device which has the

filter PLL

on-chip.

DDS devices with

1.5entire

MHzloop

SYSCLK

LoopOther

Bandwidth

~2pF

• Divider

noise

of the loop filter off-chip will

generally not

demonstrate peaking in the filter response.

PLL clock multiplier

LOOP_FILTER

-90

-100

-110

The SYSCLK PLL multiplier has a 1 GHz VCO at its core. A

- 1 2 0 provide the

phase/frequency

detector

(PFD)

and

charge

pump

The AD 9854 is likely

steering signal to the VCO in typical PLL fashion.

- 1 3 0 The PFD

similar, yet the VCO

operates on the falling edge transitions of the input signal, which

-140

frequency is 300 MHz

means that the loop locks on the negative edges of the reference

5 0 I/O register

signal. The charge pump gain is controlled via- 1the

map by selecting one of three possible constant

current

sources

-16

0

ranging from 125 μA to 375 μA in 125 μA steps. The center

-170

frequency of the VCO is also adjustable via the I/O register map

and provides high/low gain selection. The feedback path1 0from 1 0 0

VCO to PFD consists of a fixed divide-by-2 prescaler followed

4

Figure 45. Block Diagram of the SYSCLK PLL

06763-037

(N = 2 TO 33)

R1

Series C1

the

390manufacturer

Ω

1 nF

470 Ω

820 pF

1 kΩ

390 pF

2.2 kΩ

180 pF

2.7 kΩ

pF to PLL

Phase noise 120

response

1/f LL

pe

P

slo rder

do

2n

AD9912

÷2

Phase Noise in dBc/Hz

÷N

Multiplier

• No data

from

<8

10

20 a

This is just

40 (default)

wild guess!

60

Sh

82

56

27

10

5p

loop filter “peaking” at cutoff

Detail of SYSCLK Differential Inputs

6x

Leeson

frequency?

A

the

input pins

is provided in F

C l odiagram

c k M u l t i p l i eof

r en

g a g SYSCLK

ed

Included are details of the internal 1components

used

/f 2

input circuitry. These components have a direct effec

c t CSYSCLK

locking

static levels Dati r ethe

input pins. This informat

intended to aid in determining how best to interface

free-running VCO?

device for a given application.

1k

Frequency Offset in Hertz

CRYSTAL RESONATOR WI

10k

10M

1 0 0 kMUX 1 M

SYSCLK PLL ENABLED

–50

51

SF

–60

17

–70

–80

–80

–100

100

1k

10k

100k

1M

10M

AD9858

Figure 19. Residual Phase Noise (SSB) with f

FREQUENCY OFFSET (Hz)

b–1 = –150 dB

40.1MHz

15.1MHz

100

100

1K

10K

100K

(Hz)

1k FREQUENCY

10k

100k

1M

1M

10M

10M

1k

75

100

100

SUPPLY CURRENT (mA)

POWER DISSIPATION (mW)

615

600

610

500

b–1

b–1 = –101 dB

400

=605

–113

dB

300

600

200

595

100

48 bit accu, 14 bit dac

fc=400MHz, 1.8V cmos

b0 = –152 dB

b0 = –159 dB

f =4

o

0 MH

z

f = 10

o

MHz

0

590

100250

100

0

1k 375

10k500

100k625

1M750

10M875

10k

100k 100 1M120

20 1kSYSTEM

40

60

80

f (Hz) CLOCK FREQUENCY (MHz)

FREQUENCY

(Hz)

FREQUENCY

(MHz)

Figure Phase

18. Power

Dissipation

System

Clock Freq

Figure 17. Residual

Noise

with fOUT =vs.

159.5

MHz,

Figure

21.

Supply

Current

vs.=Output

Frequency;

Variation

Figure

11. AD9956

DDS/DAC

Residual

Phase

Noise

fSYSCLK

/5,

Driver

On, CM

(SYSCLK

PLL

Bypassed),

fOUT

MSPS;

PLL

Bypassed

(Green),

PLL

Set

toHSTL

4×

(Red),

and

fCLK = 400

Expressed

as

a

Percentage,

and

Heavily

Dependent

on Tun

400 MHz

Clock,

10

MHz

Output

SpurKiller Off

PLL Set to 20× (Blue)

Figure= 18.

Residual

Phase

Noise,(SYSCLK

300 MHzPLL

REFCLK

SYSCLK

1 GHz

Wenzel

Oscillator

Bypassed),

FigureMultiplier

22. PowerBypassed

vs. System

Clock

Frequency

with

REFCLK

HSTL Output Doubler Enabled

AD9912

AD9951, AD9952, AD9953, AD9954

00

800

single output,

32 bit accu, 14 bit dac

–10

–10

diff.

aux

functions

f

–20

–20

700

c=400MHz, 1.8V cmos

–30

–30

–120

–40

Rev. D | Page–40

15 of 52 f 600

–50

–50

o = 9.5 MHz

clock multiplier enabled

–60

–60

500

–130

–70

–70

–80

–80

b–1 = –107 dB

400

–90

–90

TO

–100

–100

–140

300

b0 = –153 dB

3.3

–110

–110

1.8

150MHz

–120

–120

–120

–60

200

–130

–130

–130

–150

50MHz

–140

–140

–140

–70

100

–150

–150

–150

10MHz

–160

–160

–160

f (Hz)–80

–160

–170

–170

0

–170

–90

100

1k 10

10k100

100k1K

1M10K

10M

0

200 100k

3001M

10

100

1k 100

10k

100

10

100K 100M1M

10M

Figure 16. Absolute FREQUENCY

Phase NoiseOFFSET

Using

CMOS

Driver

OUTPUT

(Hz)

FREQUENCY

(Hz)FREQUENCY (MHz)

f (Hz)

FREQUENCY

(Hz) at 3.3 V,

SYSCLK –100

= 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed)

CENTER

50.17407705MHz

1.5MHz/Driver at 3.3 V,SPAN 15MHzFigure 18. Residual Phase

Figure

19.with

Power

Frequen

Noise

fOUTDissipation

= 9.5 MHz, vs.

fCLKOutput

= 400 MSPS;

FigureRun

16.at

Absolute

Phase

Using CMOS

DDS

200

MSPS

for Noise

10 MHz

PHASE

NOISE (dBc/Hz)

L(f)

(dBc/Hz)

100.3MHz

b–1 = –116 dB

fo =75.1MHz

103 MHz

03166-A-014

–170

–170 10

10

32 bit accu, 10 bit dac

fc=1GHz, 3.3V cmos

AOUT = 5MHz

95

10k

100k

1M

10M

100M

10k (Hz)

150 1k 200 OFFSET

250

300 100k

350

4001M 450

FREQUENCY

FREQUENCY (Hz)

FREQUENCY

(MHz)

Figure 15. Absolute PhaseCLOCK

Noise Using

HSTL Driver,

–110

05785-020

PHASE

PHASENOISE

NOISE,(dBc/Hz)

L(f) (dBc/Hz)

–120

–140

–130

–140

–150

–150

–160

–160

AD9858

single output

115

–150

–170 100

10

OUT = 15.1 MHz, 40.1 MHz,

75.1 MHz, 100.3 MHz, fCLK = 500 MHz with REF_CLK Multiplier Bypassed

0

–10

–70

–20

–80

–30

–40

–90

–50

–60

–100

–70

–110

–80

–90

–120

–100

–110

–130

600MHz b0 = –149 dB

700

0

RMS JITTER (100Hz TO 20MHz):

–10

b–1 = –94 dB

150MHz: 308fs

–20

0

50MHz: 737fs

–30

1

–40 b = –103.5 dB

–10

–1

b0 = –141.5 dB

–50

–20

–60

b–1 = –110.5 dB

–70

–30

–80

b0 = –145 dB

–90

–40

b0 = –154 dB

–100

–50

–110

04806-0-024

03374-029

10

–150

–140

dB

TOTAL

3.3V

1.8V

single output

POWER DISSIPATION (mW)

–170

135

–160

15.1MHz

25

b0 = –159 dB

06763-016

b–1 = –117 dB

800MHz

AOUT = 80MHz

05785-022

b–1 = –108.7 dB

–160

–130

–140

1 =

155–1

B

AD9956

800

620

03166-A-015

40.1MHz

b–

175

4d

0

0

–10

–10

–20

–20

–30

–30

–40

–40

–50

–50

–60

–60

–70

–70

–80

–80

–90

–90

–100

–100

–110

–110

–120

–120

–130

–130

–140

–140

–150

–150

–160

–160

–170

–17010

10

500

L(f)(dBc/Hz)

(dBc/Hz)

L(f)

–140

–130

10

9.5 dB

–130

=–

9.5 dB

b0 = –151 dB

b0 = –154 dB

100.3MHz

b0 = –157 dB

b0 = –161 dB

–120

1

14 dB

b–1 = –100.2 dB

195

–120

b–

c

10

15 1MHz 20

SPAN

DAC CURRENT (mA)

05785-057

PHASE NOISE (dBc/Hz)

PHASE NOISE (dBc/Hz)

–120

05785-019

PHASE NOISE (dBc/Hz)

b–1 = –102.5 dB

RMS JITTER (100Hz TO 100MHz):

48 bit accu,

600MHz:

585fs 12 bit dac

800MHz:

406fs 3.3V cmos

f =300MHz,

two outputs:

cos+aux

/ I-Q

215

5

100kHz/

Figure 10. AD9956

DAC

Performance:

400 MSPS

Figure 20.

SFDR

vs. DAC Current,

59.1 AClock,

OUT, 300 MHz R

MHz Span

160 MHz Fwith

OUT, 1

REFCLK

Multiplier Bypassed

L(f)

L(f)(dBc/Hz)

(dBc/Hz)

–110

–110

AD9852, AD9854

235

POWER (mW)

75.1MHz

–150

SPAN 50kHz

00634-018

06763-015

–100

–100

32 bit accu, 10 bit dac

fc=1GHz, 3.3V cmos

1/2/4 outputs

–110

48

0

CENTER 159.5MHz

Figure 17. Narrow-band SFDR, 39.1 MHz, 50 kHz BW, 200 MHz REFCLK

with REFCLK Multiplier Bypassed

AD9911, AD9958, AD9959

–100

–100

AD9954

Probably related toAD9912

the cell size and to the

dynamic range

5kHz/

CENTER 39.1MHz

(dB)

PHASE

NOISE, L(f) (dBc/Hz)

AD9911

00634-017

–90

1

49

–90

04806-0-023

03374-028

–70

50

04806-0-021

3.3 V: lower PM noise than 1.8 V

–60

FREQUENCY OFFSET (Hz)

Figure 12. AD9956 DDS/DAC Residual Phase Noise

Figure 15. Residual Phase Noise, 103 MHz FOUT, 1 GHz REFCLK

Figure 18. Residual Phase Noise, 403 MHz FOUT, 1 GHz REFCLK

SYSCLK

= 1toGHz

PLL

Bypassed),

Driv

PLL Bypassed (Green),

PLL Set

4×

(Red),

and

PLL

Set to 20×HSTL

(Blue)

SYSCLK = 1Figure

GHz Wenzel

Oscillator

(SYSCLK PLL

Bypassed)

23.

Amplitude

Modulation

Using

Primary

Channel

400

MHz

Clock,

40(SYSCLK

MHz Output

E. 20.

Rubiola,

2007

(adapted

Devices

Figure

ResidualMar

Phase

Noise

(SSB) withfrom

fOUT =the

15.1Analog

MHz, 40.1

MHz, data sheets)

CMOS Driver On, SpurKiller Off

DDS

200 MSPS

for 10

MHz Plot

(CH1Run

= 50atMHz)

and One

Auxiliary

Channel (CH0 = 1 MHz)

75.1 MHz, 100.3 MHz, fCLK = 500 MHz with REF_CLK Multiplier = 5×

0

–10

Plots originally used to extract the noise parameters

–110

0

–10

10

RMS JITTER (100Hz TO 20MHz):

CARRIER:

399MHz

18

Experiments

• AD9912 demo board

• AD9854 (9914) demo board

• Claudio’s AD9854 board

• V1 – Current feedback OPA output stage

• 25Ω input impedance, 8 nV/√Hz noise, kHz coupled

• V2 – Balun and MAV-11 RF output amplifier

• F = 3.6 dB, AC coupled (≥1–2) MHz

• Specified above 50 MHz, yet works well below

19

Experimental method (PM noise)

• Pseudorandom noise, slow beat (days)

• The probability that two accumulators are in phase is ≈ 0

• Two separate DDS driven by the same clock have a random

and constant delay

• The delay de-correlates the two realizations, which makes

the phase measurement possible

Single channel

Dual channel

kind of virtual mixer, after (sub)sampling & direct ADC

TSC5125A

DUT

IF

DUT

× N/D

LO

90º adjust

DUT

phase

meter

IN

× N/D

phase

meter

REF

× N/D

synth

cross spectrum

RF

FFT analyzer

× N/D

× N/D synth

Claudio’s prototypes

balun

AD9912

balun

Cyclon

AD9854

AD9954

MAV11

20

PM noise vs. output frequency

Balun and MAV-11 at the DDS output

30 dB/dec

thermal effect?

22

.5

M

Hz

11

:

b

.2

5

M –1 =

5.

–1

62 Hz

14

2. 5 M : b

.5

81

Hz –1 =

dB

M

:

–1

1.

Hz b

40

: –1 = 2 0.

6

b

5

M

–

–

12 dB

Hz

1 ≈

:

–1 6 d

b

30 B

–1

dB

≈

–1

33

.5

dB

DDS internal stages

power supply

b0 ≈ –155 dB

b0 ≈ –159.5 dB

b0 ≈ –162.5 dB

(DDS) output stage

21

22

AD9912 noise vs. out frequency

– low Fourier frequencies –

INRIM

PM noise vs. output frequency

AD8002 current-feedback

opamp at the DDS out

b–1 = –108.5 dB

scales ≈ as 1/ν2

–140 dB@ 180 MHz

(AD8002 white)

30 dB/dec

thermal effect?

1.4

hits b–1 = –130 dB

INRIM

11 22. 45 M

5.6 .25 5 M

Hz

MH

H

M

2

5M H

z&

z: : b

z

Hz : b b– –1 = –

2.8

: b –

1 =

MH

1 =

–1 108.

–1 =

–

5

1

z:

–1 120. 4.5 d dB

b

26 5 d

–1 ≈

B

dB B

–1

30

dB

• The –140 dB floor is due to AD8002 at the DDS output

• The flicker is unchanged (comes from the DDS)

23

Figure 17. Narrow-band SFDR, 39.1 MHz, 50 kHz BW, 200 MHz REFCLK

with REFCLK Multiplier Bypassed

–110

AD9852, AD9854

two outputs:

cos+aux / I-Q

–120

–130

b–

–140

1

=–

1

=–

10

4d

B

Specs,

regular output

AOUT = 80MHz

12

5d

B

b0 = –159 dB

b0 = –149 dB

–150

–160

AOUT = 5MHz

–170

10

100

1k

10k

FREQUENCY (Hz)

100k

Figure 18. Residual Phase Noise, 300 MHz REFCLK

with REFCLK Multiplier Bypassed

1M

Flicker is in fair agreement

White is made low by spurs

who

2

rad /Hz

meas, dB math, dB

clock, MHz

specs

–159

–155.8

300

YG

–158

–155.0

250

CC

–162.5

–153.6

180

25

00634-020

5

24

2:($3−29)

’dds34_clock250MHz_out_10MHz.txt’

u

2:($3−28)

Figure 20. SFDR vs. DAC Current, 59.1 AOUT, 300 MHz

REFCLK

’dds34_clock250MHz_out20MHz_amp77.txt’

u 2:($3−29)

with REFCLK Multiplier Bypassed u 2:($3−28)

’dds34_clock250MHz_out40MHz_amp77.txt’

’dds34_clock250MHz_out80MHz_amp77.txt’ u 2:($3−28)

’amp77_24_10_10MHz.txt’ u 2:($3−29)

620

250 MHz clock, DDS noise

615

610

hits –158 dB

8 0 MH

z: –10

4 0 MH

0 dB

z: –10

6

2

d

0

1 0 MH

B

M

H

z:

z

5 MHz

: –124: –118 dB –113 dB

dB

605

600

595

1

590

10

100

1000

10000

f (Hz)

0

20

40

60

80

100

FREQUENCY (MHz)

120

140

Balun and MAV-11 at the DDS output

100000

Figure 21. Supply Current vs. Output Frequency; Variation Is Minimal,

dB/dec

Expressed as30

a Percentage,

and Heavily Dependent on Tuning Word

Rev. D | Page 15 of 52

Basic formula for white noise

4

1

b0 =

3 22n ⌫s

10

15

20

DAC CURRENT (mA)

’dds34_clock250MHz_out_4p8MHzv2.txt’

u

00634-018

PHASE NOISE (dBc/Hz)

b–

48 bit accu, 12 bit dac

fc=300MHz, 3.3V cmos

dB rad²/Hz

–100

−30

−40

−50

−60

−70

−80

−90

−100

−110

−120

−130

−140

−150

−160

−170

−180

00634-021

SPAN 50kHz

48

0

SUPPLY CURRENT (mA)

5kHz/

CENTER 39.1MHz

00634-0

AD9854 noise

–100

thermal effect?

22

.5

M

Hz

11

:

b

.2

5

–1

=

M

5.

H

–1

62

z:

14

5

2.

b

.5

M

81

Hz –1 =

dB

M

:

–

1.

H

12

40

z: b–1

0.

6

=

b

5

M

–

–1

12 dB

Hz

≈

:

–1 6 d

b

30 B

–1

dB

≈

–1

33

.5

dB

DDS internal stages

power supply

b0 ≈ –155 dB

b0 ≈ –159.5 dB

b0 ≈ –162.5 dB

(DDS) output stage

dB rad²/Hz

AD9854 I–Q noise

25

I-Q PM noise. Take away 3 dB

for 2 equal outputs (DACs)

Flicker is in quite a good

agreement between YG and CC

b–1 = –118 dB,

scales as 1/ν2

I–Q spectra cannot be

compared to specs

−30

−40

−50

−60

−70

−80

−90

−100

−110

−120

−130

−140

−150

−160

−170

−180

–140 dB@ 180 MHz:

(opa AD8002 white)

’dds3_clock_250MHz_out_IQ_5MHz.txt’ u 2:($3−28)

’dds3_clock250MHz_out_IQ_10MHz.txt’ u 2:($3−29)

’dds3_clock_250MHz_out_IQ_20MHz_v3.txt’ u 2:($3−29)

’dds3_clock250MHz_out_IQ_40MHz.txt’ u 2:($3−29)

’dds3_clock250MHz_out_IQ_80MHz.txt’ u 2:($3−29)

hits b–1 = –132 dB

250 MHz clock, I–Q noise

INRIM

80 MH

z: –11

3 dB

20 MH 40 MHz:

z: –12

–119 d

B

10 MH 4 dB

z: –12

8 dB

5 MHz

: –131

dB

1

10

hits –158 dB

100

1000

f (Hz)

10000

100000

45

22 MH

.

z

≤ 5 11.2 5 MH : b

5 M z –1 =

.6

MH

–

Hz : b

: b –1 = 118

z:

d

b

–1

–1 ≈ –1 =

24 B

–

12

d

–1

9d B

32

dB

B

?

?

PM noise vs. output amplitude

thermal effect?

b

–1 ≈

–1

24

b

–1

dB

≈

–1

26

.5

dB

1/P law

6 dB / factor-2

amplitude,

DDS units

balun and RF amplifier at the DDS out

180 MHz clock

b0 ≈ –135 dB

b0 ≈ –141 dB

b0 ≈ –147 dB

flicker almost

constant, vs. P

b0 ≈ –153 dB

b0 ≈ –158 dB

likely limited by the

measurement system

b0 ≈ –162 dB

• PM noise scales 6 dB per factor-of-two output amplitude

• Signature of digital multiplication: lower amplitude is obtained

by reducing the integer number at the DAC input

26

INRIM

1/f4 from thermal

fluctuation?

another flickerlike process?

flicker

b–1 ≈ –122 dB

–163 dB @ –8 dBm

–167 dB @ +7 dBm

Clock amplitude

PM noise vs. clock amplitude

from supply voltage

27

28

The effect of the clock frequency

INRIM

Clock

frequency

(≥ 200 MHz spec)

50

10

40

MH

z

0M

20

0M

Hz

0M

Hz

Hz

dB rad²/Hz

Thermal effects

0

−10 250 MHz clock small heat sink ’dds2.dat’ u 1:($2+3)

’bancdds2.dat’ u 1:($2+3)

−20 10 MHz output

’dds3.dat’ u 1:($2+3)

’bancdds3.dat’

u 1:($2+3)

−30

−40

−50

–4

−60

0d

−70

B/

–

de

2

0 dB

−80

c

/

d

e

−90

c

bac

kgr

oun

−100

bac

d

kgr

flicker

−110

ou

large heat sink

nd

−120

−130

−140

−150

−160

−170

−180

0.0001

0.001

0.01

0.1

1

10

f (Hz)

• Low-frequency temperature fluctuations

induce phase noise

• A large thermal mass helps

29

AD9912 Voltage sensitivity

+/- 5%

2 Hz

1.8 V

3.3 V

400 MHz

Agilent

E8257D

Power

Splitter

(PSC-2-1,

Minicircuits)

4 dBm

Input

AD9912

Demo board

Phasemeter

Symmetricom

TSC5125A

Reference

30

AD9912 temperature sensitivity

• Temperature control

(chamber)

• Measured: –2 ps/K

• Includes cables, baluns

etc

31

32

supply voltage ±5%

AD9912

time

thermal

effect

thermal

transient

voltage effect

time, s

AD9912

sensitivity to

temperature

(alternate)

AD9912 temperature sensitivity

thermal coefficient

INRIM

output frequency

• High frequency: –2 ps/K, constant

• Low frequency: 1/ν3 law

33

0

250

06763-015

–150

100

PM noise of the AD 9912

1k

10k

100k

1M

FREQUENCY OFFSET (Hz)

10M

100M

Figure 15. Absolute Phase Noise Using HSTL Driver,

SYSCLK = 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed),

HSTL Output Doubler Enabled

–120

800

RMS JITTER (100Hz TO 20MHz):

150MHz: 308fs

50MHz: 737fs

b–1 = –103.5 dB

10

M

Hz

:–

50

11

600

0

M

dB

Hz

:

–1

25

1

M 500

Hz 6 dB

:–

12

12

.5

M

400 2 d

Hz

B

:–

12

8

6.

dB300

25

M

Hz

:–

3.

12

13200

5

1

M

Hz .5 d

:– B

13

100

1.

5

dB

b0 = –141.5 dB

b–1 = –110.5 dB

14 dB

–150

150MHz

50MHz

10MHz

f (Hz)

–160

100

b0 = –153 dB

1k

10k

100k

1M

10M

100M

Figure 16. Absolute FREQUENCY

Phase NoiseOFFSET

Using CMOS

Driver at 3.3 V,

(Hz)

SYSCLK = 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed)

FigureRun

16.at

Absolute

Phase

Using CMOS Driver at 3.3 V,

DDS

200 MSPS

for Noise

10 MHz

Figure 19. Power Dissipation vs. Output Freque

SYSCLK = 1 GHz (SYSCLK PLL Bypassed), HSTL Dri

CMOS Driver On, SpurKiller Off

SYSCLK = 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed)

DDS Run at 200 MSPS for 10 MHz Plot

–120

–130

10

CARRIER:

SFDR W/O SPURKILLER:

SFDR WITH SPURKILLER:

FREQUENCY SPAN:

RESOLUTION BW:

VIDEO BW:

• At 50 MHz and 10/12.5 MHz we get ≈15 dB lower flicker

–10

than the data-sheet spectrum

–20

• Experimental conditions unclear in the data

sheets

–30

RMS JITTER (100Hz TO 20MHz):

50MHz: 790fs

0

ER (dBm)

–110

TO

3.

1.

0

0 MHz: –129 dB

100(!!!)

200

300

1.56

OUTPUT FREQUENCY (MHz)

06763-016

–140

b0 = –145 dB

9.5 dB

9.5 dB

–130

INRIM

700

0

POWER DISSIPATION (mW)

b–1 = –94 dB

34

500

625

750

875

SYSTEM CLOCK FREQUENCY (MHz)

Figure 18. Power Dissipation vs. System Clock Fre

(SYSCLK PLL Bypassed), fOUT = fSYSCLK/5, HSTL Driver On, CM

SpurKiller Off

AD9912

–110

375

–40

399MHz

–63.7dBc

–69.3dBc

500MHz

3kHz

30kHz

Spurs reduce the white noise

AD9854, ck 300 MHz

INRIM

floor

reduction

spurious

35

Spurs can be amazing

36

More about a PM-noise bump

• Low PSRR (power-supply

rejection ratio) of PM

noise

AD9912

400 MHz clock, 25 MHz out

INRIM

• For instance The AD9912

at 25 MHz out has 15 ps/%

supply-voltage sensitivity

• No bump at 103–105 Hz is

seen in the data-sheet

spectra

• DC regulator may show a

similar bump, alone or or

with the output capacitor

X7R SMD capacitor shows low ESR (≤5 mΩ)

37

PLL clock multiplier

10 –> 640 –> 10 MHz

38

PLL clock multiplier

10 –> 640 –> 10 MHz

39

PLL clock multiplier

40

41

Effect of other parts on the PCB

INRIM

A blinking LED somewhere on the PCB spoils the output spectrum

ADEV vs. clock frequency

fH = 500 Hz and fH = 50 Hz

specs: ck ≥ 200 MHz

C.Calosso & E.Rubiola, May 2012

Commented:

Original: 02_AD9912_scanFck/FckScan_01_adev.png

42

ADEV vs. output frequency

fH = 500 Hz and fH = 50 Hz

th

er

eff ma

ec l

t

C.Calosso & E.Rubiola, May 2012

Commented:

Original: 01_AD9912_scanF/FoutScan_01_adev.png

43

ADEV vs. output frequency

th

er

eff ma

ec l

t

44

Experimental method (AM noise)

Pa

Va

Pb

Vb

source

under test

monitor

power

meter

Schottky

power

detectors

dual channel

FFT analyzer

Cross-spectrum

•Averaging on m spectra, the singlechannel noise is rejected by √1/2m

•

va (t) = 2ka Pa (t) + noise

vb (t) = 2ka Pb (t) + noise

The cross spectrum Sba(f ) rejects

the single-channel noise because

the two channels are independent.

1

Sba (f ) =

S (f )

4ka kb Pa Pb

A cross-spectrum higher

than the averaging limit

validates the measure

Sα(f)

log/log scale

single channel

1

2m

cross spectrum

meas. limit

frequency

E. Rubiola, The measurement of AM noise of oscillators, arXiv:physics/0512082, Dec. 2005

E. Rubiola, F. Vernotte, The cross-spectrum experimental method, arXiv:1003.0113v1 [physics.ins-det], Feb. 2010

46

Sα(f) (dB/Hz)

AM noise (1)

−30

’./am_dds3_4p8MHz.dat’ u 1:(($2/2)−11)

−40 AD9854

’./am_dds3_10MHz_v4.dat’ u 1:(($2/2)−12)

−50 4.8–80 MHz output ’./am_dds3_20MHz.dat’ u 1:(($2/2)−13)

’./am_dds3_40MHz.dat’ u 1:(($2/2)−11)

’./am_dds3_80MHz.dat’ u 1:(($2/2)−11)

−60

−70

h–1 = –105…–115 dB

4.8 MHz

−80

−90

40 MHz

−100

−110

−120

−130

−140 80 MHz

−150

20 MHz

10 MHz

−160

−170 250 MHz clock, AM noise (cross spectrum)

−180

1

10

100

1000

10000

f(Hz)

100000

−60

−70

−80

−90

−100

−110

−120

−130

−140

−150

−160

−170

−180

single channel

h–1 = –112 dB

single channel

cross spectrum

250 MHz clock, AM noise

1

10

100

1000

h–1 = –115 dB

’./am_dds3_20MHz.dat’ u 1:(($2/2)−13)

’./am_dds3_20MHz_voie1.dat’ u 1:($2−13)

’./am_dds3_20MHz_voie2.dat’ u 1:($2−12)

Sα (f) (dB/Hz)

Sα (f) (dB/Hz)

20 MHz output

single channel

single channel

cross spectrum

1

10

100

1000

10000

−30

’./am_dds3_4p8MHz.dat’ u 1:(($2/2)−11)

−40 4.8–80 MHz output

’./am_dds3_10MHz_v4.dat’ u 1:(($2/2)−12)

’./am_dds3_20MHz.dat’ u 1:(($2/2)−13)

−50

’./am_dds3_40MHz.dat’ u 1:(($2/2)−11)

’./am_dds3_80MHz.dat’ u 1:(($2/2)−11)

−60

−70

h–1 = –105…–115 dB

4.8 MHz

−80

−90

40 MHz

−100

−110

−120

−130

−140 80 MHz

−150

20 MHz

10 MHz

−160

−170 250 MHz clock, AM noise (cross spectrum)

−180

1

10

100

1000

10000

100000

f(Hz)

10000

f(Hz)

−30

−40

−50

−60

−70

−80

−90

−100

−110

−120

−130

−140

−150

−160

−170

−180

47

AM noise (2)

Sα(f) (dB/Hz)

Sα (f) (dB/Hz)

Sα (f) (dB/Hz)

−30

4.8 MHz output

’./am_dds3_4p8MHz.dat’ u 1:(($2/2)−11)

−40

’./am_dds3_4p8MHz_voie1.dat’ u 1:($2−11)

’./am_dds3_4p8MHz_voie2.dat’ u 1:($2−11)

−50

−60

−70

−80

h–1 = –105 dB

−90

single channel

−100

single channel

−110

−120

−130

−140

−150

−160

cross spectrum

−170 250 MHz clock, AM noise

−180

1

10

100

1000

10000

100000

−30

f(Hz)

’./am_dds3_10MHz_v4.dat’

u 1:(($2/2)−12)

−40 10 MHz output

’./am_dds3_10MHz_voie1_v4.dat’ u 1:($2−11.5)

’./am_dds3_10MHz_voie2_v4.dat’ u 1:($2−11.5)

−50

−30

’./am_dds3_80MHz.dat’ u 1:(($2/2)−11)

−40 80 MHz output

’./am_dds3_80MHz_voie1.dat’ u 1:($2−11)

’./am_dds3_80MHz_voie2.dat’ u 1:($2−10)

−50

−60

−70

h–1 = –112 dB

−80

single channel

single channel

−90

−100

−110

−120

−130

−140

−150

cross spectrum

−160

−170 250 MHz clock, AM noise

−180

1

10

100

1000

10000

f(Hz)

100000

Conclusions

• Noise theory and model for the DDS

• A lot of still-not-published experimental data

• Phase noise

• Allan deviation

• Amplitude noise

• Experiments done at INRIM and at FEMTO-ST

• Model and experimental data are in fair agreement

http://rubiola.org

48