ECE 428 Programmable ASIC Design

FPGA Programmable Interconnect

and I/O Cells

Haibo Wang

ECE Department

Southern Illinois University

Carbondale, IL 62901

6-1

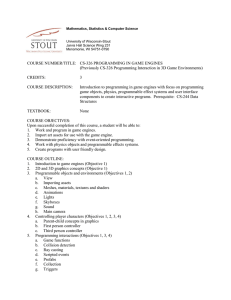

Definitions

Routing resources: wires and switches (antifuse or pass transistors) that

are used to transport signals in FPGA chips.

Routing Channels: dedicated areas with fixed sizes that contain routing

resources. Depending on wire directions in a routing channel, the channel

can be called a horizontal channel or a vertical channel.

Track & Capacity: a track holds one wire; the capacity of a routing

channel is equal to the number of tracks it holds.

wires

Switch

box

Logic

cell

Logic

cell

wires

Wire segment

Horizontal channel

Logic

cell

Logic

cell

Vertical channel

Logic

cell

6-2

Antifuse Based Programmable Interconnect

I/O cell

Antifuse

Vertical wires

Horizontal channels

Logic

cells

6-3

Antifuse Based Programmable Interconnect

FPGA layout

cell1

6

2

7

3

8

Realized connections

4

5

cell1

cell2

cell11

cell5

10

9

cell10

11

12

13

14

15

6-4

Antifuse Based Programmable Interconnect

Since an antifuse takes a very small area, an antifuse can be

implemented at every horizontal and vertical interconnect

intersection. This type structure is called fully populated.

The use of fully populated structures increase routing flexibility.

Can not re-program.

Antifuse

Horizontal wires

Vertical wires

6-5

Antifuse Based Programmable Interconnect

The metal wires and antifuse contribute significant parasitic resistance and

capacitance

The parasitic resistance and capacitance result in large signal propagation

delay and power consumption

τ D 4 = ( R1 + R2 + R3 + R4 )C4 + ( R1 + R2 + R3 )C3 + ( R1 + R2 )C2 + R1C1

Pdynamic ∝ (C1 + C2 + C3 + C4 )

6-6

Programmable Interconnect Using Pass Transistors

Horizontal wire

Pass transistor

Memory

Vertical wire

Pass transistors and their associated memories take large area.

Thus, it is unrealistic to use fully populated structure.

Normally, this type programmable interconnect has less routing

flexibility.

Can re-program.

6-7

Xilinx XC4000 Programmable Interconnect

Long wires

Double length wires

Horizontal

channel

Single length wires

Vertical channel

6-8

Xilinx XC4000 Switch Module

Switch Module

Connection example

6-9

Xilinx Programmable Interconnection Points

Double length

wires

CLB

Single length

wires

Programmable

interconnection

Point (PIP)

Routing channels

M

PIP

6-10

Xilinx XC4000 Programmable Interconnect

CLB 1

CLB 2

CLB 3

CLB1

CLB 4

CLB 5

CLB3

CLB 6

CLB9

Connection example

CLB 7

CLB 8

CLB 9

6-11

FPGA Programmable I/O Cell

I/O cells provide interface between internal FPGA circuits and

external environment.

An I/O cell can be configured as an input, output, or bidirectional

port.

D flip-flops are normally included in I/O cells to provided registered

inputs and outputs.

I/O cell

Output

Signal

Input

Signal

D

Q

I/O Pad

Q

D

I/O Cell

6-12

Xilinx XC4000 Programmable I/O Cell

6-13

SelectIO Standard

•

•

•

Allows direct connections to external signals of varied voltages and

thresholds

– Optimizes the speed/noise tradeoff

– Saves having to place interface components onto your board

Differential signaling standards

– LVDS, BLVDS, ULVDS

– LDT

– LVPECL

Single-ended I/O standards

– LVTTL, LVCMOS (3.3V, 2.5V, 1.8V, and 1.5V)

– PCI-X at 133 MHz, PCI (3.3V at 33 MHz and 66 MHz)

– GTL, GTLP

– and more!

Source: Xilinx Basic FPGA Architecture

6-14

Digital Controlled Impedance (DCI)

• DCI provides

– Output drivers that match the impedance of the traces

– On-chip termination for receivers and transmitters

• DCI advantages

– Improves signal integrity by eliminating stub reflections

– Reduces board routing complexity and component count

by eliminating external resistors

– Eliminates the effects of temperature, voltage, and

process variations by using an internal feedback circuit

Source: Xilinx Basic FPGA Architecture

6-15

0

0