Design of Inductorless, Low Power, High Conversion Gain CMOS

advertisement

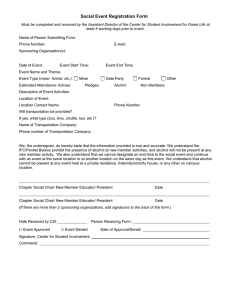

2014 IEEE International Microwave and RF Conference (IMaRC) Design of Inductorless, Low Power, High Conversion Gain CMOS Subharmonic Mixer for 2.4 GHz Application W.K. Chong, H. Ramiah, N. Vitee and G.H. Tan Dept of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia Abstract — This work describes the design and implementation of an inductorless, low power, high conversion gain fully differential subharmonic down-conversion mixer for 2.4 GHz application. A complementary current-reuse technique is adapted between the transconductance stage and LO switching stage to boost the conversion gain without additional power consumption by reusing the DC current of the LO switching stage. The proposed design has been extracted and simulated in 0.13 µm standard CMOS technology. With a power consumption of 6 mW at a supply voltage of 1.2 V, the proposed subharmonic mixer exhibits a high conversion gain (CG) of 15.18 dB, a noise figure (NF) of 16.33 dB, an 1-dB compression point (P1dB) of −16.3 dBm and an input-referred third-order intercept point (IIP3) of −6.72 dBm. Index Terms — Inductorless, low power, high conversion gain, CMOS, subharmonic mixer. I. INTRODUCTION In recent years, the development of low power transceiver is motivated in the need of withstanding longer battery life time in the implementation of wireless systems due to the slow pace of sustainable power source development. The conventional heterodyne receiver is deemed to be not suitable for low power realization and monolithic integration due to expensive, complexity, bulky integration and the necessary in high quality factor (Q-factor) IF band-select filter at the circuitry compilation [1]. In comparison with the heterodyne receiver, direct conversion receiver (DCR) is served as a viable candidate for low cost low power solution. Although the directconversion approach increases the level of integration in singlechip implementation as a result from reduced off-chip components, but it suffers from flicker noise, local oscillator (LO) signal leakage and LO self-mixing [2]. The self-mixing phenomenon results in a time varying DC offset at the mixer output which degrade the performance of mixer. Therefore, this has driven the need in exploring a new design technique to mitigate the degradation of signal to noise (SNR) performance. In a typical CMOS mixer design, low operating frequency significantly relaxes the design constraint in RF transceiver chain design especially in frequency synthesizers and oscillators. In high operating frequency, the effect of parasitic capacitance is prominent which leads the LO signal leaking into the RF port through the silicon substrate or the intrinsic parasitic of transistor. Therefore, the LO signal can mixes itself and produces a DC offset at the mixer output. In order to 274 alleviate this LO self-mixing setback, LO fundamental frequency band and RF input frequency band need to be separated in frequency proximity. Therefore, subharmonic mixer is preferred over the fundamental mixer as second or high order harmonics of LO signal is used for frequency translation. The asymmetric mismatch in subharmonic mixer design heavily attribute towards even-order distortion. Therefore, to alleviate this distortion, a fully differential topology with symmetrical physical layout is preferred. The placement of the devices and metal routing should be designed as symmetrical as possible. The differential realization also improves the linearity performance of the mixer due to even order nonlinearity cancellation. The proposed subharmonic mixer is extracted, simulated and verified in 0.13 µm standard CMOS platform. This paper is organized as follows. Section 2 addresses the insights of the subharmonic mixer design and operation. Section 3 reports the RC-extracted post layout simulation results from the implemented design while the development of work is summarized in section 4. II. PROPOSED SUBHARMONIC MIXER DESIGN The design of the inductorless, low-power, high conversion gain subharmonic mixer which operates at a supply voltage of 1.2 V is shown in Fig. 1. The usage of bulky inductor is avoided in this design to minimize the physical area consumption. The proposed architecture is based on the Gilbert-cell topology which generally achieves a good linearity performance and high port-to-port isolation in comparative to their double-balanced structure [3]. A differential RF input with relative phase shift of 0° and 180° is required. The differential RF input signal is mixed with second order harmonics of LO signal with equal amplitude and input phase shift of 0°, 90°, 180° and 270°, and effectively down-converted it to the desired IF output signal. Folded cascode architecture is a preferred solution over the conventional series stacking topology in addressing low voltage design. However, the current-reused topology is not applicable as the DC current from LO switching stage is routed into the ground instead of being used in the transconductance stage. The increase in DC current consumption has promoted in the adaptation of complementary current-reuse technique which the DC current ICR(1,2) from LO switching stage is fed into transconductance stage instead of being shunt into the ground 978-1-4799-6317-1/14/$31.00 ©2014 IEEE [4]. Therefore, the total DC current flow through the RF input transistor in Fig. 1 can be expressed as I RF= (1,2 ) I B(1,2 ) + I CR (1,2 ) . (1) In addition, as the number of switching transistor is increased, the total DC current contribution from switching stage is significantly larger. Hence, the overall conversion gain is boosted without additional power consumption. The details operation of the subharmonic mixer in Fig. 1 is described in the following mathematical analysis. When the RF input signal, VRF(t) = vRF · sin(ωRF)t is applied at the gate of the transistor M1 and M2, the gate source voltage, vgs(1,2) can be derived as v gs (1,2) 1 =± ( vRF sin ωRF t ) 2 (2) where vgs1 and vgs2 receives the differential RF input signal with 0° and 180° phase shift, respectively. The RF input transistor M1,2 serves as the transconductance transistor which dictates the conversion gain. The corresponding RF input current of the RF input voltage at node VX(1,2) can be expressed as i X (1,2) = g m (1,2) v gs (1,2) = ± g m (1,2) v RF sin ωRF t 2 . (3) The cascode transistor M3,4 is a NMOS-based common gate amplifier which provides high isolation between LO and RF ports while routing the RF signal from the transconductance stage to the LO switching stage. In addition, the transistor M3,4 also operates as a current-bleeding transistor to control the DC current flows through the LO switching transistors. At node VX(1,2), the RF signal might flow into different branch due to the existence of resistor RL(1,2), intrinsic parasitic effect and internal resistance from the transistor itself. The total impedance at node VX(1,2) can be expressed as Zin = 1 g m (3,4) || R L(1,2) || R ds(1,2) || 1 jωRF Cgs (3,4) (4) where gm(3,4) and Cgs(3,4) is the transconductance and gate-source parasitic capacitance of the transistor M3,4, respectively. RL(1,2) is the load resistor and Rds(1,2) is the impedance looking into the drain terminal of the transistor M1,2. Therefore, the AC voltage at node VX(1,2) can be expressed as follows: v X (1,2= ) Zin ⋅ i X (1,2 ) . (5) In order to fully route the RF signal into the LO switching stage, the impedance looking through the source terminal of the transistor M3,4 must be designed to be small enough. Large amount of DC current flow through the transistor M3,4 can easily boost up the gm3,4. However, this method is not well suited for the low power applications. Therefore, the gm/Id design methodology is applied to optimize and achieve a maximum transconductance with low current consumption resulting in a negligible amount of RF signal leakage through 275 VDD VB2 M5 M6 VY1 V0 VB1 M7 M8 V180 V90 VY2 M9 M10 M3 VX1 VRF+ V270V270 VIF+ IB1 ICR1 RL1 VB2 M11 M12 V90 V180 M13 M14 VB1 M4 VIF− IB2 CL1 CL2 RL2 IRF1 ICR2 IRF2 M1 Fig. 1. V0 VX2 M2 VRF− Proposed subharmonic mixer design. the resistor RL(1,2) and parasitic capacitance Cgs(3,4) as the impedance of RL(1,2) and Cgs(3,4) at the 2.4 GHz are 10 times greater than 1/gm(3,4). In the worst case scenario, the high frequency RF signal leakage through the resistor RL(1,2) still can be suppressed and filtered out by the load capacitor CL(1,2) in place of routed to the IF output. For simplicity, assuming that there is no RF current leakage through the load resistance RL(1,2), parasitic resistance Rds(1,2) and parasitic capacitance Cgs(3,4), the impedance at node VX(1,2) from (4) can be simplified and rewritten as Zin ≈ 1 . g m3 (6) As a result, the RF current delivered to node VY(1,2) through transistor M3,4 can be computed as i Y (1,2) ≈ ± v X (1,2) Zin ≈± g m (1,2) v RF sin ωRF t 2 . (7) From (7), the transistor M3,4 operates as a unity gain current buffer by delivering the same amount of RF current from node VX(1,2) to node VY(1,2). Since the impedance looking into transistor M5,6 at node VY(1,2) is also large, the RF signal is forced to enter the switching quad. The PMOS based LO switching transistors is adopted in substituting the conventional NMOS transistors as the LO power sensitivity in PMOS is lower than NMOS. In addition, PMOS transistor inherits a lower flicker noise performance compared to NMOS transistor. The total noise at the mixer output constitutes the thermal noise and flicker noise. Thermal noise is mainly contributed from transconductance stage which can reduced by increasing the bias current, while the flicker noise is dominated by LO switching transistor itself. The flicker noise is articulated by the LO switches via direct and indirect mechanism [5]. The flicker noise in effect through the direct mechanism is due to random modulation of the duty cycle of the LO switching current, whereas through the indirect mechanism is due to the LO current charging and discharging at the parasitic capacitance at switching tails. The output noise current generated by both mechanisms are given as below: i o,n = ( direct ) 4I LO,tail ⋅ Vn ST 2 ( Cp ωLO ) 2C p ⋅ Vn i o,n (indirect ) = ⋅ 2 2 T ( g m,LO ) + ( C p ωLO ) (8) (9) where ILO,tail is the DC tail current at the switching stage, S is the slope of LO signal, T is the LO period, Cp is the parasitic capacitance at switching tail, ωLO is frequency of LO signal, gm,LO is the tansconductance of the LO switching transistor and Vn is the equivalent flicker noise of the LO switching pair. In reference to the (8) and (9), both mechanisms are in proportional relation to the flicker noise voltage, Vn of the LO transistor which is expressed as Vn = 2K f Weff Leff Cox f (10) where Kf is the parameter of technology used, Weff and Leff is the effective width and length of LO switching transistor respectively, Cox is the oxide capacitance of LO switching transistor and f is the operating frequency. In the proposed subharmonic mixer design, the LO switching transistor is biased to operate in subthreshold region. Large switching transistor with low LO current is preferred to minimize the flicker noise via direct mechanism according to (8) and (10). However, when the LO switching transistor is increasing in aspect ratio, the noise contribution via indirect mechanism is become significant as the parasitic capacitance Cp increased. Therefore, an optimum LO switching transistor is chosen to minimize the noise contribution. The mixing point of RF and LO signals are located at the tail of switching stage which is at node VY1 and VY2, respectively. The differential IF output current can be expressed as i IF = ( i Y1 − i Y 2 ) ⋅ sq ( 2ωLO t ) v IF i IF R L 2 g m R L ⋅ sin ( ωRF − 2ωLO ) t . (13) = = v RF v RF π III. RC EXTRACTED RESULTS The proposed subharmonic mixer in Fig. 1 is designed, simulated and verified in 0.13 µm CMOS process. The layout parasitic extraction is executed and validated under SpectreRF and Calibre platforms. The post layout simulation results were carried out a total power consumption of 6 mW at a respective supply voltage of 1.2 V. Fig. 2 shows the simulated CG versus LO input power in a comparison plot with the presence of the complementary current-reuse technique and the absence of the complementary current-reuse technique. At 0 dBm of LO power, the simulated CG is indicated to be 11.26 dB without the complementary current-reuse in place and 15.18 dB with the integration of complementary current-reuse. This plot reveals and confirms that the complementary current-reuse technique had improved the CG by 4 dB without consuming additional power. With an LO input power of 0 dBm at 1.2 Fig. 2. Simulated results of conversion gain versus LO input power. Fig. 3. Simulated IIP3 with 100 kHz frequency spacing. 2 g m v RF sin ( ωRF − 2ωLO ) t − sin ( ωRF + 2ωLO ) t . (12) π At the IF output, since the DC bias current at the LO switching stage is designed to be low, the DC offset is reduced and substantially increases the switching efficiency. The low bias current allows the integration of larger load resistance, thus increasing the conversion gain. The load resistor, RL(1,2) couples with the load capacitor, CL(1,2) form a low pass filter which suppress the fundamental component of sin(ωLO)t, sin(ωRF)t leaking from the transconductance stage and other high-order 276 A= V (11) where sq(2ωLOt) is the square wave with double LO frequency. Considering only the desired intermodulation frequencies which is sin(ωRF ± 2ωLO)t and neglecting the feed components of sin(ωRF)t, sin(ωLO)t, and other unwanted spurs such as sin(ωRF ± ωLO)t, sin(ωRF ± 3ωLO)t, sin(ωRF ± 4ωLO)t along with other higher order terms, the differential IF output current can be simplified as below: = i IF mixing spurs such as sin(ωRF + 2ωLO)t. Ultimately, the overall voltage conversion gain of the proposed subharmonic mixer at the desired output spectrum is given by: Fig. 5. The performance summary of the proposed subharmonic mixer along with other recent reported works are given in Table 1. As can be seen, the proposed subharmonic mixer core consumes low power dissipation and smallest active chip area while achieving the highest CG. IV. CONCLUSION Fig. 4. Simulated noise figure of the proposed subharmonic mixer. IFP IFN In this work, a new circuit architecture of inductorless, low power, high conversion gain fully differential subharmonic mixer for 2.4 GHz application was successfully designed and verified in 0.13 µm standard CMOS process. The complementary current-reuse technique is implemented at the output stage to further boost the conversion gain without dissipating additional power. Post extraction simulation result reports a high CG of 15.18 dB, a NF of 16.33 dB at 1 MHz, a P1dB of −16.3 dBm and an IIP3 of −6.72 dBm. The proposed subharmonic mixer operates at a supply voltage of 1.2 V while consuming only 6 mW of power deemed as a favorable requirement for low power application. LO_0 LO_90 ACKNOWLEDGEMENT LO_180 LO_270 This research is supported by the UM HIR Grant UM.C/HIR/ MOHE/ENG/51 from Ministry of Higher Education Malaysia. Mixer Core RFP REFERENCES RFN Fig. 5. Physical layout of the proposed subharmonic mixer including RF ESD bonding pads. TABLE I SUMMARY OF TYPOGRAPHICAL SETTINGS Performance Parameter VDD (V) Power (mW) CG (dB) IIP3 (dBm) NF (dB) Core Size (mm2) Process (µm) This work 1.2 6 15.18 −6.72 16.33 0.116 0.13 [6] [7] [8] 1.2 7.2 4.5 0 11 0.13 2.5 12.5 10.5 −3.5 17.7 0.942 0.15 3 5.25 8.01 −6.5 5.96 1 0.25 [9] [10] 2.75 1.2 5 6.4 5.8 2.2 −2 −3 18 11.3 0.772 0.553 0.18 0.18 GHz, the P1dB of the design is observed to be at −16.3 dBm. The two-tone test with 100 kHz frequency offset in the linearity simulation results in an IIP3 of −6.72 dBm as illustrated in Fig. 3. Fig. 4 shows the simulated NF response across the RF frequency. The simulated NF of the proposed subharmonic mixer is 16.33 dB at 1 MHz. The physical layout of the proposed subharmonic mixer core consumes approximately 0.372 mm x 0.313 mm of chip area and 0.751 mm x 0.581 mm of chip area inclusive with the RF ESD pads as illustrated in 277 [1] A. Loke, and F. Ali, “Direct conversion radio for digital mobile phones-design issues, status and trends,” IEEE Trans. Microwave Tech., vol. 50, no. 11, pp. 2422-2435, Nov. 2002. [2] B. Razavi, “Design considerations for direct-conversion receivers,” IEEE Trans. Circuits Syst. II, vol. 44, no. 6, pp. 428435, June 1997. [3] C.-H. Chen, P.-Y. Chiang, and C. F. Jou, “A low voltage mixer with improved noise figure,” IEEE Microw. Wireless Compon. Lett, vol. 19, no. 2, pp. 92-94, Feb. 2009. [4] W.-K. Chong, H. Ramiah, G.-H. Tan, N. Vitee, and J. Kanesan, “Design of ultra-low voltage integrated CMOS based LNA and mixer for ZigBee application,” Int. J. Electron. Commun., vol. 68, no. 2, pp. 138-142, Feb. 2014. [5] H. Darabi and A. A. Abidi, “Noise in RF-CMOS mixers: A simple physical model,” IEEE J. Solid-State Circuits, vol. 35, no. 1, pp. 15-25, Jan. 2000. [6] H. C. Jen, S. C. Rose, and R. G. Meyer, “A 2.2 GHz sub-harmonic mixer for direct-conversion receivers in 0.13µm CMOS,” IEEE Int. Solid-State Circuits Symp. Dig., pp. 1840-1849, 2006. [7] B. G. Perumana, C.-H. Lee, J. Laskar, and S. Charkraborty, “A subharmonic CMOS mixer based on threshold voltage modulation,” IEEE MTT-S Int. Dig., pp. 33-36, 2005. [8] P. Upadhyaya, M. Rajashekharaiah, and D. Heo, “A 5.6 GHz CMOS doubly balanced sub-harmonic mixer for direct conversion zero IF receiver,” IEEE Workshop Microelectron. Electron. Devices Symp., pp. 129-130, 2004. [9] B. Jackson and C. Saavedra, “A CMOS Ku-band 4x subharmonic mixer,” IEEE J. Solid-State Circuits, vol. 43, no. 6, pp. 13511359, Jun. 2008. [10] R. M. Weng, J. C. Wang, S. Y. Li, and H. C. Wei, “A low power folded mixer using even harmonic technology,” IEEE Int. Workshop Radio-Freq. Integr. Technol. Symp., pp. 247-249, 2007.