MAP7101

advertisement

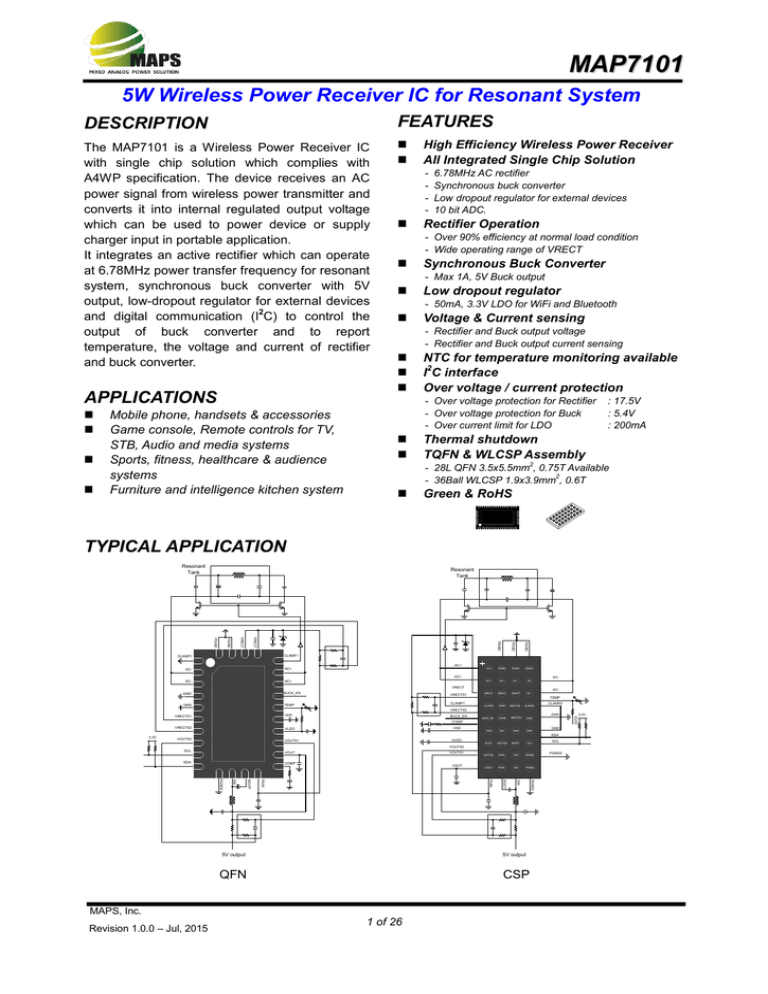

MAP7101 5W Wireless Power Receiver IC for Resonant System DESCRIPTION FEATURES The MAP7101 is a Wireless Power Receiver IC with single chip solution which complies with A4WP specification. The device receives an AC power signal from wireless power transmitter and converts it into internal regulated output voltage which can be used to power device or supply charger input in portable application. It integrates an active rectifier which can operate at 6.78MHz power transfer frequency for resonant system, synchronous buck converter with 5V output, low-dropout regulator for external devices 2 and digital communication (I C) to control the output of buck converter and to report temperature, the voltage and current of rectifier and buck converter. APPLICATIONS Mobile phone, handsets & accessories Game console, Remote controls for TV, STB, Audio and media systems Sports, fitness, healthcare & audience systems Furniture and intelligence kitchen system High Efficiency Wireless Power Receiver All Integrated Single Chip Solution - 6.78MHz AC rectifier Synchronous buck converter Low dropout regulator for external devices 10 bit ADC. Rectifier Operation - Over 90% efficiency at normal load condition - Wide operating range of VRECT Synchronous Buck Converter Low dropout regulator Voltage & Current sensing - Max 1A, 5V Buck output - 50mA, 3.3V LDO for WiFi and Bluetooth - Rectifier and Buck output voltage - Rectifier and Buck output current sensing NTC for temperature monitoring available 2 I C interface Over voltage / current protection - Over voltage protection for Rectifier - Over voltage protection for Buck - Over current limit for LDO : 17.5V : 5.4V : 200mA Thermal shutdown TQFN & WLCSP Assembly - 28L QFN 3.5x5.5mm2, 0.75T Available - 36Ball WLCSP 1.9x3.9mm2, 0.6T Green & RoHS TYPICAL APPLICATION Resonant Tank Resonant Tank PGND PGND PGND VRECT VRECT PGND PGND CLAMP1 CLAMP2 AC+ AC- AC+ AC- AC+ AC+ PGND PGND PGND AC+ AC+ AC- AC- AC+ AC- VRECT GND BUCK_EN VRECTS1 GND TEMP CLAMP1 VRECTS1 VDD BUCK_EN VRECTS2 VLDO ACVRECT VRECT VRECT CLAMP1 TEMP VRECTS1 BUCK_EN AC- TEMP CLAMP2 CLAMP2 VRECTS2 3.3V VDD VRECTS2 GND N/C SDA GND VLDO VOUTS2 BOOT SCL VOUTS1 PVIN SW PGND2 VOUT PVIN SW PGND2 GND VLDO COMP VDD COMP 3.3V GND SDA VOUTS2 VLDO VOUTS1 SCL VOUTS2 SCL VOUT SDA VOUTS1 COMP VOUT SW PGND2 PVIN BOOT BOOT PVIN SW PGND2 5V output PGND2 5V output QFN CSP MAPS, Inc. Revision 1.0.0 – Jul, 2015 1 of 26 MAPS MAP7101 ORDER INFORMATION ORDER CODE PKG MAP7101MP 28TQFN 3.5x5.5 PACKING Q’TY/CARRIER 5,000 Tape & Reel MAP7101WCP TEMPERATURE -40°C to 85 °C 36WLCSP 1.9x3.9 5,000 PIN DESCRIPTION PIN NO NAME DESCRIPTION QFN WLCSP GND 4,5 e4,f4 AC- 2,3 b3,b4,c4 VRECTS1 6 d3 Rectifier current sensing positive input for ADC. VRECTS2 7 e3 Rectifier current sensing negative input for ADC. VOUTS2 8 g2 Buck current sensing negative input for ADC. SCL 9 g4 I2C clock pin. SDA 10 f3 I2C data pin. PGND2 11 h4,i4 Buck converter power ground. Should be connected to GND. SW 12 h3,i3 Buck converter switching output. BOOT 13 g3 Analog and logic ground. Both of GND pin must be connected to ground. Negative (-) input of rectifier from receiver coil antenna. Bootstrap capacitor between SW to BOOT for high side buck switch drive. Connect a 47nF capacitor between this pin and SW. PVIN 14 h2,i2 COMP 15 e2 Buck converter power input. Connect a 2.2uF/50V capacitor between this pin and GND. Buck converter compensation. One capacitor and resistor are connected in series between ground and this pin for stable operation. VOUT 16 i1 Internal power supply input and buck converter feedback. Connect to the high side of the buck converter output capacitor. VOUTS1 17 h1 Buck current sensing positive input for ADC. VLDO 18 g1 3.3V LDO output. Connect a 1uF capacitor between this pin and GND VDD 19 f1 Output for internal circuitry. Connect a 1uF capacitor between this pin and GND. TEMP 20 d2 Temperature sensing pin with external NTC. BUCK_EN 21 e1 AC+ 22,23 a1,b1,b2 CLAMP1 24 d1 Buck enable pin. Connect this pin to HIGH to enable and LOW to disable buck convertor. Positive (+) input of rectifier from receiver coil antenna. Open-drain FET and the inverted output of CLAMP1 pin turns on the external clamping FETs. The unused CLAMP2 pin is connected to GND. CLAMP2 1 d4 Open-drain FET and the inverted output of CLAMP2 pin turns on the external clamping FETs. The unused CLAMP1 pin is connected to GND. VRECT 25,26 c1,c2,c3 Rectifier output. Connect 10uF between these pins and GND PGND 27,28 a2,a3,a4 Rectifier ground. Should be connected to GND EP (GND) PAD - Analog and digital ground, connect to board ground plane, GND, PGND and PGND2. MAPS, Inc. Revision 1.0.0 – Jul, 2015 2 of 26 MAPS MAP7101 PIN CONFIGURATION TOP VIEW (Bumps on bottom) CLAMP2 VRECT PGND VRECT PGND 1 1 2 3 4 a AC+ PGND PGND PGND b AC+ AC+ AC- AC- c VRECT VRECT VRECT AC- d CLAMP1 e BUCK_EN f VDD N/C SDA GND g VLDO VOUTS2 BOOT SCL h VOUTS1 PVIN SW PGND2 i VOUT PVIN SW PGND2 CLAMP1 AC- AC+ AC- AC+ BUCK_EN GND PAD (GND) GND VRECTS1 TEMP VRECTS1 CLAMP2 TEMP VDD VRECTS2 VLDO VOUTS2 COMP VRECTS2 GND VOUTS1 SCL VOUT SDA COMP BOOT PVIN SW PGND2 N/C : No Connection 2 2 28L QFN 3.5 x 5.5mm , 0.75T (typ) 36Ball WLCSP 1.9 x 3.9mm , 0.6T (typ) BLOCK DIAGRAM VRECTS1 VRECT VRECTS2 Bias UVLO TSD AVVOUT Synchronous Buck Controller Buck Enable HV 4V LDO SW1 CLAMP1 Power Control PGND2 VOUTS1 AVVRECT 6.78MHz AC Rectifier SW AVIOUT AC- BOOT VDD AVIRECT AC+ PVIN REN 5-to-1 MUX VOUTS2 BUCK_EN SDA I2C protocol 10bit ADC SCL VOUT CLAMP2 SW2 OVP control PGND COMP 3.3V LDO TEMP VLDO MAP7101 LDO Control VDD GND MAPS, Inc. Revision 1.0.0 – Jul, 2015 3 of 26 MAPS MAP7101 ABSOLUTE MAXIMUM RATINGS Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be not operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. TA =25°C unless otherwise specified. AC(+/-), CLAMP1/2, VRECT, VRECTS1/2, SW, PVIN .............................................................-0.3V to 20V BOOT ....................................................................................................................................... -0.3V to 25V VDD, SDA, SCL, COMP, TEMP, BUCK_EN, VOUTS1/2 ……………………..….………….…. -0.3V to 5.5V NOTE1) θJunction-to-Ambient – 28TQFN3.5x5.5 ............................................................................................ 48°C/W NOTE1) θJunction-to-Ambient – 36WLCSP1.9x3.9 ......................................................................................... 53°C/W Lead Soldering Temperature, 10second ........................................................................................ 260°C Maximum Junction Temperature ...................................................................................................... 150 °C Storage Temperature Range .................................................................................................. -65 to 150 °C NOTE1) Junction-to-ambient thermal resistane is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordane to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature TJMAX at a given ambient temperature TA RECOMMENDED OPERATING CONDITIONS PARAMETER SYMBOL VALUE UNIT AC(+/-), CLAMP1/2, VRECT, VRECTS1/2, SW, PVIN - 5.5 ~ 17.5 V BOOT - 22.5 V VDD, SDA, SCL, COMP, TEMP, VOUT1/2, BUCK_EN - 0 ~ 5.0 V TA -40 ~ 85 °C Ambient Temperature Range MAPS, Inc. Revision 1.0.0 – Jul, 2015 4 of 26 MAPS MAP7101 ELECTRICAL CHARACTERISTICS fRECT = 6.78MHz, VOUT = 5V, VRECT = 8V, TA = -40°C ~ 85°C, unless otherwise specified. PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT - 400 - mΩ - - 10 μA 4.5 6.78 7.5 MHz - 33 - mA Active Rectifier Clamping MOSFET on resistance RDTON Clamping MOSFET leakage current ILKDTSW Rectifier operating frequency range fRECT VDS = 20V Rectifier operating current IDDRECT Over-voltage protection trigger level VOVPR - 17.5 - V VOVPRHYS - 1.5 - V Over-voltage protection hysteresis VRECT = 8V, VOUT = 5V Bias Circuit V VDD rising threshold VDDUV+ 3.5 VDD falling threshold VDDUVH- - 3.1 - V Main power switch-on voltage VPSON - 4.0 - V Main power switch hysteresis VPSHYS - 0.5 - V - 0.7 - Ω - 4.0 - V - 20 - mV - 8 - mA Power selection switch on resistance RPSON VOUT = 5V, IOUT = 10mA, VDD and GND High voltage LDO voltage VHVLDO VOUT = 0V, CL = 1uF High voltage LDO Load Regulation VHVLR High voltage LDO short circuit current limit ILIMHV Thermal shutdown1 TSD - 160 - °C TSDHYS - 20 - °C 3.234 3.300 3.366 V - 10 - μA 150 200 - mA - 55 - mA - 550 - mV IL = 0 ~ 50mA, CL = 1uF - 7 - mV VDD = 4V, IL = 50mA, 100Hz - 60 - dB Thermal shutdown hysteresis 1 IL = 0 ~ 50mA, CL = 1uF VRECT = 8V, CL = 1uF VOUT = VDD = 0V LDO 3.3V LDO voltage VLDO Quiescent current for LDO1 IQLDO Over current limit IOCLDO Short circuit current limit ISCLDO LDO head room VHRLDO Load regulation VLR Power supply rejection ratio PSRR100 VDD = 4V, IL1 = 10mA CL = 1uF, TA = 25°C VDD = 4V, CL = 1uF, No load VDD = 4V, VOUT = 1V, CL = 1uF VDD = 4V, VOUT = 0V, CL = 1uF IL = 50mA, VRECT change, Output drop = 2% MAPS, Inc. Revision 1.0.0 – Jul, 2015 5 of 26 MAPS MAP7101 ELECTRICAL CHARACTERISTICS fRECT = 6.78MHz, VOUT = 5V, TA = -40°C ~ 85°C, unless otherwise specified. PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT Synchronous Buck converter BUCK_EN high-level input voltage VENH VDD = 5V 2.3 - - V BUCK_EN low-level input voltage VENL VDD = 5V - - 0.8 V BUCK_EN pull-down resistance REN VDD = 5V - 70 - kΩ Error amplifier trans-conductance GM - 140 - umho High side switch on resistance RONH - 180 - mΩ Low side switch on resistance RONL - 180 - mΩ High side switch leakage current ILKH - - 10 uA Low side switch leakage current ILKL - - 10 uA Output voltage accuracy VOUT 4.85 5.00 5.15 V - 10.0 - mA tSS -- 0.7 - ms Minimum on time tONMIM - 150 - ns Minimum off time tOFFMIM - 50 - ns Ilimit - 2.4 - A VOVPH - 5.4 - V VOVPBHYS - 0.2 - V VUVPBH - 5.9 - V VUVPBHYS - 1.4 - V fSW - 1.0 - MHz Clock Frequency1 fSCL 0 400 kHz Bus-Free Time between Stop and Start Condition1 tBUF 1.3 - us tHD-STA 0.6 - us tSU-STA 0.6 - us tSU-STO 4.0 - us tLOW 0.6 - us tHIGH 0.6 - us Data Hold Time1 tHD-DAT 10 - ns SDA, SCL logic low trigger level VILMAX VDD = 5V - - 0.8 V SDA, SCL logic high trigger level VIHMAX VDD = 5V 2.3 - - V RSDA VDD = 5V - 50 - ohm Operating current IDDBUCK VRECT = 20V TA = 25°C @ switching Synchronous Buck converter Soft start time Current limit VOUT over voltage protection rising VOUT over voltage protection hysteresis PVIN under voltage protection rising PVIN under voltage protection hysteresis Switching frequency 2 I C interface Hold Time After Start Condition1 Repeated Start Condition Setup Time 1 Stop Condition Setup Time1 1 Clock Low Period 1 Clock High Period SDA bi-directional resistance1 mode turn on MAPS, Inc. Revision 1.0.0 – Jul, 2015 6 of 26 MAPS MAP7101 ELECTRICAL CHARACTERISTICS fRECT = 6.78MHz, VOUT = 5V, TA = -40°C ~ 85°C, unless otherwise specified. PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT Voltage & Current Sensing parameters VRECT sensing gain1,2 AVVRECT - 1/20 - V/V VOUT sensing gain1,2 AVVOUT - 1/5.9 - V/V IRECT sensing gain 2 IOUT sensing gain2 VTEMP sensing gain 1,2 NOTE1) Design guaranteed, not 100% production test. NOTE2) Full Scale Input level of ADC is 1V. AVIRECT RS = 50mΩ - 13.9 - V/V AVIOUT RS = 50mΩ - 13.9 - V/V - 1 - V/V AVTEMP MAPS, Inc. Revision 1.0.0 – Jul, 2015 7 of 26 MAPS MAP7101 TYPICAL PERFORMANCE CHARACTERISTICS 250 3.3V LDO over current limit [mA] PVIN under voltage protection rising [V] 6.2 6.0 5.8 5.6 -40 -20 0 20 40 60 225 200 175 150 -40 80 -20 Temperature [Centigrade] 40 60 80 Fig 4. 3.3V LDO over current limit 1.8 18.5 Over voltage protection trigger level (high) [V] PVIN under voltage protection hysteresis [V] 20 Temperature [Centigrade] Fig 1. PVIN under voltage protection rising 1.6 1.4 1.2 1.0 -40 -20 0 20 40 60 18.0 17.5 17.0 16.5 -40 80 -20 Fig 2. PVIN under voltage protection hysteresis 20 40 60 80 Fig 5. Over voltage protection trigger level high 1.8 3.36 Over voltage protection hysteresis [V] 3.34 3.32 3.30 3.28 3.26 3.24 -40 0 Temperature [Centigrade] Temperature [Centigrade] 3.3V LDO voltage [V] 0 -20 0 20 40 60 1.6 1.4 1.2 -40 80 Temperature [Centigrade] -20 0 20 40 60 Temperature [Centigrade] Fig 3. 3.3V LDO voltage Fig 6. Over voltage protection hysteresis MAPS, Inc. Revision 1.0.0 – Jul, 2015 8 of 26 MAPS 80 MAP7101 TYPICAL PERFORMANCE CHARACTERISTICS 1.3 I2C/BUCK_EN logic low trigger level [V] Switching frequency [MHz] 1.08 1.04 1.00 0.96 0.92 -40 -20 0 20 40 60 1.2 1.1 1.0 0.9 0.8 -40 80 -20 Fig 7. Switching frequency 40 60 80 5.70 VOUT over voltage protection rising [V] Minimum on time [nS] 20 Fig 10. BUCK_EN logic low trigger level 250 200 150 100 -40 -20 0 20 40 60 5.55 5.40 5.25 5.10 -40 80 -20 0 20 40 60 80 Temperature [Centigrade] Temperature [Centigrade] Fig 11. VOUT over voltage protection rising Fig 8. Minimum on time 300 VOUT over voltage protection hysteresis [mV] 2.2 I2C/BUCK_EN logic high trigger level [V] 0 Temperature [Centigrade] Temperature [Centigrade] 2.1 2.0 1.9 1.8 -40 -20 0 20 40 60 250 200 150 100 50 -40 80 -20 0 20 40 60 Temperature [Centigrade] Temperature [Centigrade] Fig 12. VOUT over voltage protection hysteresis Fig 9. BUCK_EN logic high trigger level MAPS, Inc. Revision 1.0.0 – Jul, 2015 9 of 26 MAPS 80 MAP7101 TYPICAL PERFORMANCE CHARACTERISTICS (continued) Fig 13. Waveform of AC+ and AC- at no load Fig 16. Switching waveform at 3W load Fig 14. Waveform of AC+ and AC- at 3W load 17. 600mA instantaneous load step Fig 15. Switching waveform at no load Fig 18. Power On Sequence Fig MAPS, Inc. Revision 1.0.0 – Jul, 2015 10 of 26 MAPS MAP7101 Ploss 30mA 5V (1 ) [2] , where 5V is the buck output voltage and the last term is the efficiency of the Buck converter. If efficiency is 90%, Ploss is 15mW. VRECT CRECT Cs1 Lx AC+ Buck Converter HV 4V LDO 6.78MHz AC Rectifier Cp ACCs2 Power Control SW1 MAP7101 is a 6.78MHz magnetic resonance wireless power receiver IC which is applicable to A4WP PRU (Power Receiving Unit). According to the A4WP specification, a 6.78MHz AC signal is used to transmit power. Therefore, the active full-bridge rectifier of MAP7101 can handle 6.78MHz AC inputs. The rectifier and a passive capacitor make an unregulated DC voltage. DC level is dependent on the received signal strength by a resonant tank tuned at 6.78MHz. The rectifier output voltage is regulated to an accurate 5V by an internal synchronous buck converter. The convertor is possible to deliver current up to 1A at a given load. The IC serves a 3.3V LDO. It can be used for the power supply to the external device such as Bluetooth IC. MAP7101 provides parameters using 10bit ADC and internal amplifiers. It reports voltage/current of rectifier, voltage/current of buck output and temperature (to measure temperature of the system, an external thermistor is required). Users 2 can easily read the data using I C protocol. The maximum operation voltage of the IC must be limited to 20V. When the received energy from the resonant tank exceed VOVPR(Over-voltage protection trigger level), OVP circuit clamps receiving power with external devices or internal clamp MOSFETs. supplied by the Buck converter. The efficiency of the Buck converter is higher than the linear regulator, power loss of the IC reduces as: (1) Low efficiency current path General Description COUT VOUT SW2 (2) High efficiency current path VDD CVDD Fig. 13. Power flow: (1) high-voltage LDO path when Buck converter is off, and (2) SW2 turn-on when Buck converter is on. The 3.3V LDO itself has an ability to deliver about 100mA to the load. But, the temperature of chip could be increased because of low efficiency when high voltage LDO is used and buck converter turns off. Therefore, we strongly recommend that the Buck converter should be turned on when the LDO has to deliver lots of power to a load. Detailed Description Internal Power Scheme Power On Sequence Fig. 13 shows simplified power flow of MAP7101. All circuits of MAP7101 is powered by a resonant tank configured by Cs1, Cs2 and LX, where LX is antenna’s equivalent inductance. The received energy by the tank is rectified by a full-wave rectifier and an external capacitor, CRECT. Until 2 buck converter enable signal is detected by I C command or BUCK_EN pin, the buck does not operate. In this case, an internal high voltage LDO makes 4V of VDD to initiate operation of whole blocks. The operation current of IC reaches about 30mA when buck is turned off. Therefore, at this condition, power loss is Fig. 14 shows the power-on sequence. VAC+ Active Rectifier Operation Start VAC- VAC+/VACVRECT ~4V Active diode drop Passive diode drop 4V VDD(maximum Voltage tracking) VDD 3.5V VOUT HV LDO operation 3.3V HV LDO stop HV LDO operation VLDO VLDO(3.3V) BUCK_EN (or I2C control) 10bit ADC & I2 operation start Ploss 30mA (VRECT 4V ) . [1] Fig.14. Power-on Sequence. Assuming VRECT = 15V, power loss is 0.33W and power consumption is 0.12W. Thus the efficiency of LDO is only about 27%. When the Buck converter is enabled and VOUT becomes higher than 4V, then, SW1 and SW2 are forced to turn off and on, respectively. Thus, operation current is When AC power is detected by the resonant tank, the waveform of AC+ and AC- pins is shown in the Fig. 14 at the frequency of 6.78MHz. This input from resonant tank charges the rectifier output capacitor. When VRECT is about higher than MAPS, Inc. Revision 1.0.0 – Jul, 2015 11 of 26 MAPS MAP7101 4V, internal bias circuit starts operation and highvoltage LDO also is enabled. Thus, VDD voltage increases up to the target voltage of 4V. UVLO detector checks VDD is higher than 3.5V or not. If high, 3.3V LDO is enabled. Since LDO has softstart feature, VLDO slowly increases. When the VLDO reaches about 90% of 3.3V, 10bit A/D converter and I2C protocol circuit is activated. Thus, from that time, it is possible to 2 communicate with the chip through I C protocol. Even though most of circuits are booted, the Buck converter does not work until start command 2 comes from I C or BUCK_EN pin. If BUCK_EN signal is high and Vrect is over 6V(typ), the buck wakes up and builds VOUT softly. When VOUT > 4V, VDD voltage is changed to follow VOUT voltage and high voltage LDO ceases its operation to increase the efficiency of IC. In general, the capacitance of CRECT is much larger than that of Cp. Also, at 6.78MHz, the impedance of CRECT is too small. For example, if CRECT is 10uF, its impedance at 6.78MHz is about 2.3mOhm. Thus, Req and CRECT almost does not affect to the resonance frequency of tank. Finally the resonance frequency is achieved as f Cs Fig.15 shows the power conversion flow of magnetic resonant system. The resonant tank by Lx, Cs1 and Cs2 catches 6.78MHz wireless signal. Thus, the tank output is 6.78MHz AC signal. It is rectified by the rectifier of MAP7101 and becomes unregulated DC voltage. It is converted again to make accurate voltage by the Buck converter. Thus, AC current signal (IAC) flows via CS1, rectifier, CRECT and buck converter, rectifier again and CS2 as illustrated in Fig. 15. Cs1 Transition Period DC-DC conversion (Accurate DC; 5V) Cp Req Equivalent circuit during Transition period VAC+ Cp Higher Order Harmonic frequency VAC+ (or VAC-) @ smaller Cp IAC Rectifier Cs2 Energy Transfer to CRECT VRECT Cs2 VRECT A4WP antenna(Lx) Cs1 [4] Energy Transfer to CRECT Transition Period Lx MAP7101 2 1.11015 . (2f ) 2 LX LX Antenna voltage is dependent on the size of antenna and distance between a TX antenna. In some conditions, its peak can be several tens Voltage. Thus, we recommend Cs1 and Cs2 to meet the maximum operation voltage of 100V rate. Cp which is connected between VAC+ and VACactually does not affect the resonant frequency. But it affects transition characteristic. Power Conversion Flow Rectification (rough DC) [3] The equation [3] must be equal to 6.78MHz for the high efficiency. When you know the inductance of the antenna, Cs (=Cs1=Cs2) is determined as Resonant Tank Design 6.78MHz AC signal 1 . 2 LX (Cs1 || Cs 2) CRECT Buck converter VAC+ (or VAC-) @ larger Cp RL VAC- Fig. 17. Waveform of VAC+ or VAC- according to the size of Cp. Active Diode Fig. 15. Power Conversion Flow. Therefore, it is possible to simplify the circuit as depicted in Fig. 16 where Req is the equivalent resistance of the Buck converter. Cs1 Lx Cs2 CRECT+Cp ~ CRECT Req The larger Cp makes the longer transition period. It helps to decrease dv/dt stress on the devices in the rectifier. However, the period of energy transfer is reduced. Thus, the peak current of the rectifier increases and it also increases the conduction loss of rectifier. On the other hand, Cp is too small, higher-order harmonic waveforms can appear at VAC+ and VAC-. Thus, Cp must be properly selected by considering efficiency and stability of the rectifier. We recommend Cp satisfies below equation: Fig. 16. Equivalent circuit at power delivering sequence. MAPS, Inc. Revision 1.0.0 – Jul, 2015 12 of 26 MAPS MAP7101 3 1 2 LX (Cs1 || Cs 2) 2 LX (Cs1 || Cs 2 || Cp) . [4] 7 2 LX (Cs1 || Cs 2) From equation [4], reasonable Cp range is obtained as 0.006 Cs Cp 0.01 Cs . can increase the chip temperature. It is the major drawback of TYPE-I protection. To handle higher resonant current without increasing the chip temperature, TYPE-II shown in Fig. 19 is adequate. It requires high-voltage external MOSFETs. When these are turned on, the resonant frequency is changed as if we explained in the TYPE-I case. VRECT [5] Over-Voltage Clamp Cs1 Fig. 18 shows simplified over-voltage clamp circuit. When VRECT exceeds VOVPR, the comparator’s output in OVP controller becomes high and triggers two MOSFETS. The resonant current flows through Cs1, Ccl2, Ccl1 and Cs2. Consequently, the resonant frequency of the tank is changed as AC+ Lx 6.78MHz AC Rectifier Cp Cs2 Ccl1 AC- Ccl2 CLAMP1 OVP controller Driver f 1 . 2 LX (Cs1 || Cs 2 || Ccl1 || Ccl 2) [6] Fig. 19. Over-voltage clamp, TYPE-II. This frequency is higher than 6.78MHz. Therefore, the resonant tank is detuned from 6.78MHz and the power received by the antenna is decreased. From this operation, it is possible to clamp VRECT voltage not to be over VOVPR. When VRECT is lower than (VOVPR-VOVPRHYS), two MOSFETs are turned off and normal operation resumes. VRECT Cs1 AC+ Lx 6.78MHz AC Rectifier It requires a few hundred Voltage rate small size MOSFETs. f 1 . 2 LX (Ccl1 || Ccl 2) [7]. Current Sense & CRECT Selection Fig. 20 shows the rectifier current sense circuit. The rectifier produces 6.78MHz pulsating current from the resonant tank. It charges CRECT1 and CRECT2. Assume that Buck converter delivers 1A to the load. If the rectifier voltage is VRECT, the average input of the Buck converter is I AVG Cp Cs2 VOVPR Hyeteresis: VOVPRHYS High Voltage Discrete MOSFET AC- 1A 5V 5W . VRECT VRECT [8] If we allow the 100mV voltage drop of CRECT1, CRECT1 must meet following inequality: Ccl1 CLAMP1 Ccl2 CRECT 1 CLAMP2 OVP controller Driver 5W 100mV VRECT f BUCK , where fBUCK is the operation frequency of the converter. VOVPR Hyeteresis: VOVPRHYS Fig. 18. Over-voltage clamp, TYPE-I. We call this scheme as TYPE-I. The resonant current and the resistances of clamp MOSFETs For the stable operation, VRECT should be higher than 6V. Thus, VRECT=6V becomes worst case. Since fBUCK is 1MHz, the minimum CRECT1 is calculated as: MAPS, Inc. Revision 1.0.0 – Jul, 2015 [9] 13 of 26 MAPS MAP7101 CRECT 1 8F [10] Large CRECT2 is also helpful to reduce current and voltage ripples. But, when the Buck converter output is abruptly shorted to ground, large CRECT2 delivers too much charge to the Buck converter. Thus, high-side MOSFET of the Buck converter can be damaged. In the presented application circuit, CRECT1 and CRECT2 are chosen to 10uF and 2.2uF, respectively. CRECT1 and CRECT2 reduce current ripple. However, still the current draws through Rs has lots of current ripple. To measure the average rectifier current without aliasing due to high frequency noise, the current ripple must be rejected. In Fig. 20, RF and CF configure a lowpass filter. For RF=100 Ohm and CF=470nF, the cut-off frequency becomes 3.39kHz. Lower RF is recommended since larger RF can change the offset of the amplifier. IRECT Rectifier Ibuck Isense When R1 and R2 are selected as 12k and 5.1k respectively, temperature versus output voltage (TEMP) is characterized as Fig. 23. st 1 order linear approximation gives VTEMP 0.0073 Tc 0.9034 [12] , where Tc is temperature with a Celsius scale. This circuit is not perfectly linear but satisfies less o than +/- 5 C error in the temperature range of 0 o to 85 C. Buck converter Resonant tank CRECT1 Lx Rs(50m) CF Fig. 21. Resistance of thermistor vs. temperature o Refer to Murata web page [0 ~ 85 C]. CRECT2 RF Noise Filter 3.3V R1(12k) 14 TEMP R2(5.1k) Vsense=0.7*Isense Rth(thermistor) Fig. 20. Rectifier current sense circuit. Temperature Sense Fig. 22. Temperature sense circuit. To measure system temperature, an external thermistor is required. The resistance of that is inversely proportional to the temperature. In the design, MAPS used Murata’s thermistor, NCP15XH103E03RC. The chosen thermistor has following characteristic. 1 1 R Ro exp B T To [11] , where Ro=10k [Ohm], B=3434 [K] and To=300 [OK]. T is absolute thermistor temperature. As plotted in Fig. 21, the resistance of thermistor is quite non-linear over temperature. To compensate non-linearity, sensing circuit is configured as Fig. 22. R1 and 3.3V reference determines sensing voltage range. R2 compensates non-linearity. Fig. 23. Temperature vs. output voltage and 1 order linear approximation. MAPS, Inc. Revision 1.0.0 – Jul, 2015 14 of 26 MAPS st MAP7101 tuned from the test depending on application environment and purposes. For efficiency, trise,tfall of SW is very short. Because switching loss of buck converter is proportional to those values. Short trise,tfall means SW voltage changes very steeply. This may cause unintended effect on the buck converter operation depending on application environment like PCB patterns. To guarantee stable buck converter operation, external schottky diode (PMEG3020) or RC snubber should be connected as close as possible between SW and PGND in application. The recommended values for RC snubber, Rs and Cs are 10ohm and 100pF. Each values need to be tuned for application purposes. Fig. 24. Error of linear approximation. Buck Converter Basic Operation Load Clamp Function VRECT voltage varies widely depending on magnetic energy received and load conditions. Synchronous buck converter provides regulated 5.0V output from the rectifier output(VRECT). In some cases, the PRU is not positioned properly enough from PTU (Power Transmitting Unit) unintentionally or intentionally by user. At this condition the energy received by antenna and rectifier is not enough to supply load current through the buck converter. VRECT may collapse then it can cause repetitive fluctuation of VRECT and PVIN voltages. To prevent it, the buck converter limits load current and maintains PVIN voltage around 5.0V. To turn off the buck converter, BUCK_EN needs to be low and disable command is delivered by 2 I C. After then, an internal resister makes VOUT discharged to ground. Fig. 25 shows overall operation of the Buck converter. The buck converter operation is based on peak current mode control. The inductor current is sensed during high side switch on. Compensation ramp is generated internally to prevent sub-harmonic oscillation. Duty is determined by comparing the value summing sensed result and compensation ramp with command from COMP. Inductor Selection OSC Drv PWM dead time Control Logic EN Drv ZCD Cout The inductor stores energy during the high side switch-on time of buck convertor and transfers that energy to the output through the low side switch during high side switch-off time. It should have a sufficiently high saturation current rating and a DCR as low as possible. The peak-to-peak current ripple can be calculated by: Load BUCK_EN I2C CLK Soft Start Vref Rc discharge Cc ΔiLp p Fig. 25 Buck converter block diagram. The buck converter can be turned on by 2 BUCK_EN high or I C command. Once the buck converter is turned on, VOUT gradually ramps up by internal soft-start to prevent VRECT collapse by abrupt inrush current. Soft-start time is around 700us. For stable operation, proper values of each component should be used in compensation. The recommended values for Rc and Cc are 30kohm and 100pF. Actual Rc and Cc values should be VOUT VOUT (1 ) fs L VPVIN , where ΔiLp p is peak-to-peak ripple current, VOUT is the output voltage of Buck, VPVIN is the input voltage of Buck, fs is the switching frequency and L is inductance. In general, it is desirable to have lower inductance in switching power supplies, because it usually corresponds to faster transient response, smaller DCR, and reduced size for more compact designs. But too low of an inductance can generate too large of an inductor ripple current such that overcurrent protection at the full load could be falsely MAPS, Inc. Revision 1.0.0 – Jul, 2015 [13] 15 of 26 MAPS MAP7101 triggered. Make sure that the peak inductor current is less than the rated saturation current of the inductor. In addition, ensure that the maximum rated rms current is greater than the maximum dc input current to the regulator. The following inductors in Table 1 have been used with the MAP7101 and are recommended for use. XPL2010-222ML should be used below 2 watt like wearable application. Output Capacitor Selection The output capacitor maintains the output voltage and supplies current to the load. The value and characteristics of the output capacitor greatly affect the output voltage ripple and stability of the regulator. Use a low ESR output capacitor like ceramic dielectric capacitors are preferred. The output voltage ripple, ΔVOUT is a function of ΔiL and the ESR of COUT. It is calculated by: ΔVOUT ΔiL (ESR 1 ) 8 fs COUT To control the Buck converter and read out A/D 2 conversion results, I C protocol is used. Table 2 2 shows I C address map of MAP7101 and Fig 26 2 shows the I C interface timing diagram. 2 I C physical address of MAP7101 is fixed to 0b1010_010X (X=0 or 1). Thus write and read address of MAP7101 is 0xA4 and 0xA5, respectively. To know actual signal quantity from the A/D conversion data, you should use following equation: (1) Temperature o Tc[ C ]=123.8-137*DOUT0<9:0>/1023 (2) Rectifier voltage: VRECT=DOUT1<9:0>/(AVVRECT*1023) (3) Buck output voltage: VOUT=DOUT2<9:0>/(AVVOUT*1023) (4) Rectifier current: IRECT=DOUT3<9:0>/(50m*AVIRECT*1023) (5) Buck output current: IOUT=DOUT4<9:0>/(50m*AVIOUT*1023) [14] To keep the low resistance up to high frequencies and to get narrow capacitance variation with temperature, it's recommended to use X7R or X5R dielectric. The recommended value for the output capacitor is 22uF. Table 1. List of Inductors TYPE I2C communication When you read 0x0D address, you can get several information described in table 3. INDUCTANCE[H] CURRENT [A] MANUFACTURER LPS4018-222ML 2.2 H, 20% 2.8 Coilcraft LPS4012-222ML 2.2 H, 20% 2.4 Coilcraft XPL2010-222ML 2.2 H, 20% 1.2 Coilcraft Table. 2. I2C address map. Address Data 0x00 BUCK_EN 0x01 DOUT0<9:8> 0x02 DOUT0<7:0> 0x03 DOUT1<9:8> 0x04 DOUT1<7:0> 0x05 DOUT2<9:8> 0x06 DOUT2<7:0> 0x07 DOUT3<9:8> 0x08 DOUT3<7:0> 0x09 DOUT4<9:8> 0x0A DOUT4<7:0> 0x0D SSR<7:0> Bits 1 R/W R/W Description If High, Buck converter is turned on. 10 R Temperature sensing result 10 R Rectifier voltage sensing result. Gain = AVVRECT. 10 R Buck converter output voltage sensing result. Gain = AVVOUT 10 R Rectifier current sensing result. Gain = AVIRECT. 10 R Buck converter output current sensing result. Gain = AVIOUT 8 R Status Report MAPS, Inc. Revision 1.0.0 – Jul, 2015 16 of 26 MAPS MAP7101 Table. 3. Status Report Resistor Format Bits <5> <4> <3> <1> <0> Description Buck Output OVP Rectifier Output OVP Buck soft start End VRECT Status Buck Output Status SCL SDA Bit High VOUT > 5.5V CLAMP = L && VRECT > 18V Buck soft start finished VRECT > 6V VOUT > 4.5V Bit Low VOUT < 5.2V CLAMP = H && VRECT < 16V Buck is under soft start VRECT < 4.5V VOUT < 4.2V VIHMAX VILMAX VIHMAX VILMAX Fig. 26. I2C Interface Timing Diagram. Fig. 27 show how to enable Buck converter. To turn-on the Buck converter, you should make data address 0x00 be high. temperature sensed results in series. (1) BUCK_ENABLE=H S S Slave Write Ack Start Chip ID W Device address 0x00 A Data address selection 0x01 A S P Device address W Stop A 0x00 Data address selection A 0x00 A 0x01 A Sr Master Ack Read Chip ID R Data address selection A 0xXX Data of address: 0x01 A Master not Ack 0xXX A P Command Fig. 27. How to wake up Buck converter through I2C protocol. To read A/D conversion results, we recommend continuous data read operation. The protocol is summarized in Fig. 28 when you want to read Temperature data. A/D conversion data length is 10bit. Therefore, two addresses are designated for the data. For the case of temperature, 0x01 and 0x02 occupies temperature sensing results. If you follow Fig. 28 sequence, you can get 10bit P Data of address: 0x02 To achieve high efficiency, good regulation, and stability, a good PCB layout is required and critical for the high frequency operation. Therefore the PCB layout of MAP7101 demands careful design for good operation and performance. A poor layout can make issues like poor line transient, load transient, stability, EMI radiation and noise sensitivity. Use the following general guidelines when designing PCBs: Make all power (high current) traces as short, direct, and thick as possible: VRECT, PVIN, VOUT, VDD, VLDO. High frequency bypass capacitors need to be placed close to VRECT, PVIN, VOUT, VDD and VLDO. The inductor, input and output capacitors should be as close to each other as possible. This helps reduce the EMI radiated by the MAPS, Inc. Revision 1.0.0 – Jul, 2015 A Stop Layout Guidelines Command Slave Write Ack Chip ID W repeated Start Fig. 28. Continuous A/D conversion results readout. (2) BUCK_ENABLE=L Start Chip ID Device address Stop A Slave Write Ack Start 17 of 26 MAPS MAP7101 power traces that is due to the high switching current through them. The grounds of the IC should be connected close together, directly to a ground plane like exposed pad. The trace resistance of AC+, AC-, VRECT and VOUT should be as low as possible. The rectifier output capacitor must be placed as close as possible to the VRECT and PGND pin of the IC. This provides low resistive and inductive path. The ground of buck output capacitor should be placed as close as possible to the IC's PGND2 pin for avoiding additional coupled noise in traces. The sensing pins like VRECTS1, VRECTS2, VOUTS1, VOUTS2 and TEMP should be connected in the shortest way to each pins at the sensing parts for avoiding noise coupling. Make sure that these traces are not being interfered by the noisy and power traces. It means that the noisy traces should be routed away from these sensing traces. AC+, AC-, SW, BOOT are the main source of noise in the board. These traces should be isolated by using GND trace and do not interfere with the signal and sensing traces and it is usually preferred to have a ground copper area placed under these traces to provide additional shielding. The inductor should be placed close to the SW pin and connect directly to the output capacitor for minimizing the loop area between the SW pin, inductor, output capacitor and PGND2 pin. Exposed Thermal PAD must be soldered to the PCB for achieving appropriate power dissipation. This PAD is electrically connected to GND. In case of power and ground traces, use several via pads when routing between layers. The several thermal vias on the exposed pad are needed to provide a thermal path to the PCB to remove the heat generated by device power dissipation. WLCSP PCB Assembly WLCSP PCB assembly typically follows the process flow depicted below. WLCSP TnR Inspection Incoming WLCSP tape and reel (TnR) inspection should be performed to confirm die orientation in the tape, device PIN 1 identification, laser marking, device thickness and overall bumping quality. Solder Paste Common information needed for solder paste selection is: solder alloy recommendation, flux material and activity level, particle size, and metal content of the paste system. A commonly used solder paste in board assembly printing application is Type III solder particle and 89.5% metal content. Flux compositions are “no clean” or water-soluble. No-clean fluxes may be rosin based (RO), resin (RE), or free of rosins and resins, which are classified as organic (OR). Flux activity level may be low (L) or moderate (M). Water-soluble fluxes generally have organic (OR) composition and high (H) activity level, where cleaning is mandatory. Halide-free fluxes are preferred and designated by a 0, while 1 indicates the presence of halides. A flux with ROL0 classification means rosin based, low activity, and halide free. Common solder alloys for board assembly are SnAgCu, the most common for lead-free solder (~217-220°C liguidus temperature). After solder paste printing, optical inspection is recommended to ensure uniform solder paste coverage over the PCB pads. Component Placement Automated placement equipment with vision alignment systems is used for placing WLCSP onto PCB. The allowable package offset with respect to pad should be determined. Proper nozzle is critical for damage-free picking from tape and releasing on the PCB. Die placement pressure should be characterized. Generally, a 50% misalignment during placement of the component on the board is tolerable; as WLCSP tends to self-align during the reflow process. The placement machine nozzle z-height should have enough over-travel to allow the bumps to be submerged about 50μm (2mils) (or half of the solder paste height) to the printed paste to allow the self-centering of the package. This also prevents the package from moving during transit from the pick-and-place equipment to the reflow oven. The two most popular methods of package alignment are the package silhouette (“look-down camera”) and the ball-recognition system (“lookup camera”). In the package silhouette system, the vision system locates the package outline only. In the ball recognition system, the vision system locates the ball-array pattern and can also detect MAPS, Inc. Revision 1.0.0 – Jul, 2015 18 of 26 MAPS MAP7101 missing balls. Cleaning (Post-Soldering) Assembly Reflow Post component placement and before reflow, Xray inspection is recommended to ensure acceptable placement accuracy of WLCSP components. Solder Reflow The SnAgCu solder alloy melts at ~ 217°C. Reflow peak temperature at joint level should be 15 to 20°C higher than the melting temperature. MAPS WLCSP is qualified for 260°C reflow. A typical temperature/time profile for the lead-free (SnAgCu) solder and the corresponding critical reflow parameters based on JEDEC JTSD020D are show below. The actual profile for the individual application depends on many factors; such as the size of the package, complexity of the PCB assembly, oven type, solder paste type, temperature variation across the board, oven tolerance, and thermal couple tolerance. Reflow profile and critical parameters for lead-free (SnAgCu) solder: Ramp up 3°C/second maximum Preheating temperature (Tsmin to Tsmax) : 150C to 200°C Time in pre-heat (ts) : 60 to 120 seconds Liquidus temperature (TL) : 217°C Time above TL (tL) : 60 to 150 seconds Peak temperature TP ≤ 260°C Ramp-down rate : 6°C/second maximum Time 25°C to peak temperature : 480 seconds maximum Depending on the application, soldering flux activity, board surface finish used, and whether under fill will be applied; cleaning after solder reflow may be required. There are three typical methods for cleaning the assembly: 1) boiling liquid bath with or without ultrasonic agitation; 2) liquid bath plus vapor; and 3) aqueous spray cleaning (most commonly used in the PCBA industry when cleaning is required using watersoluble fluxes). Caution must be used when conducting ultrasonic cleaning because it may result in weakened solder joints, especially for the fine-pitch WLCSP. Typical liquid cleaning solutions are alcohol at 40°C or water-based cleaning solutions. An appropriate drying methodology must be used to ensure no water entrapment under the package. IPC/EIA J-STD-001 provides acceptance criteria for post soldering cleaning, particularly on the rosin flux residues, ionic residues, and other surface organic contamination. IPC-TM-650 provides the test methodology for these. Under Fill of WLCSP Unless clearly stated, MAPS WLCSP is tested without applying under fill materials. WLCSP reliability performances provided are all guaranteed without under fill. However, it is up to the end user to decide whether under fill is applied. It is generally accepted that under fill materials improve WLCSP reliability, as well as helping hold components when reflowed upside down. Upside-down Reflow Ramp-down rate should be below : 6°C/s to prevent incurring stresses on the package and to create finer solder grain structure, which may affect reliability. On the other hand, slow than 2°C/s ramp-down rate is prone to produce large Ag3Sn aggregations in high silver solder, which is not desired. Convection-type or combined convection-IR reflow may be used. A Nitrogenpurge environment is preferable to improve solder wetting. Normally, the oxygen level should be less than 1000ppm. If WLCSP is reflowed on the bottom side, it is important to know if there is enough surface tension on the solder joints to hold the package. If analysis determines that the package would drop, the application and curing methodology of an appropriate adhesive should be provided. The need for adhesive can be estimated using the following calculation. Actual weight of the component ≤ Allowable weight Allowable weight = Total solder contact surface area of WLCSP in mm2 × die thickness Inspection Visual and X-ray inspection is recommended after solder reflow for solder joint size and shape irregularities. Well-reflowed solder joints show evidence of good wetting of copper pads with uniform solder surface appearance. Dull or grainy solder surface is not uncommon for lead-free solder. These solder joints are acceptable. Rework WLCSP components removed during PCB rework should not be reused for final assemblies. A WLCSP that has been attached to a PCB and then removed has seen 2~3 solder reflows, depending on whether the PCB is double sided. This is at or near the end of the tested and MAPS, Inc. Revision 1.0.0 – Jul, 2015 19 of 26 MAPS MAP7101 qualified three-solder-reflow survivability for MAPS WLCSP. The removed WLCSP components should be properly disposed of so that they do not mix with fresh WLCSP components. WLCSP component removal and replacement procedures should be established and qualified. A reference rework process follows this flow: The floor life of moisture-sensitive components starts from the time the moisture barrier bag is opened and the mounted component(s) is exposed to ambient conditions. The floor life of the component should be not have been exceeded before rework. Baking may be required in case this has been exceeded. Pre-heating of the whole PCB assembly before localized heating of the component for rework. Pre-heating reduces the overall heating time and prevents potential substrate warping when localized heating is applied on the region for rework. Typical pre-heating temperature is around 100°C. Localized heating on the region for rework is recommended to minimize heat exposure to the surrounding components. A hot air gun equipped with a thermocouple site is preferred. Once the solder interconnect reaches the specified reflow temperature, a vacuum pick-up tool is used to remove the component from the board. Cleaning of the board land pads: residue solder is removed using a soldering iron and a braided solder wicking materials. A vacuum-desoldering tool can also be used to extract the solder by continuous vacuum aspiration of the solder. After removing the residue solder, leftover flux must also be removed. Solder paste or flux printing: solder paste is usually deposited using a miniature stencil and squeegee. Where space is limited, flux is deposited on the solder pads. Component placement on the boardreplacing WLCSP components can be placed onto the board using automatic placement equipment. Solder or reflow- this can be selectively soldering the component using the same tools for removing the component or by passing the whole board to the original reflow profile. MAPS, Inc. Revision 1.0.0 – Jul, 2015 20 of 26 MAPS MAP7101 REFERENCE SCHEMATIC Fig. 29. MAP7101MP Reference Schematic REFERENCE COMPONENT Table. 4. MAP7101MP Reference Bill of Materials, Based on A4WP category 3 coil MAPS, Inc. Revision 1.0.0 – Jul, 2015 21 of 26 MAPS MAP7101 REFERENCE SCHEMATIC Fig. 30. MAP7101WCP Reference Schematic REFERENCE COMPONENT Table. 5. MAP7101WCP Reference Bill of Materials, Based on A4WP category 3 coil MAPS, Inc. Revision 1.0.0 – Jul, 2015 22 of 26 MAPS MAP7101 PACKAGE INFORMATION 28-TQFN (3.5mmx5.5mm) Unit : mm MAPS, Inc. Revision 1.0.0 – Jul, 2015 23 of 26 MAPS MAP7101 PACKAGE INFORMATION 36Ball-WLCSP (1.9mmx3.9mm) Unit : um MAPS, Inc. Revision 1.0.0 – Jul, 2015 24 of 26 MAPS MAP7101 PACKING INFORMATION 28-TQFN (3.5mmx5.5mm) PACKAGE 28TQFN 3.5x5.5 Units per Reel 5,000 Reel/Hub size 13/4 inch Trailer (min) Leader (min) 300mm 500mm Pocket Tape Width Pitch 12mm 8mm User direction of feed MAPS, Inc. Revision 1.0.0 – Jul, 2015 25 of 26 MAPS MAP7101 PACKING INFORMATION 36Bump WLCSP (1.9mmx3.9mm) PACKAGE 36WLCSP 1.9x3.9 Units per Reel Trailer (min) Leader (min) 300mm 500mm Reel/Hub size 5,000 13/4 inch Pocket Tape Width Pitch 12mm 4mm M133203 442DN M133203 442DN M133203 442DN M133203 442DN M133203 442DN M133203 442DN M133203 442DN M133203 442DN User direction of feed MAPS Inc. reserves the right to change the product specifications without notice at any time. The readers are responsible to verify that the data sheets are current before using the products. Information furnished by MAPS Inc. is believed to be accurate and reliable. However, no responsibility is assumed by MAPS Inc. No responsibility is assumed by MAPS Inc. either for any infringements of patents or other rights of third parties which may result from its use. MAPS, Inc. Revision 1.0.0 – Jul, 2015 26 of 26 MAPS