A wideband current-commutating passive mixer for multi

advertisement

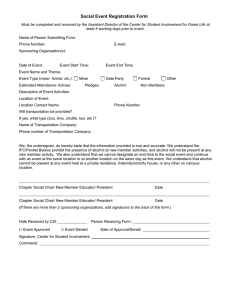

Vol. 34, No. 1 Journal of Semiconductors January 2013 A wideband current-commutating passive mixer for multi-standard receivers in a 0.18 m CMOS Bao Kuan(包宽), Fan Xiangning(樊祥宁) , Li Wei(李伟), and Wang Zhigong(王志功) Institute of RF-&OE-ICs, School of Information Science and Engineering, Southeast University, Nanjing 210096, China Abstract: This paper reports a wideband passive mixer for direct conversion multi-standard receivers. A brief comparison between current-commutating passive mixers and active mixers is presented. The effect of source and load impedance on the linearity of a mixer is analyzed. Specially, the impact of the input impedance of the transimpedance amplifier (TIA), which acts as the load impedance of a mixer, is investigated in detail. The analysis is verified by a passive mixer implemented with 0.18 m CMOS technology. The circuit is inductorless and can operate over a broad frequency range. On wafer measurements show that, with radio frequency (RF) ranges from 700 MHz to 2.3 GHz, the mixer achieves 21 dB of conversion voltage gain with a –1 dB intermediate frequency (IF) bandwidth of 10 MHz. The measured IIP3 is 9 dBm and the measured double-sideband noise figure (NF) is 10.6 dB at 10 MHz output. The chip occupies an area of 0.19 mm2 and drains a current of 5.5 mA from a 1.8 V supply. Key words: CMOS; current-commutating passive mixer; linearity; source and load impedance; multi-standard receiver; wideband DOI: 10.1088/1674-4926/34/1/015003 EEACC: 2570 1. Introduction The emerging various wireless communication systems promote the necessity to design a single transceiver that is compatible with multiple standardsŒ1 . Different kinds of software defined radio (SDR) receivers are proposed for applications like 3GPP-LTE, WCDMA, GPS, WLAN, and so onŒ2; 3 . One key challenge in bringing out a multi-standard multimode front-end lies in fulfilling the high level of integration and flexibility for reconfiguration. The direct-conversion (or zero IF) transceiver has attracted widespread attention recently for its simple design and easy integration with the baseband circuit, as well as for its low power consumption and potentially low manufacturing costsŒ4 . Nevertheless, direct conversion designs have many problems including the flicker noise, dc offset, and second-order intermodulationŒ5 . Those issues become more troublesome when implemented in super-scaled CMOS technology, especially the flicker noise problemŒ6; 7 . As a result, it is necessary to design a mixer free of those obstacles. An active mixer has intrinsic flicker noise problems due to its nonzero dc currentŒ8 , and the linearity of an active mixer cannot be very good due to its vertical structure and critical voltage headroom problemŒ9 . In fact, current-commutating passive mixers have recently become a preferred choice in the literature for wireless receivers thanks to their superior noise performance (especially 1/f noise) and their ability to linearly handle large unfiltered blockersŒ2; 4; 6 . Several direct conversion receivers have been published in which a current-commutating passive mixer is employedŒ10 12 . This paper gives a brief analysis on the advantages and disadvantages of current-commutating passive mixers compared to their active competitors. The effect of source and load impedance on the linearity of a passive mixer is analyzed with special focus on the impact of the input impedance of the transimpedance amplifier (TIA), which acts as the load impedance of the mixer. Afterwards, a wideband CMOS mixer based on a passive current-commutating structure is designed for multistandard applications including GSM, WCDMA, GPS, and Beidou. Complementary folded inputs are employed to achieve a higher transconductance efficiency. No inductor has been utilized in order to realize a wideband mixer. Without a high impedance node, the mixer can achieve pretty high linearity without using additional techniques like IM3 cancellation or other distortion calibration techniquesŒ13; 14 . 2. Comparisons between current-commutating passive mixers and active Gilbert mixers Active Gilbert mixers have been commonly used due to their good isolation between local oscillator (LO) and IF output, moderate gain, and moderate linearity performance. Recently, passive mixers have attracted more attention due to their flexibility in direct conversion receivers. This section gives a brief comparison between a typical current-commutating passive mixer and a typical active Gilbert mixer which are illustrated in Figs. 1(a) and 1(b) respectively. The comparisons are carried out in aspects of gain, linearity, and noise performance. * Project supported by the National Science and Technology Major Project (No. 2010ZX03007-002-01) and the State Key Development Program for Basic Research of China (No. 2010CB327404). Corresponding author. Email: xnfan@seu.edu.cn c 2013 Chinese Institute of Electronics Received 19 June 2012, revised manuscript received 25 July 2012 015003-1 J. Semicond. 2013, 34(1) Bao Kuan et al. Fig. 1. (a) A current-commutating passive mixer. (b) A conventional Gilbert active mixer. 2.1. Voltage conversion gain Firstly, the active mixer depicted in Fig. 1(b) is taken into consideration. The voltage conversion gain (VCG) of the active mixer isŒ5 2 VCG D gm RL ; (1) where gm is the transconductance of the transconductor stage composed by M1 and M2, RL is the load resistance, and coefficient 2/ is caused by the commutation behavior of the switches stage. Since DC current flows vertically through RL , switches and transconductor transistors, a tradeoff inevitably exits between voltage conversion gain and voltage headroom. For example, we can increase RL to achieve a higher VCG. However, the increased voltage drop on RL may force the transistors of the switches stage or transconductor stage out of saturation state. That is the reason why we can only have moderate gain, typically 5 to 10 dB. On the other hand, a passive mixer is accounted as no gain but only lossŒ5 . A passive mixer with only four switches and transistors definitely cannot provide any gain at all. Nonetheless, we can use a TIA to terminate the mixer in order to amplify the commutating current as shown in Fig. 1(a)Œ15 . The TIA converts the commutated current into voltage, and thus a considerable gain is generated due to the high gain of the TIA. In a current-commutating passive mixer, the voltage conversion gain has more degrees of freedom thanks to the independent dc current flowing through each stage. The transconductor stage, switch stage, and TIA stage in the mixer can be designed independently. So it is flexible to realize a high-gain passive mixer without lowering its linearity. Moreover, this advantage also makes it convenient to realize gain reconfigurability for multi-standard receivers which need programmable gains. It also partly explains why the current commutating passive mixer is preferred in software defined radio (SDR) receiversŒ2; 16; 17 . 2.2. Linearity The vertical design of the active mixer degrades its linearity performance especially where the fast-lowering supply voltage for super-scaled CMOS technology is concerned. Many techniques like IM3 cancellationŒ14 or distortion calibrationŒ18 are brought out to improve its linearity performance. Fig. 2. Illustration of the source and load of a passive mixer. But those techniques inevitably complicate its design procedure and may have some other penalty in aspect of gain or noise figure. In a current-commutating passive mixer, switch transistors only carry a signal current with negligible voltage swings showing inside the mixer, which results in significantly better linearity. Actually, the switch transistors are embedded between a current source input and an output buffer with zero input resistance. In the real situation, a transconductor acts as a current source, and a transimpedance amplifier can terminate the mixer in a low resistance as shown in Fig. 2. So the signals only operate in current mode, and the small voltage swings before and after the switches guarantee its intrinsic high linearity. The 2nd-order inter-modulation (IM2) is a critical challenge when designing direct conversion receivers. The achievable 2nd-order input intercept point (IIP2) has a fundamental dependence on nonlinearity and mismatches in the switching stage and improves with technology scalingŒ19 . In an active mixer, the 2nd-order intermodulation products generated by the input transconductor or due to self-mixing usually determine the IIP2. The parasitic capacitance loading the switchingstage common source plays a key role in the intermodulation mechanisms, and this parasitic capacitance can be cancelled by applying an inductor between themŒ20 . Fortunately, in a current commutating current mixer, ac coupling can be used to pass RF signals while suppressing the low frequency IM2 component generated by the transconductor stage, which provides a great benefit to IIP2Œ21 . 015003-2 J. Semicond. 2013, 34(1) Bao Kuan et al. Fig. 4. Simplified schematic of a commutating-current passive mixer. Fig. 3. Illustration of TIA noise amplification issues. 3. Linearity analysis of the current-commutating passive mixer 2.3. Noise The flicker noise (1/f / of an active mixer, which is proportional to its dc current, can corrupt the integrated noise significantly. Fortunately, passive mixers will not introduce significant flicker noise since there is no dc current following through the switches. However, a current output passive mixer has TIA noise amplification issuesŒ7 as illustrated in Fig. 3. The equivalent mixer output resistance, which can be expressed as a switched-capacitor resistance, is given asŒ21 : Req D 1 : Cp fLO (2) An equivalent circuit illustrated in Fig. 3 can be seen as a simple proportional operational amplifier. The input noise is amplified by a ratio related to ZL and Req . Consequently, the output noise contributed from the TIA can be derived as: 4ZL 2 2 2 ; D 1C vn; eq D 1 C 4ZL fLO Cp vn; eq Req (3) where ZL is the parallel of RL and CL . The noise amplification problem can be overcome by increasing the equivalent output impedance of the mixer Req Œ21 . The equivalent output impedance Req of the mixer is dominated by the switched-capacitor resistance Cp operating at LO frequency. The switched-capacitor resistance is inversely proportional to the operating frequency and the switched-capacitor value. A large portion of Cp is the parasitic capacitance from the transconductor output stage. Therefore, the mixer output impedance can be increased if the capacitance associated with transconductor output can be removed. The noise contribution from the TIA stage can be more than 50%. So it is of significant sense to minimize it. What’s interesting is that this switched-capacitor effect is very small in active mixers. That’s because the switch transistors remain in the saturation region during the whole LO period. The large output impedance of the switch transistors operating in the saturation region then connects in series with the switched-capacitor resistance Req , so the noise gain of the baseband amplifier remains small. 2 vn; TIA; out The above analysis give us an intuition that a commutating-current passive mixer is inherently highly linear thanks to the fact that there is no high impedance node in the mixer. The switches and transistors only carry current signals. In addition, the current signals are terminated by a TIA with very low input impedance which minimizes the signal loss. However, in a real situation, the output impedance of the transconductor is not sufficiently high, and the input impedance of the TIA is not sufficiently lowŒ22 . Thus signal loss and linearity degradation cannot be avoided. In this section the effect of the source and load impedance on the mixer will be analyzed in detail. 3.1. Effect of source impedance on mixer linearity As depicted in Fig. 4, the transconductor stage is modeled by an ideal current source irf with a frequency dependent source impedance ZS .!/. The TIA stage is modeled as the load impedance of mixer ZL .!/. Considering the impact of ZS .!/ and ZL .!/, the closed-form expressions for IIP2 and IIP3 for a current commutating passive mixer have been derived using a Volterra-series analysis in Ref. [22]. The relationship between the impedance of source and load and the linearity of the mixer is expressed as Eqs. (4) and (5): IIP2 Ka ZL .!1 /ZS .!1 !2 / 1 ZL .!1 !2 / f ŒZL .!LO 2 !1 / ; (4) ZL .!LO !1 /ZS .2!1 !2 / 1 ZL Œ!LO .2!1 !2 / gŒZL .!LO ; !1 / (5) where !1 and !2 represent the RF frequencies of two near input tones, and !LO represents the LO frequency. Equation (4) suggests that a quite large ZS (!1 !2 / is desired for a good IIP2. In order to have a high ZS (!1 !2 /, it is crucial to decrease the parasitic capacitance at the transconductor–switches interface. Parasitic capacitance can be easily tuned out by an inductor for all the possible operating frequencies in narrow band designs. However, in wideband designs inductors cannot be used in that fashion because the input frequency is so IIP3 Kb 015003-3 J. Semicond. 2013, 34(1) Bao Kuan et al. transimpedance of the TIA are derived as: Zin; TIA .j!/ D D vin iin Zf .j!/ C Zout .j!/ ; (6) 1 C A.j!/ C j!Cgs ŒZf .j!/ C Zout .j!/ vout Zout .j!/ Zf .j!/A.j!/ D ; vin 1 C A.j!/ C j!Cgs ŒZf .j!/ C Zout .j!/ (7) where Zf and Zout are: ZTIA .j!/ D Fig. 5. Equivalent small signal circuit for the analysis of the TIA’s input impedance. wide. DC coupling of current from transconductor to switches can be used to minimize the parasitic capacitance in the output node of the transconductor stageŒ15 . However, the absence of DC-blocking capacitors results in a non-zero DC bias current flowing through the switches. This amount of current should be minimized in order to reduce the 1/f noise contributions from the switches. The other method is that we apply an ac coupling capacitor CC between the transconductor stage and the switches stage, which will boost the mixer source impedance at !1 !2 , while passing the RF signal. Actually, CC here eliminates IM2 dramatically and consequently improves the IIP2 of the mixer. Similarly, Equation (5) reflects that, to improve IIP3, the source impedance at the RF signal frequency (2!1 !2 / should be as high as possible. Frequencies !1 and !2 shown in Eqs. (4) and (5) are two closely spaced radio frequencies. Consequently, !1 !2 is near DC, and 2!1 !2 is a pretty high frequency. High IIP3 and IIP2 both require a large source impedance at low and high frequencies. So it is essential to make the output resistance of the transconductor as large as possible and also the parasitic capacitance at this node as small as possible. It causes a tradeoff when choosing the size of the transistors because a large resistance needs a longer channel length while small parasitic capacitance prefers transistors with a small size. 3.2. Effect of the TIA’s input impedance on the linearity of passive mixers In a real current commutating passive mixer, the input impedance of the TIA acts as the load impedance of the mixer, i.e. ZL (!) as illustrated in Fig. 4. A very low ZL (!) is desired to avoid a big voltage swing at the input of the TIA. We also expect that the commutated signal current will be completely fed to the TIA. However, the input impedance of the TIA is not always as low as expected and signal loss due to the nonzero input impedance of TIA is inevitable. The mechanism of non ideality of input impedance of the TIA is illustrated in Fig. 5. In Fig. 5, Cgs , Gm , Rout , and Cout stand for the input capacitance, transconductance, output resistance and output capacitance of a typical OTA, respectively. The input impedance and Zf .j!/ D RF == 1 ; j!Cgs Zout .j!/ D Rout == 1 ; j!Cout (8) (9) and A(j!) is the open loop gain of the OTA. At a relatively high intermediate frequency, the finite OTA gain-bandwidth will cause a significant open loop gain decrease. The denominator of Eq. (6) will decrease due to the dropped A(j!). As a result, Zin; TIA will get bigger. A bigger Zin; TIA is not desired because it will cause a large voltage swing at the TIA input, and introduces nonlinearity from both the mixer and the TIA. With a second glance to Eq. (6), we found the numerator of Eq. (6) will also decrease due to the decreasing Zf , which is a parallel combination of RF and CF . The decreasing Zf can partly cancel the effect of decreasing A(j!) and give a compensation for Zin; TIA . Simulation results of Zin; TIA and ZTIA with different Zf are illustrated in Fig. 6. Simulation is based on a typical two stages miller compensated OTA with a unit gain bandwidth of 350 MHz and RF of 2 k. The Cf ranges from 0 to 8 pF. It’s clearly seen from Fig. 6(a) that CF has a dramatic compensation effect for the input impedance of the TIA. Let’s check it at 300 MHz, the Zin; TIA with 0 pF CF is 1.8 k, while less than 100 with 8 pF CF . This phenomenon provides us a way to decrease Zin; TIA with a moderate area-consuming penalty. Additionally, the transimpedance characteristic is also affected by the changing CF as shown in Fig. 6(b). The –3 dB bandwidth decreases with increasing CF , which has a great impact on the IF bandwidth of the mixer. So a careful tradeoff needs to be considered to achieve a relatively low Zin; TIA while maintaining a good gain bandwidth for the mixer. Considering a multi-standard receiver compatible with the WCDMA standard, the baseband bandwidth is 3.84 MHz, whereas the strongest jammer, due to TX leakage, is down converted to 135 MHz. If the TIA input impedance is very large at 135 MHz, the linearity performance will be poor due to a big voltage swing at the input of the TIA. As suggested by Eqs. (4) and (5), the TIA input impedance, which acts as the load impedance of the switches, contributes to IIP2 and IIP3, making the high load impedance at the down converted jammer frequency the single most dominant factor in degrading the passive mixer linearity. Hence, instead of placing an interstage RF filter, it’s worthy to figure out a way to decrease the load impedance of the switches. 015003-4 J. Semicond. 2013, 34(1) Bao Kuan et al. Fig. 6. (a) Input impedance and (b) transimpedance of the TIA versus frequency with different CF . Consequently, it’s very necessary to bias the 4 transconductor transistors in the deep saturation region to guarantee the large resistance of the channel. What’s more, the sizes of M1–M4 need to be careful optimized to achieve a proper gm and an acceptable parasitic capacitance Cdd . In the presented circuits, the bias of the PMOS transistors is generated by a common feedback circuit which can also stabilize the output common voltage level. 4.2. Switches stage Fig. 7. Transconductor stage for the passive mixer. 4. Circuit design Motivated by the comparison between active mixers and current-commutating passive mixers, this section describes the design considerations of the presented circuits with an emphasis on tradeoff among linearity, noise, gain, and power consumption. Moreover, the effect of source and load impedance of the core mixer will be kept in mind when designing the circuits. In this section, we will focus on the implementation of mixer’s main building blockers including the transconductor stage, switches stage, and TIA stage. 4.1. Transconductor stage As shown in Fig. 7, a fully differential current reused transconductor is employed to convert the input RF voltage signal to RF current. Then, the current signal is fed to the doublebalanced passive current commutating mixer. As analyzed in Section 3, the transconductor stage acts as a current source in front of the switches. A large output impedance ZS (j!) is desired to minimize the signal loss and enhance its linearity performance according to Eqs. (4) and (5). Considering the real implementation of this circuit, the channel resistance rds1 4 and the parasitic capacitance at the drain of transistors M1–M4 constitute the output impedance of the transconductor stage. Figure 8(a) illustrates the schematic of the double balanced switches stage. The RF transistors implemented in the deep Nwell are used as switches due to their attractive high frequency performance. Triple-well process, as shown in Fig. 8(b), makes it convenient to bias the body at the same voltage level as the sourceŒ5; 21 . The buried deep N-well provides good isolation between the substrate and the active area of transistors and the bias of its body is not limited to ground any more. Indeed, connecting the body and source reduces the body effect, and also can reduce the dc bias voltage as well. However, on the other hand, the inside P-substrate and the buried deep N-well form a reverse-biased diode which has quite a big parasitic junction capacitance CJ due to the large area in touch. This big parasitic capacitor will be connected into the signal path if the body and source of the transistor are directly connected together, which will dramatically impact the high frequency performance of the switches stage. So, the body of switches and transistors in the presented mixer is simply connected to the ground. Although the threshold voltage of the transistors gets bigger, the junction capacitor CJ has no impact on the switching signal path. 4.3. TIA stage The TIA stage serves as the load, current to voltage converter and anti-aliasing filter for the mixer. The active-RC TIA stage will provide very low impedance at the mixer output, so that nearly all the signal current that comes from the mixer core follows into the feedback RC. A two stage miller compensated OTA topology is chosen for the TIA design as shown in Fig. 9. This structure can obtain both a high output voltage swing and low input-referred noise. Considering the noise am- 015003-5 J. Semicond. 2013, 34(1) Bao Kuan et al. Fig. 8. (a) Switches stage of the passive mixer. (b) Cross picture of the deep N-well transistors. Fig. 9. (a) Structure of the TIA. (b) Two-stage OTA used in the TIA. plification effect as discussed in Section 2, noise contribution from TIA nearly dominates the noise performance of the mixer, especially the 1/f noise. It is essential to minimize noise generated from the TIA stage. The input-referred noise density of the OTA is derived asŒ15 : gmN gmP C f ˛N ˛P 2 2 KN KP gmP C C ; 2 f Cox .W L/N .W L/P gmN Vn;2 OTA D 8kT (10) where KP and KN are process-dependent constants, ˛ is the ratio gm /gds0 , and Cox is the gate oxide capacitance per unit area. In order to reduce the OTA noise contribution, the input nMOS transistors are sized to have a high W=L ratio with a along channel length, while the pMOS has a low W =L ratio with a long channel length. The output stage of the amplifier is simply a common-source amplifier and provides an almost rail–rail output swing. The voltage conversion gain of the mixer is VCG D gm ZF /2, where ZF is the feedback impedance CL parallel with RL as shown in Fig. 9(a). So the low frequency VCG of the mixer is determined by gm and RL . The voltage conversion gain has more degrees of freedom thanks to the independent dc current flowing through each stage as discussed in Section 2. So, it is flexible to realize a high-gain passive mixer without lowering its linearity, which is a big advantage compared to active mixers. In this design, we use a RF of 2 k to provide about a 20 dB gain. However, conventional active mixers usually cannot use a load resistance as large as several kilo ohms, because of critical voltage headroom problems. The feedback capacitors CF are chosen with the consideration of both minimizing the input impedance of the TIA at high frequency and the area consumption of the circuits. Although using large feedback capacitors creates a low-frequency gain rolloff at the baseband output, this can be characterized and corrected in later stages as long as the noise figure is low and the gain is high enough for the baseband frequency of interest. The TIA draws a total of 3.5 mA from the supply. 5. Measurement results The wideband current-commutating passive mixer is fabricated in TSMC 0.18 m RF CMOS technology. The chip photograph of the fully-integrated wideband mixer is shown in Fig. 10. The core chip size is 460 410 m2 . On-wafer measurement is carried out by mounting the wafer on a Cascade Summit 11000 probe station. The voltage conversion gain is measured using an Agilent E4440A Spectrum Analyzer, and the noise figure is measured by an Agilent N8975A NF Analyzer. The measured dc current is 5.5 mA from a 1.8 V supply voltage. The voltage conversion gain is measured using an Agilent E4440A spectrum analyzer. Considering the wideband applications of the mixer, LO signals with frequencies of 0.7 GHz, 1.57 GHz, and 2.2 GHz are applied respectively. With each fixed LO signal, we change the frequency of the input RF sig- 015003-6 J. Semicond. 2013, 34(1) Bao Kuan et al. Fig. 10. Chip photograph of the fully-integrated wideband mixer. Fig. 11. Measured voltage conversion gain with different input RF frequencies. nal, so that the output IF frequency can be swept from near DC to 50 MHz. Figure 11 illustrates the voltage conversion gain versus different IF frequency with 3 LO frequencies. It is clearly seen from Fig. 11 that the conversion gain with three LO frequencies are all above 20 dB with a –1 dB bandwidth of about 10 MHz. Figure 12(a) illustrates the 3rd order intermodulation phenomenon of the presented mixer. Two sinusoidal signals with frequencies of 2213 MHz and 2213.5 MHz are applied to the input of the mixer with a power of –20 dBm, and a LO frequency of 2.2 GHz. The 3rd order intermodulation product is about –72 dBm. In the same fashion, we increase the input power, and the output linear term and 3rd order intermodulation term is measured respectively. The measured and post-simulated output linear term and IM3 term is depicted in Fig. 12(b). With the extension of the two curves, the measured IIP3 is achieved with a value of 9 dBm while the simulated IIP3 is 11.6 dBm. The flick noise in the current-commutating passive mixer is inherently low thanks to its zero dc current in the switches transistors. The simulation results shows that the flick noise corner frequency of the presented mixer is 60 kHz as shown in Fig. 13(a), while its active competitor typically has a 1/f Fig. 12. (a) Measured 3rd order intermodulation phenomenon with fRF D 2.2 GHz, Pin D –20 dBm. (b) Post-simulated and measured IIP3of the mixer. noise corner frequency of hundreds of kHz or several MHz. It makes the passive mixer very attractive in direct conversion receivers. Figure 13(a) shows the simulation results with fLO D 2.2 GHz. Because the minimum measurable frequency using an Agilent N8975A noise figure analyzer is 10 MHz, the low frequency characteristics of the presented mixer cannot be measured. Figure 13(b) shows the measured noise figure with an output frequency from 10 to 50 MHz. The NF grows from about 30 MHz due to the decreasing conversion gain and no ideality of the chip and the measurement equipments. However, the NF measured at 10 to 25 MHz matches well with the simulated result. The measured NF is 10.6 dB at 10 MHz IF. The performance of the proposed passive mixer and other recently published passive mixers are summarized in Table 1. The comparison shows that the presented mixer achieves a wide RF bandwidth and wide IF bandwidth along with competitive linearity, noise figures, and power consumption compared to the other recently published mixers. 6. Conclusions This paper presents a wideband passive mixer for the direct conversion of multi-standard receivers. The currentcommutating structure is chosen considering the comparisons 015003-7 J. Semicond. 2013, 34(1) Bao Kuan et al. Table 1. Performance comparison. Parameter This work TMTT 2010Œ21 JSSC 2007Œ15 Technology RF frequency (GHz) VCG (dB) IF bandwidth (MHz) Noise figure (dB) 1/f noise corner (kHz) IIP3(dBm) Supply voltage (V) Total bias current (mA) Note 0.18 m CMOS 0.7–2.3 21 10 10.6 60 9 1.8 5.5 One mixer 0.18 m CMOS 1.55–2.3 22.5–25 NA 7.7–9.5 NA >7 2 5 IQ mixer 0.13 m CMOS 0.9–2.3 34.5 0.25 9.5–11.5 6 33 4–11 1.5 20–24 IQ mixer C Divider IEEE TCS 2011Œ23 0.13 m CMOS 0.048–0.86 19.5–21 NA 11.4 NA 8–9 1.2 4.5 One mixer J. Semicond. 2011Œ11 0.13 m CMOS 2.3–2.7 45 1.4/3/5/10/15/20 2.7 NA –7 1.2 40 LNA C IQ mixer sured IIP3 is 9.0 dBm and the measured double-sideband NF is 10.6 dB at 10 MHz IF. The chip drains a current of 5.5 mA from a 1.8 V supply. The characteristics of low 1/f noise, high linearity, flexible gain and moderate power consumption make this implementation a suitable alternative for multi-band, multi-standard radio applications. Acknowledgement We are grateful for encouraging discussions and technique assistance from the whole team in the Institute of RF- & OEICs, Southeast University. References Fig. 13. (a) Simulated NF of the mixer. (b) Measured NF of the mixer. between the current commutating passive mixers and active mixers. The effect of the mixer’s source and load impedance on its linearity was investigated in detail with special consideration given to the impact of input impedance of the TIA, which acts as the load impedance of the mixer. The analysis is verified by a mixer implemented in 0.18 m CMOS technology. Measurement results shows that with the RF frequency ranges from 700 MHz to 2.3 GHz, the proposed mixer achieves 21 dB of conversion voltage gain. Also, the measured intermediate frequency bandwidth is more than 10 MHz around dc. The mea- [1] Brandolini M, Rossi P, Manstretta D, et al. Toward multistandard mobile terminals—fully integrated receivers requirements and architectures. IEEE Trans Microw Theory Tech, 2005, 53(3): 1026 [2] Giannini V, Nuzzo P, Soens C, et al. A 2 mm2 0.1–5 GHz software-defined radio receiver in 45 nm digital CMOS. IEEE J Solid-State Circuits, 2009, 44(12): 3486 [3] Bao Kuan, Fan Xiangning, Li Wei, et al. A wideband LNA employing gate-inductive-peaking and noise-canceling techniques in 0.18 m CMOS. Journal of Semiconductors, 2012, 33(1): 015003 [4] Abidi. The path to SDR receiver. IEEE J Solid-State Circuits, 2007, 42(5): 954 [5] Lee T H. The design of CMOS radio-frequency integrated circuits. Cambridge, UK: Cambridge University Press, 2004 [6] Zhou S, Chang M C F. A CMOS passive mixer with low flicker noise for low-power direct-conversion receivers. IEEE J SolidState Circuits, 2005, 40(5): 1084 [7] Redman-White W, Leenaerts D M W. 1/f noise in passive CMOS mixers for low and zero IF integrated receivers. IEEE Eur Solid-State Circuits Conf, 2001: 41 [8] Darabi H, Abid A A. Noise in RF-CMOS mixers: a simple physical model. IEEE J Solid-State Circuits, 2000, 35(1): 15 [9] Terrovitis M T, Meyer R G. Intermodulation distortion in currentcommutating CMOS mixers. IEEE J Solid-State Circuits, 2000, 35(10): 1461 [10] Mirzaei, Darabi H, Yazdi A, et al. A 65 nm CMOS quad-band SAW-less receiver SoC for GSM/GPRS/EDGE Ahmad. IEEE J Solid-State Circuits, 2011, 46(4): 950 [11] Wang Riyan, Huang Jiwei, Li Zhengping, et al. A 1.2 V CMOS front-end for LTE direct conversion SAW-less receiver. Journal of Semiconductors, 2012, 33(3): 035005 015003-8 J. Semicond. 2013, 34(1) Bao Kuan et al. [12] Hao Shilei, Mei Niansong, Huang Yumei, et al. A 5 GHz 7.2 dB NF low power direct conversion receiver front-end with balun LNA. Journal of Semiconductors, 2011, 32(12): 125006 [13] Kim T W, Kim B. A 13-dB IIP3 improved low-power CMOS RF programmable gain amplifier using differential circuit transconductance linearization for various terrestrial mobile D-TV applications. IEEE J Solid-State Circuits, 2006, 41(4): 945 [14] Kim T W, Kim B, Lee K. Highly linear receiver front-end adopting MOSFET transconductance-linearization by multiple gated transistors. IEEE J Solid-State Circuits, 2004, 41(4): 223 [15] Poobuaphen N, Chen W H, Boos Z, et al. A 1.5 V, 0.7–2.5 GHz CMOS quadrature demodulator for multiband direct-conversion receiver. IEEE J Solid-State Circuits, 2007, 42(8): 1669 [16] Ingels M, Giannini V, Borremans J, et al. A 5 mm2 40 nm LP CMOS transceiver for a software-defined radio platform. IEEE J Solid-State Circuits, 2010, 45(12): 2794 [17] Bagheri R, Mirzaei A, Chehrazi S, et al. An 800 MHz–6 GHz software-defined wireless receiver in 90-nm CMOS. IEEE J Solid-State Circuits, 2006, 41(12): 2860 [18] Elahi I, Muhammad K. IIP2 calibration by injecting DC offset at the mixer in a wireless receiver. IEEE Trans Circuits Syst I, Reg Papers, 2007, 54(12): 1135 [19] Manstretta D, Brandolini M, Svelto F. Second-order intermodulation mechanisms in CMOS down converters. IEEE J SolidState Circuits, 2003, 38(3): 394 [20] Brandolini M, Rossi P, Sanzogni D, et al. A CMOS direct downconverter with C78 dBm minimum IIP2 for 3G cell-phones. IEEE International Solid-State Circuits Conference, 2005 [21] Kim N, Aparin V, Larson L E. A resistively degenerated wideband CMOS passive mixer with low noise figure and high IIP2. IEEE Trans Microw Theory Tech, 2010, 58(4): 820 [22] Khatri H, Gudem P S, Larson L E. Distortion in current commutating passive CMOS down conversion mixers. IEEE Trans Microw Theory Tech, 2009, 57(11): 2671 [23] Le V H, Nguyen H N, Lee I Y, et al. A passive mixer for a wideband TV tuner. IEEE Trans Circuits Syst II, 2011, 58(7): 398 015003-9