- Kamaljeeth Instrument

J F E C H A R A C T E S T C S

Experiment-449 S

JFET CHARACTERISTICS

Jeethendra Kumar P K

KamalJeeth Instrumentation & Service Unit, Tata Nagar, Bengaluru-560 092, Karnataka, INDIA

Email: labexperiments@kamaljeeth.net

Abstract

Input characteristics (transconductance) curve and output characteristics (drain) curves of an n-channel junction field effect transistor (JFET) are determined using a

BFW-10 JFET. From these characteristic curves, maximum drain current, I

DSS;

pinchoff voltage, V

GS(off)

; and drain-source resistance, R

DS(on)

are determined and compared with the corresponding standard values. The drain current equation is also verified.

Introduction

A junction field effect transistor (JFET) is a uni-polar semiconductor device in which only one type of charge carriers are involved in conduction. A JFET or FET differs from a bipolar transistor in several ways. The most important being that in a bipolar transistor the small input (base) current controls the large output (collector) current, making it a current controlled device. In the case of a FET, it is the input voltage that controls the output current making it a voltage-controlled device. The output drain current is controlled by the electric field across the conducting channel of the semiconductor, from which the name field effect transistor has been derived.

There are two types of FETs. The Junction FET in which the control electrode or gate is isolated from the conducting channel by a reverse biased junction and in the insulated gate field effect transistor (or MOSFET ) a layer of silicon dioxide is used to insulate the control electrode making it a very high input resistance device.

An n-channel JFET consists of n-type silicon bar in which two p-islands are deposited that are interconnected and called as the gate (G) terminal. The lower portion of the bar is called source (S) and upper portion of the bar is called drain (D). Figure-1 shows the schematic structure, symbols and the base diagram of a JFET. Similarly a p-channel

JFET has p-bar and n-type islands. In the schematic representation, for a p-channel

JFET the direction of the arrow at the gate is reversed.

1

K A M A L J E E T H N S T R U M E N T S

J F E C H A R A C T E S T C S

Figure-1: Structure, symbols and the base diagram of an N-channel JFET

The gate controls the flow of current through the bar by modifying its resistance. When no potential is applied to the gate, the bar has maximum resistance, called the sourcedrain resistance, R

DS (on)

. For this biasing condition, the source-drain resistance is minimum, and hence the maximum current flows from source to drain. This maximum current is called I

DSS

. Under these conditions the two p-islands form very thin depletion layers around them and provide large space for the electrons to flow from the source to drain.

As negative gate voltage is applied with respect to the source, the depletion regions grows which makes it difficult for electrons to flow from source to drain, hence the drain current is reduced. As the negative gate voltage is increased further, the drain current will decrease further and become zero at a voltage at which the depletion regions come very close to each other around the two islands making difficult for electrons to pass through. This gate voltage at which the drain current becomes zero is called “pinch-off voltage” or V

DS(Off)

.

For low drain-source voltage (V

DS

), the two depletion regions are thin and the current increases with the applied voltage linearly, initially with increase in V

DS

. As V

DS increases, the two depletion layers come closer (but never touch each other) and the drain current thereafter remains constant with further increase in the V

DS

value.

Hence the current flowing from source to drain is called drain current and it is controlled by gate voltage [1, 2]. The drain current is given by:

I

ୈ

=

I

ୈୗୗ

ቀ1 −

ృ

ౌ

ቁ

ଶ

− ቀ1 −

ృ

ି

ీ

ౌ

ቁ

ଶ

൨ where V

DS

is drain-source voltage,

V

GS

is gate –source voltage,

V

P

is pinch-off voltage, and

I

DSS

is maximum drain current.

…1

2

K A M A L J E E T H N S T R U M E N T S

J F E C H A R A C T E S T C S

Equation-1, giving the ratio of current and voltage, represents a non-linear curve; hence it is called transconductance curve or input characteristic curve. The input is voltage (V

GS

) and output is current (I

D

), the maximum value of which gives the maximum transconductance as g mo

=

ିଶ୍

ీ

ౌ where

…2 g mo is the maximum value of transconductance ( for V

GS

=0),

I

DSS

is the maximum drain-source current (for V

GS

=0), and

V

P is the pinch-off voltage.

Knowing the maximum value of transconductance, g mo

, transconductance for any gatesource voltage can be calculated using the Equation g m

= g mo

ቂ1 −

ృ

ౌ

ቃ

…3

Equation-3 represents a parabolic curve.

The other parameter associated with JFET is the drain source resistance and its variation with the source gate voltage is given by

R

DS

= R

DS(on)

ቂ1 −

ృ

ౌ

ቃ

…4 where

R

DS(on

=-

ౌ

ଶ୍

ీ

…5

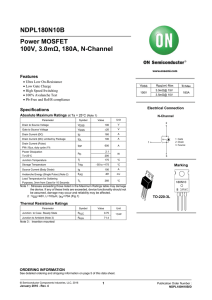

Apparatus used

The experimental setup for studying JFET characteristics consists of a dual power supply -0-5V and 0-10V, digital DC voltmeter 0-20V, and digital DC milli-ammeter 0-

20mA. Figure-3 shows the experimental set-up used.

Figure-2: Circuit connections for studying JFET characteristics

K A M A L J E E T H N S T R U M E N T S

3

J F E C H A R A C T E S T C S

Figure-3: Experimental set-up of FET-201 of KamalJeeth make for studying JFET characteristics

Experimental procedure

The experiment consists of four parts, namely

Part-A: Determination of maximum drain current, I

DSS

Part-B: Determination of the pinch-off voltage, V

P

(V

GS (OFF)

)

Part-C: Transconductance curve (Input curve)

Part-D: Output characteristics curve for different values of gate source voltage

Part-A: Determination of maximum drain current, I

DSS

1.

The circuit connections are made as per the circuit diagram shown in Figure-2 and the BFW-10 JFET is fixed into to the socket, as shown in Figure-3.

2.

The gate-source voltage is set to 0V, by adjusting the voltage control knob of V

GG power supply

V

GS

=0V

3.

The drain-source voltage V

DS

is now set to its maximum value by adjusting the two

(coarse and fine) knobs of the V

DD

power supply and maximum drain current is noted as

I

DSS

= 10.45mA

4

K A M A L J E E T H N S T R U M E N T S

J F E C H A R A C T E S T C S

Part-B: Determination of the pinch-off voltage

,

V

P

(V

GS (OFF)

)

4.

The negative gate-source voltage is now slowly increased by observing the decrease in the drain current until it becomes zero.

I

D

=0

5.

The gate voltage is now measured by connecting the voltmeter across the V

GS terminal, as shown in Figure-4.

V

P

= V

GS(OFF)

= -3.11V

Figure-4: Determination of the pinch-off voltage

Part-C: Transconductance curve (Input curve)

6.

To draw the transconductance curve, first V

GS

is set to 0V and V

DS is set to 5V and the value of current I

D is noted.

I

D

= 10.45mA

7.

The experiment is repeated by setting V

GS

=-0.5V and V

DS

is set as 5.0V and the drain current is noted.

I

D

= 7.9mA

8.

The experiment is repeated for V

GS

=-1.0V, keeping V

DS

constant at 5V throughout.

The readings obtained are tabulated in Table-1. The graph giving the variation of drain current with gate voltage is shown in Figure-5 from which the value of V

P

is noted as

5

K A M A L J E E T H N S T R U M E N T S

J F E C H A R A C T E S T C S

V

P

=-3.0V

The maximum transconductance, g mo

, can be calculated using Equation-2 as g mo

=

ିଶ୍

ీ

ౌ

= -

ିଶ௫ଵ.ସହ௫ଵ షయ

ିଷ.

= 6.96x10

-3 mho

Table-1: Variation of drain current with gate voltage

Transconductance Curve V

DS

= 5.00V

Gate-Source Drain current I

D

Voltage V

GS

(V) (mA)

0

-0.5

-1.0

-1.5

-2.0

-2.5

-3.0

10.45

7.90

5.73

3.73

2.23

0.83

0.01

Figure-5: Transconductance curve of BFW-10 JFET for V

DS

=5V

Part-D: Output characteristics curve for different values of gate source voltage

9.

In this part of the experiment, keeping V

GS

constant, the variation in I

D

is observed with respect to V

DS

.

6

K A M A L J E E T H N S T R U M E N T S

J F E C H A R A C T E S T C S

10.

First keeping V

GS

= 0, the V

DS

versus I

D

variation is studied. V

DS

is varied in steps of

0.1V from 0V up to 2V and from 2V onwards it is varied in steps 0.2V up to 3V, and from 3V to 5V in steps of 1V. Table-2 gives the observed voltage and current variations.

Table-2: Drain current variation with Drain-source voltage at different Gate voltage

Drain Current I

D

(mA)

V

DS

(V)

0

V

GS

= 0V

0

V

GS

= -1.5V

0

V

GS

=-2.5V

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.69

1.34

1.92

2.60

3.16

3.67

4.24

4.77

0.39

0.71

1.02

1.33

1.64

1.89

2.13

2.35

0.11

0.23

0.30

0.37

0.42

0.46

0.48

0.51

1.6

1.8

2.0

2.2

2.4

2.6

0.9

1.0

1.2

1.4

5.21

5.62

6.43

7.21

7.81

8.28

8.71

9.12

9.39

9.62

2.53

2.70

2.96

3.17

3.31

3.43

3.51

3.58

3.62

3.67

0.52

0.54

0.56

0.58

0.60

0.61

0.62

0.63

0.64

0.65

2.8

3.0

4.0

9.79

9.99

10.37

3.70

3.72

3.83

0.66

0.67

0.70

5.0 10.46 3.88 0.73

11.

From the above figure it is noted that after reaching the pinch off voltage, the current subsequently remains constant. The small change in the current thereafter is due to the thermal heating of the JFET that can be observed by touching it with a finger.

12.

A graph is drawn taking V

DS

along X-axis and I

D

along Y-axis as shown Figure-6.

This is the output characteristics curve of the JFET.

7

K A M A L J E E T H N S T R U M E N T S

J F E C H A R A C T E S T C S

13.

The JFET is removed from the socket and its source-drain resistance is measured using a digital multimeter.

R

DS(on)

= 160Ω

This can also be calculated from Equation-5 as

R

DS(on

=-

ౌ

ଶ୍

ీ

=

ଷ

ଶ୶ଵ.ସହ

= 143.5Ω

Equation-1 obtains

can also be verified, for example for V

GS

=-1.5V and V

DS

= 1V, one

I

D

= 2.32mA, which is close to the value 2.7mA, as given in Table-2.

Figure-4: Output Characteristics of BFW 10 JFET

Results

The characteristic parameters of BFW-10 JFET obtained are listed in Table-3 as

Table-3: Experimental results

Parameter Experimental Standard

I

DSS

(mA)

V p

(V)

R

DS(ON)

(Ω) g mo

(mS)

10.45

-3.1V

149

7

*Measured value

<

20

<

-8V

160*

<

12

K A M A L J E E T H N S T R U M E N T S

8

J F E C H A R A C T E S T C S

Discussion

1.

The output characteristics curves, or the drain curves, of the BFW-10 JFET resemble that of transistor output characteristic curves, with the difference that the base current I

B

is replaced by V

GS

. The value of the saturation voltage is higher in a JFET compared to a transistor which is around 0.3V for a silicon transistor.

2.

The transconductance curve meets the Y-axis at a point giving the maximum value of the drain current I

DSS

and meets the X-axis at a point giving the maximum value of the voltage Vp.

References

1.

A P Malvino, Electronic Principles, TMD Ed 3 rd Ed, 1987, Page-321

2.

W Goswng, W G Townsend, J Watson, Field Effect Electronics, Butterworth

London, Page-18

K A M A L J E E T H N S T R U M E N T S

9