Common-Base Input Resistance R

advertisement

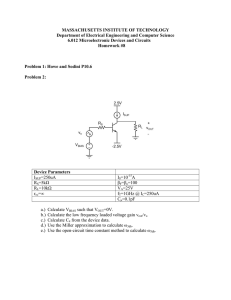

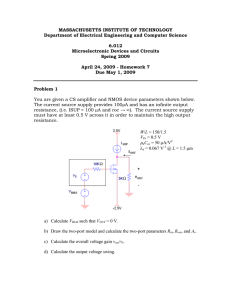

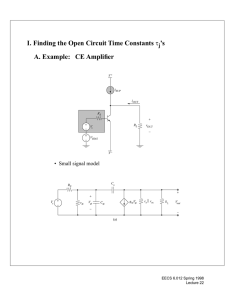

Common-Base Input Resistance Rin ■ Apply test current, with load resistor RL present at the output + vπ − gmvπ rπ ro roc + vt − RL it The transconductance generator dominates the sum of the currents at the input node since gm >> ro-1 and gm >> rπ-1 and 1 R in ≈ -----gm EE 105 Spring 1997 Lecture 18 Common-Base Output Resistance Rout ■ Test circuit: leave source resistance of input current in place; remove roc for analysis and place it in parallel ... gmvπ − vπ + ■ ro + vt − rπ it roc RS Complicated analysis (see Section 8.8), with the final result boiling down to: R out ≈ r oc [ r o ( 1 + g m ( r π R S ) ) ] If the RS is much greater than rπ, then the output resistance is approximately: R out ≈ r oc [ βr o ] EE 105 Spring 1997 Lecture 18 Common-Base Two-Port Model ■ Note that the output resistance depends on the source resistance -- which means that the CB current buffer is not unilateral and the two-port formal model is not strictly valid. However, the error in using the model is small (see Appendix A8.1). iin iout 1 gm ■ −iin roc ro[1 + gm(rπRS)] Controlled source can be flipped to make current gain + 1. EE 105 Spring 1997 Lecture 18 Common-Gate Amplifier ■ Circuit configuration: analogous to common-base V+ V+ iSUP ISUP IOUT iOUT V− V− RL is RS IBIAS IBIAS V− V− (a) (b) The backgate can be tied to the source if the device is in a well. It is obvious that the current gain for this amplifier must be unity, since the gate current for a MOSFET is zero EE 105 Spring 1997 Lecture 18 Common-Gate Two-Port Model ■ The resulting two port model is: iin iout −iin 1 gm + gmb roc (ro + gmroRS) The input resistance is the same as for the CB for the case where source and backgate are shorted. When this isn’t the case, the backgate generator is added in: 1 R in = -----gm ■ or 1 R in = ----------------------g m + g mb The output resistance is similar to the CB result with rπ --> infinity R out = r oc r o [ 1 + g m R S ] EE 105 Spring 1997 Lecture 18 Common-Collector Amplifier ■ Circuit configuration V+ V+ RS vs VBIAS + − + VBIAS + − vOUT iSUP + VOUT + − RL ISUP − − V− V− (a) ■ (b) Biasing: if transistor is “on” (i.e., not cutoff), then VBIAS - VOUT = 0.7 V EE 105 Spring 1997 Lecture 18 Common-Collector as a Small-Signal Amplifier ■ Linear relationship between output voltage and total input voltage indicates that the CC amplifier is a voltage buffer -- the voltage gain is about equal to 1. ■ Small-signal model and procedure for finding Av for two-port model: + vπ vt + − gmvπ rπ ro − roc + vout − ■ Circuit analysis: current through roc || ro is vπ / rπ + gm rπ --> v t – v out v out -------------------- + g m ( v t – v out ) = ----------------r oc r o rπ multiplying by rπ and recognizing that gm rπ = βo, v out r π v t – v out + β o ( v t – v out ) = ( 1 + β o ) ( v t – v out ) = ----------------r oc r o solving for the open-circuit voltage gain: 1 A v = ----------------------------------------------- ≈ 1 rπ 1 + -------------------------------------r oc r o ( β o + 1 ) EE 105 Spring 1997 Lecture 18 Common-Collector Input Resistance Rin ■ Procedure: apply pure test source, leave load resistor RL in -- very important for CC amplifier ib it + vt βoib rπ − ro roc RL note that current through roc || ro ||RL is it + βo it --> R in = r π + ( β o + 1 ) ( r oc r o R L ) ■ When the load resistor is much smaller than the output resistance of the transistor and the current source resistance, then the input resistance of the CC amplifier is approximately Rin = rπ + (βo + 1)RL EE 105 Spring 1997 Lecture 18 Common Collector Output Resistance ■ Apply test current source at the output, leaving any source resistance RS attached at the input. + vπ gmvπ rπ − RS ro roc it vt + − KCL at the common node + algebra --> 1 RS R out = ------ + -----gm βo EE 105 Spring 1997 Lecture 18 Common Collector Two-Port Model ■ Final result: pretty good voltage buffer: 1/gm + RS /βo + vin − rπ + βo(ro roc RS) + − + vin vout − Note: this model is approximate and can give erroneous results for extremely low values of RL. However, it is very convenient for hand analysis. EE 105 Spring 1997 Lecture 18 Common-Drain Amplifier ■ Similar configuration to common collector. V+ V+ RS vs VBIAS + − + VBIAS + − iSUP vOUT RL + VOUT + − ISUP − − V− V− Analysis: much the same as for CC amplifier -- if VSB isn’t zero, then the voltage gain is degraded from about 1 to 0.8-0.9 EE 105 Spring 1997 Lecture 18 Common-Drain Two-Port Model ■ Two-Port model: 1 (gm + gmb) + vin − + + − gm (gm + gmb) vin vout − If VSB = 0, then the input resistance is Av = 1 and Rout = 1 / gm (for hand analysis) The CD amplifier is a reasonable voltage buffer, especially for large (W / L) --> large gm. EE 105 Spring 1997 Lecture 18 Single-Stage Amplifier Configurations ■ Two complemetary versions exist for each amplifier type. ■ CS/CE, CG/CB, and CD/CC have similar topologies (and properties) Transistor Type Amplifier Type NMOS PMOS npn pnp V+ V+ V+ V+ IN iSUP Common Source/ Common Emitter (CS/CE ) iSUP OUT OUT IN IN iSUP V− V+ V− V+ IN iSUP OUT OUT iSUP V− V+ V− V+ IN iSUP OUT Common Gate/ Common Base (CG/CB) OUT OUT OUT iSUP IN V− V+ iSUP IN V− V+ V− V+ IN Common Drain/ Common Collector (CD/CC ) IN iSUP V− V+ iSUP IN OUT OUT OUT OUT IN IN iSUP iSUP V− V− V− V− EE 105 Spring 1997 Lecture 18 Two-Port Parameters for Single-Stage Amplifiers Amplifier Type Controlled Source Input Resistance Rin Output Resistance Rout Common Emitter Gm = gm rπ ro || roc Common Emitter +RE Gm = gm / (1+gmRE) rπ ( 1 + gm RE) roc || [(1 + gmRE)ro] for rπ >> RE, RS Common Source Gm = gm infinity ro || roc Common Base Ai = -1 1 / gm roc || [(1 + gm(rπ||RS)) ro], for gmRS >> 1 Ai = -1 1 / gm, (vsb = 0) -otherwise1 / (gm + gmb) roc ||[(1 + gm RS)ro], (vsb=0) -otherwiseroc || [(1+ (gm + gmb)RS) ro] both for gmRS >> 1 Common Collector Av = 1 rπ + βο(ro || roc|| RL) (1 / gm ) + RS / βο Common Drain Av = 1 if vsb = 0, -otherwisegm / (gm + gmb) infinity 1 / gm if vsb = 0, -otherwise1 / (gm + gmb) Common Gate Note: appropriate two-port model is used, depending on controlled source EE 105 Spring 1997 Lecture 18 Ultra-Simplified Two-Port Parameters ■ ■ gmb = 0, common base has reasonable source resistance --> RS >> rπ Amplifier Type Controlled Source Input Resistance Ri Output Resistance Ro Common Emitter Gm = gm rπ ro || roc Common Source Gm = gm infinity ro || roc Common Base Ai = -1 1 / gm roc || (β ro) Common Gate Ai = -1 1 / gm roc ||[(1+gm RS) ro] Common Collector Av = 1 rπ + β (ro || roc|| RL) (1 / gm ) + RS / β Common Drain Av = 1 infinity 1 / gm this table is adequate for first-cut hand design EE 105 Spring 1997 Lecture 18