LT5502 - 400MHz Quadrature IF Demodulator with RSSI

advertisement

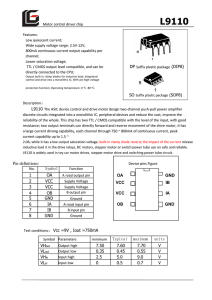

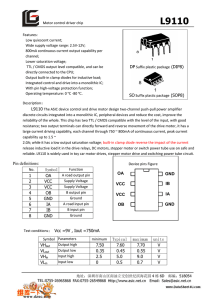

LT5502 400MHz Quadrature IF Demodulator with RSSI U DESCRIPTIO FEATURES ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ The LT®5502 is a 70MHz to 400MHz monolithic integrated quadrature IF demodulator. It consists of an IF limiter, quadrature down mixers, integrated lowpass filters, and divide-by-two LO buffers. The demodulator provides all building blocks for demodulation of I and Q baseband signals with a single supply voltage of 1.8V to 5.25V. The IF limiter has 84dB small-signal gain, and a built-in receive signal strength indicator (RSSI) with over 90dB linear range. The input referred noise-spectral-density is 1.45nV/√Hz, which is equivalent to a 4dB noise figure when the input is terminated with a 50Ω source. The integrated lowpass output filters act as antialiasing and pulse-shaping filters for demodulated I/Q-baseband signals. The 3dB cutoff frequency of the filters is about 7.7MHz. The VCO frequency is required to be twice the desired operating frequency to provide quadrature local oscillator (LO) signals to the mixers. The standby mode provides fast transient response to the receive mode with reduced supply current when the I/Q outputs are AC-coupled to a baseband chip. Single 1.8V to 5.25V Supply IF Frequency Range: 70MHz to 400MHz 84dB Limiting IF Gain 90dB Linear RSSI Range 7.7MHz Lowpass Output Filter Baseband I/Q Amplitude Imbalance: <0.7dB 4dB Noise Figure Low Supply Current: 25mA Outputs Biased Up While in Standby Shutdown Current: 1µA 24-Lead Narrow SSOP Package U APPLICATIO S ■ ■ ■ IEEE802.11 High Speed Wireless LAN Wireless Local Loop , LTC and LT are registered trademarks of Linear Technology Corporation. U TYPICAL APPLICATIO I/Q Output Swing, RSSI Output vs IF Input Power 2V C3 22nF R1 240Ω IF + 1200 VCC IF – 2XLO IOUT+ 90° 2XLO INPUT QOUT+ ÷2 0° 2XLO – LT5502 ENABLE EN IOUT– + GND BASEBAND DIFFERENTIAL I/Q OUTPUTS QOUT– RSSI C4 1.8pF 5502 TA01a 1.2 1000 1.0 800 0.8 600 0.6 400 0.4 200 –85 RSSI OUTPUT (V) IF INPUT C1 1nF DIFFERENTIAL OUTPUT SWING (mVP-P) C2 1µF 0.2 –70 –55 –40 –25 –10 IF INPUT POWER (dBm) 5 5502 TA01b Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights. 1 LT5502 U W W W ABSOLUTE AXI U RATI GS U W U PACKAGE/ORDER I FOR ATIO (Note 1) TOP VIEW Power Supply Voltage ............................................ 5.5V LO Input Power .................................................. 10dBm IF Input Power .................................................... 10dBm Operating Ambient Temperature (Note 2) ..............................–40°C to 85°C Storage Temperature Range ................. – 65°C to 150°C Lead Temperature (Soldering, 10 sec).................. 300°C Voltage on any Pin not to Exceed ............................. VCC + 1 24 QOUT+ IOUT– 2 23 QOUT– GND 3 22 VCC IOUT VCC 4 21 GND GND 5 20 GND IF + 6 19 2XLO+ IF – 7 18 2XLO – GND 8 17 VCC GND 9 16 VCC EN 10 15 RSSI STBY 11 14 GND IFt + 12 ORDER PART NUMBER LT5502EGN 13 IFt – GN PACKAGE 24-LEAD NARROW PLASTIC SSOP TJMAX = 150°C, θJA = 85°C/W Consult factory for parts specified with wider operating temperature ranges. ELECTRICAL CHARACTERISTICS PIF = –50dBm, TA = 25°C, unless otherwise noted. (Note 3) SYMBOL PARAMETER VCC = 3V, f2XLO = 570MHz, P2XLO = –10dBm, f IF = 280MHz, CONDITIONS MIN TYP MAX UNITS IF Input fIF Frequency Range 3dB Limiting Sensitivity Noise Figure Terminated 50Ω Source DC Common Mode Voltage 70 to 400 MHz –79 dBm 4 dB 2.6 V 850 mVP-P Demodulator I/Q Output I/Q Output Voltage Swing Differential I/Q Amplitude Mismatch 0.1 I/Q Phase Mismatch Output Driving Capability 0.7 0.6 Differential; CMAX = 10pF DEG 1.5 DC Common Mode Voltage dB kΩ 1.84 V 90 dB 3.8 kΩ RSSI Linear Dynamic Range (Note 4) ±3dB Linearity Error Output Impedance Output Voltage Input = – 70dBm 0.27 0.41 0.54 V Output Voltage Input = 0dBm 0.8 1.01 1.2 V Output Voltage Slope Input from –70dBm to 0dBm 8.7 Linearity Error Input from –70dBm to 0dBm 1 mV/dB dB Baseband Lowpass Filter 2 3dB Cutoff Frequency 7.7 MHz Group Delay Ripple 16.4 ns LT5502 ELECTRICAL CHARACTERISTICS PIF = –50dBm, TA = 25°C, unless otherwise noted. (Note 3) SYMBOL PARAMETER VCC = 3V, f2XLO = 570MHz, P2XLO = –10dBm, f IF = 280MHz, CONDITIONS MIN TYP MAX UNITS –5 dBm 2XLO f2XLO Frequency Range P2XLO Input Power 140 to 800 MHz –20 DC Common Mode Voltage 2.6 V Power Supply VCC Supply Voltage 1.8 ICC Supply Current IOFF Shutdown Current Standby Mode Current EN = High 32 EN = Low; Standby = Low 1 100 µA EN = Low; Standby = High 2.6 3.5 mA U W I/Q Output Swing vs IF Input Power 1200 fIF = 280MHz DIFFERENTIAL OUTPUT SWING (mVP-P) SUPPLY CURRENT (mA) DIFFERENTIAL OUTPUT SWING (mVP-P) TA = 85°C TA = 85°C TA = 25°C 24 TA = –40°C 20 2.5 3.5 4.5 SUPPLY VOLTAGE (V) 5.5 5502 G01 TA = 25°C 800 TA = –40°C 600 400 1.8 VCC = 3V fIF = 280MHz 1000 1000 28 16 1.8 (Note 3) I/Q Output Swing vs Temperature 1200 36 2.5 mA Note 3: Tests are performed as shown in the configuration of Figure 3. Note 4: Tests are performed as shown in the configuration of Figure 1 for IF input. TYPICAL PERFOR A CE CHARACTERISTICS Power Supply Current vs Temperature V 25 Note 1: Absolute Maximum Ratings are those values beyond which the life a device may be impaired. Note 2: Specifications over the –40°C to 85°C temperature range are assured by design, characterization and correlation with statistical process controls. 32 5.25 3.5 4.5 SUPPLY VOLTAGE (V) 5.5 5502 G02 TA = 85°C TA = 25°C 800 600 TA = –40°C 400 200 –85 –70 –55 –40 –25 –10 IF INPUT POWER (dBm) 5 5502 G03 3 LT5502 U W TYPICAL PERFOR A CE CHARACTERISTICS (Note 3) I/Q Output Swing vs IF Input Power VCC = 3V TA = 25°C 1.2 VCC = 3V fIF = 280MHz 800 fIF = 280MHz 600 0.8 TA = 85°C TA = –40°C 0.6 TA = 25°C 0.8 fIF = 70MHz 0.6 0.4 0.4 –55 –40 –25 –10 IF INPUT POWER (dBm) 0.2 –85 5 –70 –55 –40 –25 –10 IF INPUT POWER (dBm) –73 INPUT SENSITIVITY (dBm) 1.0 0.8 VCC = 3V 0.6 VCC = 5.5V VCC = 1.8V 0.4 –55 –40 –25 –10 IF INPUT POWER (dBm) fIF = 280MHz –75 TA = 85°C –77 TA = 25°C –79 TA = –40°C –81 –83 1.8 5 2.5 4.5 SUPPLY VOLTAGE (V) 5 110 0 VCC = 3V TA = –40°C –82 70 100 150 200 250 300 IF FREQUENCY (MHz) 350 TA = –40°C 65 TA = 25°C 50 110 VCC = 1.8V, 3V, 5.5V TA = 25°C 0 TA = 85°C 80 –5 90 –10 –15 70 –20 –25 35 –30 20 –35 0 4 8 16 12 BASEBAND FREQUENCY (MHz) 20 5502 G10 400 LPF Frequency Response vs VCC 5 –25 4 TA = –40°C 50 –30 0 4 8 12 16 BASEBAND FREQUENCY (MHz) 20 5502 G11 –35 0 4 8 16 12 BASEBAND FREQUENCY (MHz) 30 20 5502 G12 GROUP DELAY (ns) GROUP DELAY (ns) –5 –20 TA = 25°C 5502 G09 95 TA = 85°C –15 –79 5.5 LPF Group Delay vs Baseband Frequency TA = 25°C TA = 85°C 5502 G08 VCC = 3V –10 VCC = 3V –76 –85 3.5 5502 G07 LPF Frequency Response vs Baseband Frequency 5 IF Input Sensitivity vs IF Frequency –73 GAIN RESPONSE (dB) –70 –55 –40 –25 –10 IF INPUT POWER (dBm) 5502 G06 IF Input Sensitivity vs Temperature fIF = 280MHz TA = 25°C 0.2 –85 –70 5502 G05 RSSI Output Voltage vs VCC 1.2 0.2 –85 5 INPUT SENSITIVITY (dBm) –70 fIF = 400MHz 5502 G04 RSSI OUTPUT (V) fIF = 280MHz fIF = 400MHz 400 200 –85 GAIN RESPONSE (dB) VCC = 3V TA = 25°C 1.0 1.0 fIF = 70MHz RSSI OUTPUT (V) 1000 RSSI Output Voltage vs IF Frequency RSSI Output vs Temperature 1.2 RSSI OUTPUT (V) DIFFERENTIAL OUTPUT SWING (mVP-P) 1200 LT5502 U U U PI FU CTIO S IOUT+ (Pin 1): Positive Baseband Output Pin of I-Channel. The DC bias voltage is VCC – 1.16V. This pin should not be shorted to ground. IOUT– (Pin 2): Negative Baseband Input Pin of I-Channel. The DC bias voltage is VCC – 1.16V. This pin should not be shorted to ground. GND (Pins 3, 5, 8, 9, 14, 20, 21): Ground Pin. VCC (Pins 4, 16, 17, 22): Power Supply Pin. This pin should be decoupled using 1000pF and 0.1µF capacitors. IF + (Pin 6): Positive IF Input Pin. The DC bias voltage is VCC – 0.4V. IF – (Pin 7): Negative IF Input Pin. The DC bias voltage is VCC – 0.4V. EN (Pin 10): Enable Pin. When the input voltage is higher than 0.9V or up to VCC, the circuit is completely turned on. When the input voltage is less than 0.7V or down to ground, the circuit is turned off except the part of the circuit associated with standby mode. STBY (Pin 11): Standby Pin. When the input voltage is higher than 0.9V or up to VCC, the circuit of standby mode is turned on to bias the I/Q buffers to desired quiescent voltage. When the input voltage is less than 0.7V or down to ground, it is turned off. IFt + (Pin 12): Interstage IF Positive Pin. The DC bias voltage is VCC – 0.25V. IFt – (Pin 13): Interstage IF Negative Pin. The DC bias voltage is VCC – 0.25V. RSSI (Pin 15): RSSI Output Pin. 2XLO – (Pin 18): Negative Carrier Input Pin. The inputsignal’s frequency must be twice that of the desired demodulator LO frequency. The DC bias voltage is VCC – 0.4V. 2XLO + (Pin 19): Positive Carrier Input Pin. The inputsignal’s frequency must be twice that of the desired demodulator LO frequency. The DC bias voltage is VCC – 0.4V. QOUT– (Pin 23): Negative Baseband Output Pin of the Q-Channel. The DC bias voltage is VCC – 1.16V. This pin should not be shorted to ground. QOUT+ (Pin 24): Positive Baseband Output Pin of the Q-Channel. The DC bias voltage is VCC – 1.16V. This pin should not be shorted to ground. W BLOCK DIAGRA IFt+ IFt– 12 13 I-MIXER 6 IF – 7 1 IOUT+ 2 IOUT– 1 LIMITER 2 LIMITER 1 IF + LPF LO BUFFERS DIVIDE 2 0°/90° LPF 24 QOUT+ 1 RSSI 23 QOUT– Q-MIXER BIAS 15 RSSI 19 2XLO + 18 2XLO – 10 EN 5502 BD 5 LT5502 U W U U APPLICATIO S I FOR ATIO The LT5502 consists of the following sections: IF limiter, I/Q demodulators, quadrature LO carrier generator, integrated lowpass filters (LPFs), and bias circuitry. An IF signal is fed to the inputs of the IF limiter. The limited IF signal is then demodulated into I/Q baseband signals using the quadrature LO carriers that are generated from the divide-by-two circuit. The demodulated I/Q signals are passed through 5th order LPFs and buffered with an output driver. The 1:4 IF input transformer can also be replaced with a narrow band single-to-differential conversion circuit using three discreet elements as shown in Figure 1. Their nominal values are listed in Table 1. Due to the parasitics of the PCB, their values need to be compensated. The receiver’s input sensitivity in this case is improved to –85dBm even without interstage filtering. The matching circuit is essentially a second order bandpass filter. Therefore, the requirement for the front-end channel-select filter can be eased too. IF Limiter The IF limiter has 84dB small-signal gain with a frequency range of 70MHz to 400MHz. It consists of two cascaded stages of IF amplifiers/limiters. The differential outputs of the first stage are connected internally to the differential inputs of the second stage. An interstage filtering is possible in between (Pin 12 and Pin 13) with minimum offchip components. It can be a simple parallel LC tank circuit L1 and C8 as shown in Figure 3. The 22nF blocking capacitor, C19, is used for the proper operation of the internal DC offset canceling circuit. To achieve the best receiver sensitivity, a differential configuration at the IF input is recommended due to its better immunity to 2XLO signal coupling to the IF limiter. Otherwise, the 2XLO interference, presented at the IF inputs, may saturate the IF limiter and reduce the gain of the wanted IF signal. The receiver’s 3dB input-limiting sensitivity will be affected correspondingly. The interstage bandpass filter will minimize both 2XLO feedthrough and the receiver’s noise bandwidth. Therefore, the receiver’s input sensitivity can be improved. Without the interstage filter, the second stage will be limited by the broadband noise amplified by the first stage. The noise bandwidth in this case can be as high as 500MHz. The 3dB input limiting sensitivity is about –79dBm at an IF frequency of 280MHz when terminated with 200Ω at the input. The differential IF input impedance is 2.2kΩ. Therefore, a 240Ω resistor is used for R3 as shown in Figure 3. Using a bandpass filter with 50MHz bandwidth, the input sensitivity is improved to –86dBm. 6 MATCHING NETWORK CS1 3.3pF IF INPUT C5 22nF TO IF + CS2 3.3pF LSH 120nH TO IF – 5502 F01 Figure 1. IF Input Matching Network at 280MHz Table 1. The Component Values of Matching Network LSH, CS1 and CS2 fIF (MHz) LSH (nH) CS1/CS2 (pF) 70 642 13.7 100 422 9.6 150 256 6.4 200 176 4.8 250 130 3.8 300 101 3.2 350 80.4 2.7 400 66.0 2.4 In an application where a lower input sensitivity is satisfactory, one of the IF inputs can be simply AC-terminated with a 50Ω resistor and the other AC-grounded. The input receiver’s sensitivity is about – 76dBm at 280MHz in this case. LT5502 U W U U APPLICATIO S I FOR ATIO The receive signal strength indicator (RSSI) is built into the IF limiter. The input IF signal is detected in a current output proportional to the IF input power. The current outputs from two cascaded stages of IF amplifiers/limiters are summed and converted into the RSSI voltage. The RSSI output has an excellent linear range of 90dB. The characteristic of RSSI output voltage versus input IF power is independent of temperature and process variation. The nominal output impedance is 3.8kΩ. An off-chip capacitor C7 is needed to reduce the RSSI voltage ripple. Its value can be determined using the following formula: C7 ≥ 1 F 760π • fIF matched in gain response and group delay. The 3dB corner frequency is 7.7MHz and the group delay ripple is 16.4ns. The I/Q differential outputs have output driving capability of 1.5kΩ with maximum capacitive loading of 10pF. The outputs are internally biased at VCC –1.16V. Figure 2 shows the simplified output circuit schematic of I-channel or Q-channnel. VCC I-CHANNEL (OR Q-CHANNEL): DIFFERENTIAL SIGNALS FROM LPF IOUT+ (OR QOUT+) IOUT– (OR QOUT–) I/Q Demodulators The quadrature demodulators are double balanced mixers, down converting the limited IF signals from the IF Limiter into I/Q baseband signals. The quadrature LO carriers are obtained from the internal quadrature LO carrier generator. The nominal output voltage of differential I/Q baseband signals is about 850mVP-P. These magnitudes are well matched, and their phases are 90° apart. Quadrature LO Carrier Generator The quadrature LO carrier generator consists of a divideby-two circuit and LO buffers. An input signal (2XLO) with twice the desired LO carrier frequency is used as the clock for the divide-by-two circuit, producing the quadrature LO carriers for the demodulators. The outputs are buffered and then drive the down converting mixers. With a full differential approach, the quadrature LO carriers are well matched. Integrated Low Pass Filters The 5th order integrated lowpass filters are used for filtering the down converted baseband outputs for both the I-channel and the Q-channel. They serve as antialiasing and pulse-shaping filters. The I/Q filters are well + + 200µA – 200µA – 5502 F02 Figure 2. Simplified Circuit Schematic of I-Channel (or Q-Channel) Outputs The I/Q baseband outputs can be directly DC-coupled to the inputs of a baseband chip. For AC-coupled applications with large coupling capacitors, the STBY pin can be used to prebias the outputs to the desired quiescent voltage at much reduced current. This mode only draws 2.6mA. When the EN pin is then turned on, the chip is quickly switched to normal operating mode without long time constants due to charging or discharging the large coupling capacitors. Table 2 shows the logic of the EN pin and STBY pin. In both normal operating mode and standby mode, the maximum discharging current is about 200µA, and the maximum charging current is more than 10mA. Table 2. The logic of different operating modes EN STBY Comments Low Low Shutdown Mode Low High Standby Mode High Low or High Normal Operation Mode 7 LT5502 U TYPICAL APPLICATIO S IOUT+ R8 51.1k J2 R7 49.9 + U2 LT1809CS 6 IOUT – 4 R10 5.11k J1 IFIN C24 10µF C25 10µF C20 1µF C14 1µF VCC1 3 C1 1µF 2 R6 2.55k C11 1µF C12 1.8pF C5 22nF 1:4 MINI-CIRCUIT R2 20k 1 2 3 4 5 6 7 8 9 10 11 12 IOUT+ IOUT– C2 1nF R12 C15 2.55k 1µF U1 LT5502 GND VCC GND IF + IF – GND GND EN STBY IFt + 2 ÷2 QOUT+ QOUT– VCC GND GND 2XLO+ 2XLO – VCC VCC RSSI GND IFt – 24 23 22 21 20 19 18 17 16 15 14 13 VCC2 1 = EN 2 = STBY C23 1µF R1 20k – 6 R16 49.9 4 R13 5.11k 6 RSSI C18 1µF L1 5502 F02 Figure 3. Evaluation Circuit Schematic With I/Q Output Buffers J3 QOUT R4 240Ω C19 22nF 8 C17 1µF U3 LT1809CS T2 JTX-4-10T C4 1nF IF INTERSTAGE R17 OPTIONAL CIRCUIT 7 + C16 1.8pF C3 1nF C8 SW1 R15 51.1k R14 51.1k 3 T1 JTX-4-10T 6 1 R3 240Ω C9 1µF R9 51.1k QOUT+ QOUT– VCC2 C10 1µF 7 C13 1µF IOUT– C7 1.8pF 1 4:1 MINI-CIRCUIT J4 2XLO LT5502 U TYPICAL APPLICATIO S Figure 4.Component Side Silkscreen of Evaluation Board Figure 5. Component Side Layout of Evaluation Board 9 LT5502 U TYPICAL APPLICATIO S Figure 6.Bottom Side Silkscreen of Evaluation Board Figure 7. Bottom Side Layout of Evaluation Board 10 LT5502 U PACKAGE DESCRIPTIO Dimensions in inches (millimeters) unless otherwise noted. GN Package 24-Lead Plastic SSOP (Narrow 0.150) (LTC DWG # 05-08-1641) 0.337 – 0.344* (8.560 – 8.738) 24 23 22 21 20 19 18 17 16 15 1413 0.229 – 0.244 (5.817 – 6.198) 0.150 – 0.157** (3.810 – 3.988) 1 0.015 ± 0.004 × 45° (0.38 ± 0.10) 0.007 – 0.0098 (0.178 – 0.249) 0.033 (0.838) REF 2 3 4 5 6 7 8 0.053 – 0.068 (1.351 – 1.727) 9 10 11 12 0.004 – 0.0098 (0.102 – 0.249) 0° – 8° TYP 0.016 – 0.050 (0.406 – 1.270) * DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE ** DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE 0.008 – 0.012 (0.203 – 0.305) 0.0250 (0.635) BSC GN24 (SSOP) 1098 11 LT5502 U TYPICAL APPLICATIO Example: 2.4GHz to 2.5GHz Receiver Application (RX IF = 280MHz) 2V 100pF 0.1µF 12 RX INPUT: 2.4GHz TO 2.5GHz 280MHz IF SAW BP FILTER 3.3pF RX FRONT END 1st LO, 2.12GHz TO 2.22GHz VCC 4,16,17,22 13 I 1 OUTPUTS 2 I MIXER 22nF 6 7 LIMITER 1 LIMITER 2 LO BUFFER 90° LPF Q MIXER LPF 3.3pF 11 10 19 1nF 1.8pF IF SYNTHESIZER A/D BUFFER STBY EN LT5502 18 3,5,8,9, 14,20,21 1nF BUFFER Q 24 OUTPUTS 23 f/2 RSSI 15 A/D 0° 120nH MAIN SYNTHESIZER BASEBAND PROCESSOR 2.7pF 30nH 2nd LO, 560MHz 200Ω 30nH 2.7pF 5502 TA02 12 Linear Technology Corporation 5502f LT/TP 0101 2K • PRINTED IN USA (408)432-1900 ● FAX: (408) 434-0507 ● www.linear-tech.com LINEAR TECHNOLOGY CORPORATION 2001 1630 McCarthy Blvd., Milpitas, CA 95035-7417