Source/Drain Parasitic Resistance Role and Electric Coupling Effect

advertisement

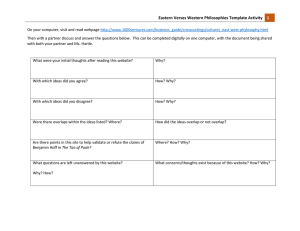

Source/Drain Parasitic Resistance Role and Electric Coupling Effect in Sub 50 nm MOSFET Design 9/25/2002 Jun Yuan, Peter M. Zeitzoff*, and Jason C.S. Woo Department of Electrical Engineering University of California, Los Angeles * SEMATECH, Austin, TX Outline Introduction Simulated Device Structure Source/Drain Engineering Contact Depth Effect in S/D Region Conclusions Introduction MOSFET device performance is determined by carrier transportation, Source/Drain (S/D) electrostatic coupling, and parasitic resistance/capacitance effects Critical parameters for digital: Ion / Ioff, DIBL, C*V/I MOSFET is driven into nanoscale regime 2 Carrier transportation is enhanced Õ velocity overshoot 2 Worse SCE Õ increased S/D electrostatic coupling effect P Scaled down S/D junction depth ¼ S/D series resistance limitation Introduction (cont) P Reduce gate oxide thickness to enhance gate controllability ¼ gate tunneling limitation P Increase substrate doping to reduce S/D electric coupling ¼ Carrier mobility Ð, B-B tunneling and junction capacitance Ï 2 R con / R c h is increased Õ L g & T ox Ð, contact area Ð P look for new material to reduce schottky barrier height (Φ B) The purpose of this work is to study parasitic resistance role and S/D electric coupling effect in 45nm NMOS design, thus provide guideline for further scaling down of conventional bulk device Outline Introduction Simulated Device Structure Source/Drain Engineering Contact Depth Effect in S/D Region Conclusions Simulated Device Structure (NMOS) Lgate = 45nm POLY contact contact Source Drain SDE offset region Lm = 30nm Tgate,eq = 0.8nm Kgate = 25 Xje = 15nm Xjc = 45nm Si substrate n- = 1~5x1019/cm3 n+ = 3x1020/cm3 •Abrupt junction is defined since hot carrier effect is not an issue • SILVACO tool is used with energy balance model Outline Introduction Simulated Device Structure Source/Drain Engineering Contact Depth Effect in S/D Region Conclusions S/D Extension Doping Effect 700 110 650 100 •ρc = 1.2x10-7Ω/µm2 600 Ion (µA/µm) 500 80 450 70 400 •Ioff=10 nA/µm Ion,offset=0nm Ion,offset=7.5nm 50 DIBL,offset=0nm DIBL,offset=7.5nm 300 10 •Vdd=0.8 V 60 350 250 DIBL (mv/v) 90 550 18 10 19 10 40 20 -3 Extension doping concentration (cm , log) SCE is very sensitive to SDE doping (1x1019cm-3 ~1x1020cm-3) SDE doping in nonzero offset region is critical to series resistance S/D Extension Offset Length Effect 130 550 120 100 1.00 90 80 450 70 60 400 19 350 -10 -3 Ion,SDE=5x10 cm 19 -3 Ion,SDE=1x10 cm 19 -3 DIBL,SDE=5x10 cm 19 -3 DIBL,SDE=1x10 cm -5 0 50 40 30 5 10 15 Normalied C*V/I 1.05 DIBl (mv/v) Ion (µA/µm) 500 110 19 -3 19 -3 Next=5x10 cm Next=1x10 cm 0.95 0.90 0.85 0.80 0.75 -10 -5 0 5 10 15 20 Extension offset length (nm) 20 Extension offset length (nm) S/D series resistance is increased with SDE offset length increment DIBL can be decoupled from deep S/D region with large spacer design Device with low SDE doping but zero offset length design can improve Ion , DIBL and C*V/I SDE-to-Gate Overlap Depth/Length Effect 650 19 -3 19 -3 Ion,Next=1x10 cm Ion,Next=5x10 cm 600 Ioff=10nA/µm 95 100 600 90 550 500 Ioff=10nA/µm 450 80 400 DIBL (mv/v) 90 DIBL (mv/v) 85 550 80 500 75 70 450 19 65 70 350 19 -3 19 -3 DIBL,Next=1x10 cm DIBL,Next=5x10 cm 300 0 50 100 150 200 60 19 55 60 -3 DIBL, doping=1x10 cm 19 -3 DIBL, doping=5x10 cm 19 -3 Ion, doping=1x10 cm -3 Ion, doping=5x10 cm 0 Extension junction depth (Α) Drive current is independent of SDE-togate overlap depth/length due to trade-off between Vth and overlap resistance SDE-to-gate overlap can be eliminated to reduce SCE and overlap capacitance 25 50 400 350 75 SDE-to-Gate overlap length (A) POLY Source ~ ~ Ion (µA/µm) Ion (µA/µm) 650 100 110 Zero & Nonzero Gate-to-SDE overlap Device Performance Comparison (1) with ext. overlap without ext. overlap 650 650 600 550 550 500 450 400 350 300 •Lg=500nm 250 200 •Lg=45nm 500 with ext. overlap without ext. overlap 600 Drain current (µA/µm) Drain current (µA/µm) 700 -9 10 -8 10 -7 10 -6 10 leakage current (A/µm) 450 -9 10 10 -8 10 -7 10 -6 Leakage current (A/µm) Long channel: device with overlap has higher current drive due to smaller effective channel length, Ion ∝ Leff-1 Short channel: Similar Ion /Ioff performance due to velocity saturation and SCE limitation Zero & Nonzero Gate-to-SDE Overlap Device Performance Comparison (2) 1.05 with ext. overlap without ext. overlap 1.1 0.9 0.95 0.90 0.85 0.8 0.7 0.6 0.5 0.4 0.80 0.75 -9 10 with ext. overlap without ext. overlap 1.0 normalized C*V/I normalized C*V/I 1.00 0.3 •Lg=45nm •Lg=500nm -9 10 -8 10 -7 10 -6 10 leakage current (A/µm) 10 -8 10 -7 10 -6 leakage current (A/µm) Long channel: SDE-to-Gate overlap improves device intrinsic speed due to enhanced drive current Short channel: SDE-to-Gate overlap degrades device speed due to increased overlap capacitance 92 90 88 86 84 82 80 78 76 74 72 70 68 66 64 62 60 58 640 Ioff=10nA/µm contact 620 POLY ~ ~ POLY ~ ~ 600 Source 580 560 540 520 DIBL, doping=3x10 cm 21 -3 DIBL, doping=3x10 cm 20 -3 Ion, doping=3x10 cm 500 Ion, doping=3x10 cm 460 20 21 100 200 300 400 500 -3 -3 Ion (µA/µm) DIBL (mv/v) Deep S/D Junction Depth Effect 480 Source 600 deep S/D junction depth (A) •Shallow and highly doped Source/Drain is needed for high drive current and low DIBL Outline Introduction Simulated device structure Source/Drain Engineering Contact depth effect in S/D region Conclusions Source/Drain contact resistance S Contact resistance can be major parasitic resistance component in nanoscale MOSFET device S Contact resistance can be reduced by increasing silicide interface doping concentration and reducing schottky barrier height ΦB: ρc ∝ Exp( ΦB*√ε / Nd ) S Recessed contact depth effect on contact resistance 2 Long contact limit device: silicide-diffusion resistance is increased with contact depth increment in S/D region 2How about in short contact limit device ? Recessed Contact Depth Effect spacer 720 Drain Current (µA/µm) 690 gate Silicide 660 630 600 Ion (µA/µm) 570 540 Junction 0 100 200 300 400 Contact electrode depth in source/Drain region (A) Unlike long contact limit case, Current drive capability is enhanced by increased contact depth in S/D region for short contact limit device Reason: current flows to both bottom and side of contact electrode Optimized MOSFET Bulk Device POLY contact contact Source Drain Si substrate Device structure is optimized based on S/D series resistance, short channel effect and recessed contact depth effect Bulk device can be further scaled down below 45nm Outline Introduction Simulated Device Structure Source/Drain Engineering Contact Depth Effect in S/D Region Conclusions Conclusions MOSFET Short Channel Effect is Source/Drain (S/D) electrostatic coupling result SCE is sensitive to SDE doping and junction depth, but it can be de-coupled from deep S/D region Doping concentration and length in SDE offset region is critical to S/D series resistance Shallow and highly doped S/D is expected for both Ion and DIBL Conclusions Unlike long channel device, SDE-to-Gate overlap in nanoscale device can be eliminated without degrading Ion/Ioff performance due to velocity saturation limitation and S/D electric coupling effect Zero SDE-to-Gate overlap design can improve device speed in nanoscale MOSFET device Increased contact electrode depth in S/D region can enhance drive current in short contact limit case due to increased current spreading