MICRO/NANO HIERARCHICAL STRUCTURE IN MICROCHANNEL

advertisement

MICRO/NANO HIERA

ARCHICAL STRUCTURE IN MICR

ROCHANNEL

HEAT SINK FOR BOILING ENHANCEMENT

Z.Yao1, Y-W. Lu2 and S.G. Kandlikar1

1

Rochester Institute of Technology, Rochester, NY, USA

A

2

National Taiwan University, Taipei, Taiwan

studied and it is found that byy creating uniform SiNW

arrays in the microchannel, the surface hierarchy is capable

of providing a significant high heat flux at low wall

superheat.

ABSTRACT

Uniform SiNW structures were fabrricated for the first

time on the top, bottom and sidew

wall surfaces of

microchannel heat sinks by using a twoo-step electro-less

etching process. The micro/nano hierrarchical structure

yields superior boiling heat transfer performance.

p

Its

maximum heat flux is improved byy 150% over the

microchannel-only heat sink and 400% over

o

a plain silicon

surface. These results provide a new

w insight into the

boiling mechanism for microchannel heat sinks using

hierarchical structures.

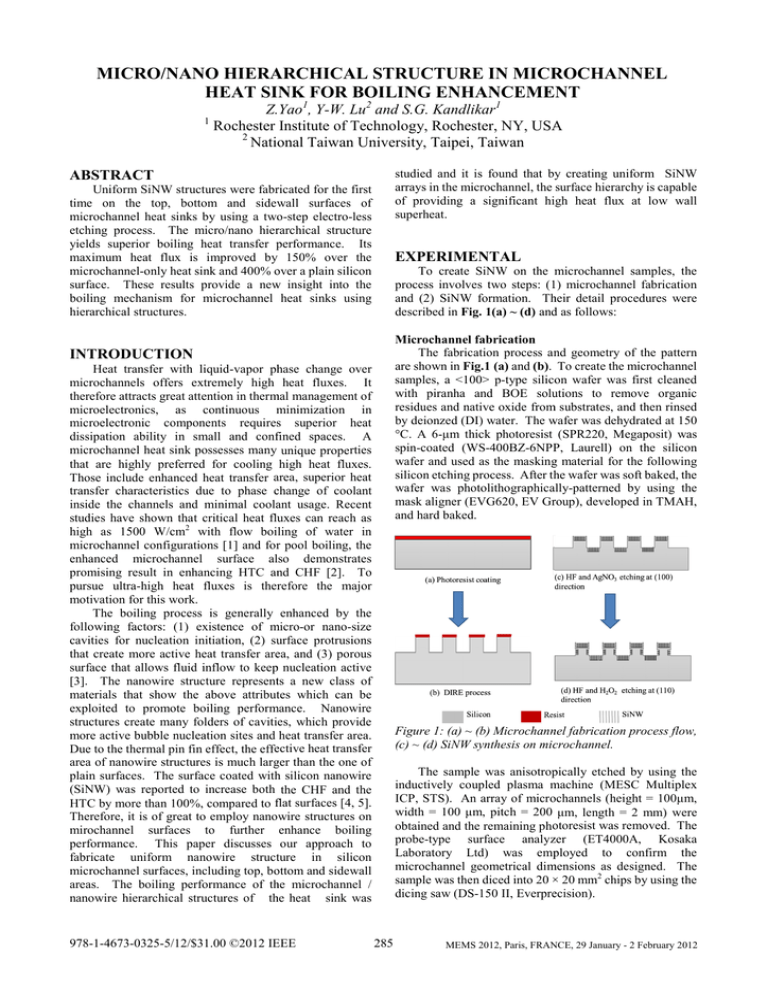

EXPERIMENTAL

To create SiNW on the microchannel

m

samples, the

process involves two steps: (11) microchannel fabrication

and (2) SiNW formation. Thheir detail procedures were

described in Fig. 1(a) ~ (d) andd as follows:

Microchannel fabrication

The fabrication process annd geometry of the pattern

are shown in Fig.1 (a) and (b). To create the microchannel

samples, a <100> p-type silicoon wafer was first cleaned

with piranha and BOE soluutions to remove organic

residues and native oxide from

m substrates, and then rinsed

by deionzed (DI) water. The wafer

w

was dehydrated at 150

°C. A 6-μm thick photoresist (SPR220, Megaposit) was

P, Laurell) on the silicon

spin-coated (WS-400BZ-6NPP

wafer and used as the maskingg material for the following

silicon etching process. After thhe wafer was soft baked, the

wafer was photolithographicaally-patterned by using the

mask aligner (EVG620, EV Grroup), developed in TMAH,

and hard baked.

INTRODUCTION

Heat transfer with liquid-vapor phhase change over

microchannels offers extremely high heat fluxes. It

mal management of

therefore attracts great attention in therm

microelectronics, as continuous minimization

m

in

microelectronic components requiress superior heat

dissipation ability in small and conffined spaces. A

microchannel heat sink possesses many unique properties

that are highly preferred for cooling high heat fluxes.

a

superior heat

Those include enhanced heat transfer area,

transfer characteristics due to phase change

c

of coolant

inside the channels and minimal coolaant usage. Recent

studies have shown that critical heat fluuxes can reach as

high as 1500 W/cm2 with flow boiling of water in

microchannel configurations [1] and forr pool boiling, the

enhanced microchannel surface allso demonstrates

promising result in enhancing HTC annd CHF [2]. To

pursue ultra-high heat fluxes is therrefore the major

motivation for this work.

The boiling process is generally enhanced by the

m

nano-size

following factors: (1) existence of micro-or

cavities for nucleation initiation, (2) suurface protrusions

that create more active heat transfer areea, and (3) porous

surface that allows fluid inflow to keepp nucleation active

[3]. The nanowire structure representts a new class of

materials that show the above attributtes which can be

exploited to promote boiling perform

mance. Nanowire

structures create many folders of cavities, which provide

more active bubble nucleation sites and heat transfer area.

Due to the thermal pin fin effect, the effeective heat transfer

area of nanowire structures is much largger than the one of

plain surfaces. The surface coated withh silicon nanowire

(SiNW) was reported to increase both the CHF and the

f surfaces [4, 5].

HTC by more than 100%, compared to flat

Therefore, it is of great to employ nanowire structures on

mirochannel surfaces to further enhance boiling

performance. This paper discusses our approach to

fabricate uniform nanowire structture in silicon

microchannel surfaces, including top, boottom and sidewall

areas. The boiling performance of thhe microchannel /

nanowire hierarchical structures of thhe heat sink was

978-1-4673-0325-5/12/$31.00 ©2012 IEEE

Figure 1: (a) ~ (b) Microchannnel fabrication process flow,

(c) ~ (d) SiNW synthesis on miccrochannel.

The sample was anisotroppically etched by using the

inductively coupled plasma machine

m

(MESC Multiplex

ICP, STS). An array of microochannels (height = 100μm,

width = 100 μm, pitch = 200 μm, length = 2 mm) were

obtained and the remaining phootoresist was removed. The

probe-type surface analyzzer (ET4000A, Kosaka

Laboratory Ltd) was empployed to confirm the

microchannel geometrical dim

mensions as designed. The

sample was then diced into 20 × 20 mm2 chips by using the

dicing saw (DS-150 II, Everpreecision).

285

MEMS 2012, Paris, FRANCE, 29 January - 2 February 2012

top and bottom areas, as theey are created at different

etching steps. At the top andd bottom area, cavities and

openings were observed between

b

SiNW bundles,

providing ideal active bubblee nucleation sites for pool

boiling. The SiNW structure att the sidewall area enhanced

active heat transfer area annd functioned as wicking

structure to provide capillary foorce. The average height of

SiNW on top/bottom surface is about 10 ~ 15 µm with a

diameter ranging from 10 ~ 50 nm. For SiNW on sidewall

surface, the average height is 100 µm with a diameter of ~80

nm.

SiNW fabrication on Microchannel

S

electroless

Our SiNW process facilitated SiNW

etching processes. In general, this SiNW

W etching process

was crystalline-direction dependent; it haad different SiNW

formation when different etching condittions were applied

[7]. Therefore, a two-step etching process was necessary

when there were more than one crystalliine direction in the

microchannel samples – <100> crystallinne direction for the

top and bottom of the microchannel annd <110> for the

sidewall of the microchannel when a {1000} silicon wafer is

used. As shown in Fig. 1 (c) and (d)), our first SiNW

etching step promoted the SiNW etchhing at the <100>

direction, which was realized by immerssing the samples in

5M HF and 0.02 M AgNO3 at room tem

mperature. In this

etching step, the deposited Ag+ was redduced into Ag0 by

injecting positive holes (h+) into the bulkk silicon because of

the high positive redox level of Ag/A

Ag+. Silicon was

oxidized into SiO2 and consequently dissolved by HF. As

the SiO2 removal was associated with the number of its

back bonds and the density of back bonds

b

in different

crystal planes increased with the order of

{100}<{110}<{111}. Therefore, at the equilibrium state,

the etching preferred <100> direction, where least back

bonds to break, results in SiNW onnly in the <100>

direction, as shown in Fig. 2(a). The siidewall surface of

{110} was little affected in the first etchiing step.

Surface wettability

r

to enhance the

SiNW structure was reported

wettability on plain silicon surffaces [8]. By improving the

hydrophilicity, bubble nucleatiion during the pool boiling

process is promoted and the CHF

C

is increased to prevent

dry out. The micro/nano hierarchy

h

demonstrates the

hydrophilic property (contact anngle ~ 0), as indicated in the

contact angle measurement in Fig.

F 3. 2 µL droplets of DI

water were dispensed on microchannel-only and

microchannel with SiNW suurfaces, respectively. For

microchannel-only surface, thee measured contact angle of

water is 150°, as the droplet waas suspended by the air-gap

inside the channel. For the microchannel with SiNW

surface, the droplet spreads throough and across the channel

surface, showing completely-w

wetting property.

Figure 3: Contact angle of (a)) microchannel surface and

(b) microchannel with SiNW suurface

The surface hydrophiliciity may attribute to the

capillary wicking induced by the

t micro/nano hierarchical

structure. The capillary wickiing supplies fresh liquid to

the dry region beneath the vappor bubbles during boiling,

delaying the irreversible growthh of hot spots and CHF.

Pool boiling test setup

To study the pool boiiling performance of the

hierarchical structure, an expperimental setup shown in

Fig.4 was employed [8]. The test

t samples were mounted

on an insulated and sealed coppper block. A 450 W capacity

cartridge heater served as thhe major heating element.

Three K-type thermocouples, placed

p

along the axis of the

copper block, were used to measure the temperature

gradient through the top of the heater. The thermocouples

were 8 mm apart and the first onne (T1) was 3 mm below the

top copper surface. DI wateer was used as the boiling

liquid. Sufficient time was givven to remove dissolved air

before commencing the test. Periodically between the tests,

p

for replenishment. An

more water was added to the pool

auxiliary heater (100W) was used

u

to maintain the water

temperature in the reservoir at 100°C. The temperature of

water was monitored by a K-typpe thermocouple (T4). After

water was kept in saturation teemperature for 30 min, the

Figure 2: SEM images of (a) microchannnel sidewall area

after the 1st etching step, (b) sidewall area after the 2nd

etching step, (c) top area after the 2nd ettching step and (d)

bottom area after the 2nd etching step.

To create SiNW on the sidewall witthout affecting the

structure in the other areas, H2O2 was introduced in the

second NW etching step to alter the etchhing direction into

<110>. The solution contained HF/H2O2 with 2:1 molar

ratio. High concentration of H2O2 wouuld generate large

amount of holes (h+) and significantlyy speeded up the

removal of silicon atoms in the crystal planes,

p

where there

were more silicon back bonds than {100}} plane to polarize,

resulting in SiNW forming at the <110> direction.

d

Uniform

SiNW structures on the sidewall, top annd bottom areas of

the microchannels were successfully fabbricated thereafter,

as shown in Fig. 2(b) ~ (d). The SiNW

W branches at the

sidewall surface were slightly different from the ones on

286

main heater was started and the powerr was increased in

small increment. A LabView program

m was created to

display temperatures, determining w

when the system

reached a steady-state, and record the meeasurement data.

RESULTS AND DISUSS

SION

The boiling characterrization of micro/nano

hierarchical structure in miccrochannel heat sink was

depicted in Fig. 5. The heat flux value was calculated

based on the projected miccrochannel area. Boiling

performance on the plain siliccon substrate was obtained

and served as the primary conntrol for comparing boiling

performance.

For microchannel-only sample, the

maximum heat flux recorded is 110 W/cm2 at 35K wall

S

in the microchannel

superheat. By incorporating SiNW

heat sink, the boiling incipieent wall superheat on the

surface was found to be much lower

l

than that on the plain

silicon surface as well as on

o the microchannel-only

surface.

Figure 4: Schematic of boiling test fixtuure (a) Cartridge

heater, (b) Ceramic block, (c) Testing chhip, (d) Gasket, (e)

Polycarbonate visualization tube, (f) Auuxiliary heater, (g)

K-type thermocouples, (h) Data acquuisition system, (i)

Compression screws, (j) High speed camera and (k)

Power supply.

The heat flux was calculated froom the following

equation:

dT

(1)

dx

The temperature gradient, dT/dx, was ccalculated using a

three-point

backward-difference

Taylor

series

approximation showing below,

q ' ' = −kcu

dT 3T1 − 4T2 + T3

=

dx

2Δx

Figure 5: Boiling characterizaation of microchannel with

SiNW surface, microchannel only surface and plain Si

surface.

(2)

m heat flux of micro/nano

Particularly, the maximum

2

hierarchy surface reached 164 W/cm

W

at 24 K superheat, an

improvement of 150% over thee microchannel-only surface

and 400% over a plain silicon surface. The heat transfer

coefficient at 24K wall superrheat is 54.2 kW/m2·K for

micro/nano hierarchy surfacee and 24.9 kW/m2·K for

microchannel only surface, reppresenting more than 200%

improvement. Those results are also among the highest

m

that, the chosen

values. It is worthy to mention

microchannel pattern may not be

b the best configuration for

boiling heat transfer; therefore, by optimizing the

microchannel configuration, thhe boiling performance can

be further improved.

This study demonstrates thhat uniform SiNW structure

can be created on microchannnel heat sink surfaces by a

two-step etching process. Thee pool boiling heat transfer

performance can be signifiicantly enhanced by the

microchannel/nanowire hierarcchical structures. The SiNW

enhanced the surface wettabilitty of the microchannel. The

main findings of this study are summarized as follows:

where T1, T2 and T3 are the temperatuures measured by

thermocouples located at distances Δx = 8mm. The

surface temperature of the microchannell, Ts, was obtained

by calculating the heat flux through thee copper block, as

well as the reading from thermocoupple T1, from the

following equation,

Ts = T1 − q" (

LCu

L

+ Rt",c + Si )

K Cu

K Si

(3)

where L and K represent material thickkness and thermal

conductivity, respectively. R”t,c repressents the thermal

contat resistance of the interface, whicch is found to be

repeatedly 5 × 10-6 m2·K/W, with an unncertainty less than

4%, as calculated in our previous studdy [2]. The wall

superheat ΔT is therefore obtained by

ΔT = Ts − Tsat

(4)

1.

For boiling with water at standard atmosphere, the

saturation temperature Tsat = 100°C.

287

A two-step synthesis proccess is developed to create

uniform SiNW on the micrrochannel surface, including

top, bottom and sidewall areas.

a

The average height of

SiNW on the surface is aroound 10~15 µm.

2.

3.

4.

The SiNW structures enhanced the surface wettability,

making the microchannel surface super-hydrophilic.

The testing results suggested that for pool boiling with

water on the microchannel heat sink, heat transfer can

be significantly enhanced by creating micro/nano

hierarchical structures on the testing surfaces.

The current silicon microchannel sample with SiNW

structure yielded a heat flux of 164 W/cm2 at 24K wall

superheat.

This result is 400% improvement,

compared to the plain silicon surface sample at the

same wall superheat region. The boiling performance

can be further enhanced by optimizing the

microchannel configuration.

REFERENCES

[1] G.P.Celata, M. Cumo, M.A. Mariani, “Geometrical

Effects on Sub-cooled Flow Boiling Critical Heat

Flux”, Rev. Gen. Therm. 36, pp.807-814, 1997

[2] D. Cooke, S.G. Kandlikar, “Pool Boiling Heat Transfer

and Bubble Dynamics over Plain and Enhanced

Microchannels”, ASME J. Heat Trans, 133, pp.

052912-052919, 2011.

[3] T.J. Hendricks, S. Krishnan, C. Choi, C-H. Chang, B.

Paul, “Enhancement of Pool Boiling Heat Transfer

using Nanostructured Surfaces on Aluminum and

Copper”, Int. J. Heat Mass Tran, 53, pp.3357-3365,

2010.

[4] R. Chen, M. C. Lu, V. Srinivasan, Z. Wang, H. H. Cho,

and A. Majumdar, “Nanowires for Enhanced Boiling

Heat Transfer”, Nano Lett. 9, pp. 548-553, 2009.

[5] Y.Im, Y.Joshi, C.Dietz and S.S.Lee, “Enhanced

Boiling of a Dielectric Liquid on Copper Nanowire

Surfaces”, Int. J. Micro-Nano Scale Transport, 1,

pp.79-95, 2010.

[6] Y.-W. Lu and S. G. Kandlikar, “Nanoscale Surface

Modification

Techniques

for

Pool

Boiling

Enhancement — A Critical Review and Future

Directions”, Heat Trans Eng, 32, pp. 827-842, 2011.

[7] Jungkil Kim, Young Heon Kim, Suk-Ho Choi, Woo

Lee, “Curved Silicon Nanowires with Ribbon-like

Cross Sections by Metal-Assisted Chemical Etching”,

ACS Nano, 5, pp 5242–5248, 2011.

[8] Z.Yao, Y-W. Lu, S.G. Kandlikar, “Effects of Nanowire

Height on Pool Boiling Performance of Water on

Silicon Chips”, Int. J. Therm. Sci., 50, pp. 2084-2090,

2011.

Silicon is the most commonly used material in the

semiconductor industry. The micro/nano hierarchical

structure employed here are ready for future

semiconductor cooling, thermal management and

high-heat-flux energy conversion applications. The study

of micro/nano-scale structure on pool boiling provides a

new insight on effectively enhancing boiling heat transfer.

ACKNOWLEDGEMENT

We thank Mr. P.C. Kao from National Taiwan

University for preparing the microchannel samples. The

collaborative project has been supported by National

Science Council (NSC98-2218-E002-023-MY3) and

National Science Foundation EPDT Grant (# 0802100).

CONTACTS

1

S.G.Kandlikar, sgkeme@rit.edu;

Y-W. Lu, yenwenlu@ntu.edu.tw

2

288