• For single-crystal silicon, each silicon atom has four nearest

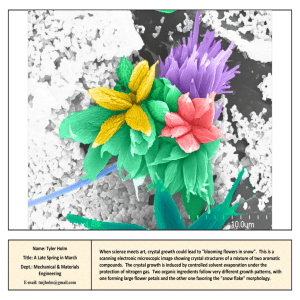

advertisement

• For single-crystal silicon, each silicon atom has four nearest neighbors. Since Si is a column IV element and has four valence electrons, each of these electrons is shared with one of its four nearest neighbor Si atoms. • This nearest neighbor atom likewise contributes one of its electrons to the bond. • The two valence electrons shared between nearest neighbors form a covalent bond, and such interactions of electrons in neighboring atoms of a solid serve the function of holding the crystal together. • Since all the valence electrons in a perfect Si crystal are involved in shared bonding pairs, none are available as free electrons for conducting electrical current (as long as they remain localized in the bonding region). • Such covalently bonded electrons can, however, be thermally or optically excited, and thereby become free to participate in conduction. • when dopant atoms (mostly from Group III or V) are substituted for Si atoms in the crystal lattice, they are said to occupy substitutional lattice sites. • Such dopants can also become the source of additional conduction electrons or holes. For example, phosphorus is a substitutional donor, because four of its valence electrons become covalently bonded with other Si atoms but, the fifth valence electron is easily separated, and once free, becomes available to conduct current. • Group III elements (e.g. boron, aluminum) are substitutional acceptors, and become sites leading to hole conduction. • Atoms that do not occupy lattice sites are described as occupying interstitial (e.g. between lattice sites) sites. 1 MANUFACTURE OF SINGLE CRYSTAL SILICON • The fabrication of integrated circuits utilizes silicon substrates possessing very high crystalline perfection. • Polycrystalline material would exhibit inadequately short minority carrier lifetimes, due to the defects occurring at the grain boundaries of the polycrystalline grains. • The method of obtaining such single crystal Si for VLSI fabrication, involves two steps: 1) Raw material (e.g. quartzite, a type of sand), is refined by a complex, multistage process which produces electronic grade polysilicon (EGS), 2) This polysilicon is used to grow single crystal silicon by Czochralski (CZ) crystal growth or float zone (FZ) growth. In CZ growth, single crystal ingots are pulled from molten silicon contained in a crucible. • Czochralski silicon is preferred for VLSI applications since it can withstand thermal stresses better than FZ material and it is able to offer an internal gettering mechanism that can remove unwanted impurities. • With the FZ process, ingots are grown without making contact to any container or crucible and can attain higher purity (and thereby higher resistivity). • Devices and circuits calling for high purity starting material (e.g. high voltage, high power devices) are typically fabricated from FZ silicon. 2 • Silicon (Si) is presently the most important semiconductor for the electronics industry, since integrated circuit technology is almost entirely on silicon. • The name silicon comes from the Latin silex or silicas meaning flint. • Second in abundance only to oxygen silicon comprises 25.7% of the earth’s crust. • Solid-state electronics was launched w1t11 the invention of the bipolar transistor by Bardeen, Brattain, and Shockley in 1947. • Germanium (Ge) was the original semiconductor material used to fabricate diodes and transistors but the narrow bandgap of Ge (0.66 eV), however, greatly limits the useful temperature range devices fabricated with this element. • The larger bandgap of silicon (1.1 eV) results in smaller leakage currents and thereby allows silicon devices to be built with a maximum operating temperature of abut 150@C. • The oxide of silicon SiO2, is also easy to form and is chemically very stable. • Electronic grade silicon is about one tenth as costly as germanium. 3 From Raw Material To Electronic Grade Polysilicon • Single crystal silicon is grown from melts of electronic grade polycrystalline silicon (EGS). • The CZ process (which is used to grow most single crystal silicon) adds impurities to the resultant ingot, the EGS must be extraordinarily pure. • In order to achieve controlled doping during subsequent single crystal growth, EGS must have impurity levels in the parts per billion atoms range. • This is the purest material routinely available on earth. • The raw material from which EGS is refined (quartzite) contains high levels of impurities the process must reduce impurities by approximately eight orders of magnitude! • This procedure involves four major stages : 1) Reduction of quartzite to metallurgical grade silicon (MGS) with a purity of approximately 98%, 2) Conversion of MGS to trichloroethane (SiHCl3), 3) Purification of SGCI by distillation, 4) Chemical valor deposition (CVD) of Si from the purified SiHCl3, as EGS. • In Step 1, SiO2 in the form of quartzite is reacted with carbon to yield silicon and carbon monoxide: SiO2 + 2C => 4 Si + 2 CO • Quartzite is a relatively pure form of SiO2 that occurs in nature. In the presence of carbon (in the form of coal, coke, or wood chips), it is reduced to MGS. • The name MGS is derived from the fact that silicon with this purity (~98%) is sufficiently refined to be used as an alloy material in the manufacture of aluminum or for producing silicone polymers. 4 • Most silicon manufactured every year is consume by such applications, and only a small fraction is further refined into EGS for electronic applications. 5 • Quartzite and coal, coke, or wood chips are loaded into a submerged electrode arc furnace. • Temperatures within the electric arcs that are generated between the furnace electrodes exceeds 2000°° C, forming SiC. • The SiC reacts with SiO2 to form Si, SiO, and CO. • Molten silicon is drawn off while the Sic and CO gases escape. • Large quantities of electrical power are consumed in producing the reaction (12-14 kWh /kg). • MGS from this process has Al and Fe as the main impurities. • In Step 2, trichloroethane (SiHCl3) is formed by the reaction of anhydrous hydrogen chloride and MGS. • In this step, the MGS is first ground to a fine powder and treated with HCI to form SiHCl3. • The reaction of the solid Si and the gaseous HCl occurs at 300°°C in the presence of a catalyst. • Both the formation of the SiHCl3 and the chlorides of the impurities takes place in this step. • SiHCl3 is a liquid at room temperatures (boiling point 31.8°° C) which can be purified by distillation. • In Step 3, the SiHCl3 is separated from its impurities by fractional distillation. • The resulting SiHCl3 must be deposited as semiconductor grade polysilicon, then converted to single crystal silicon, and finally measured electrically, in order to determine the impurity levels. • In Step 4, the highly purified SiHCl3 is converted back into polysilicon (EGS) by CVD in the presence of hydrogen in a reactor referred to as the Siemens process. • 2 SiHCl3 (gas) + 2 H2 (gas) => 2 Si (solid) + 6 HCI (gas) 6 • The starting surface is a thin silicon rod (called a slim rod) which serves as a nucleation surface for the depositing silicon. • For large rods (200 mm in diameter and several meters long), the deposition process takes several hundred hours. 7 • After deposition, the EGS is processed into three products: a) One-piece crucible charges; b) Nugget (random sized pieces); and c) Poly-rods . • The first two products are used as charges in the CZ growth of single crystal silicon, while the rest are used for float-zoning single crystal ingots. CZOCHRALSKI (CZ) CRYSTAL GROWTH • Czochralski (CZ) growth, named for its inventor, involves the crystalline solidification of atoms from a liquid phase at an interface. • The basic production process for producing CZ Si has undergone remarkably little change since it was pioneered in the early 1950s. • The simplicity of the process and the relatively high degree of crystal purity helped establish the CZ process as the dominant crystal growing technology in the early years of the semiconductor industry. • The development of dislocation-free ingot growth and automatic diameter control in the late 1960s, lead to a rapid growth in the sizes of ingot diameters and crystal melts. • Further increases in charge size and diameters were driven by the economic advantages of even larger ingots. • Typical commercial ingots are grown 0.5-2.5 m in length, and a 60 kg charge can grow a 150 mm diameter ingot roughly 1 m long. • Current ingot diameters are ~300 mm. Czochralski Crystal Growth Sequence • The steps used in growing a CZ Si crystal include: a) fused silica crucible is first loaded with a charge of undated EGS together with a precise amount of diluted silicon alloy. 8 b) The growth chamber is then pumped out, backfilled with an inert gas (to limit incorporation of atmospheric gases into the melt during growth), and the charge is melted (melting point of silicon is 1421°°C). c) Next, a slim seed crystal of silicon (~5 mm in diameter and 100- 300 mm long) is lowered into the molten silicon. d) The seed crystal is then withdrawn at a controlled rate. • Both the seed crystal and the crucible are rotated during the pulling process, but in opposite directions. • The initial pull rate is relatively rapid so that a thin neck is produced. • At that point the melt temperature is reduced and stabilized so that the desired ingot diameter can be formed (shouldering out step). • This diameter is subsequently maintained by precisely monitoring the pull rate. • The pulling continues until the charge is nearly exhausted, at which point the ingot is withdrawn to form the tang (tail off). • A shutdown procedure of the furnace completes the process. • The initial immersion of the cool seed crystal into the melt sets up very high stresses between the heated crystal exterior and the still cool interior. • These stresses are high enough to cause plastic deformation, and result in macroscopic dislocations in the crystal. • By rapidly pulling a thin necked region from the melt, these dislocations are driven to the cylindrical surface of the neck, and at that point they cease to propagate into the subsequently solidifying crystal regions. • The growing crystal becomes free of macroscopic dislocations and will continue to grow in this way unless a significant perturbation disturbs the solidification process 9 • This tendency for a dislocation-free crystal to continue to grow without dislocations is due to the very high stresses that must be imparted to a perfect crystal in order to create dislocations but are not incurred under well-controlled growth conditions. • As the crystal solidifies and is pulled from the melt, the latent heat of fusion L, is • Dislocations generated at the end of the seed crystal that contacted the molten zone grow out to the side surface of the neck and do not propagate into the main crystal. • Heat is transported from the solid-liquid interface along the growing crystal and lost from the crystal surface due to radiation and convection. • The upper limit of the pull rate is reached when the maximum heat that can lost by the ingot is being transferred to the ingot by the solidifying silicon. • As the diameter of the ingot is increased, the maximum pull-rate must decrease, because the heat loss is proportional to the surface area of the ingot which increases only linearly with the diameter) while the heat gain is promotional to the volume being solidified which increases as the square of the ingot radius. • The actual pull rate is typically 30% to 50% less than the maximum theoretical rate. • Such slower rates result from the effects of a transient temperature increase in the melt which occur near the interface which causes remelt of the crystal and the nominal pull-rate must be reduced until solidification restarts. • When a subsequent temperature reduction takes place, the solidification rate increases, leading to an increase in the ingot diameter. 10 • To maintain the desired diameter, the pull-rate at that instant must be increased. Such temperature oscillations thus lead to pull-rate variations and an overall lower average pull-rate. • Automatic diameter control (ADC) mechanisms control the pull-rate changes to optical diameter measurements. • Several ingot properties are impacted by temperature fluctuations, which include: a) Dimensional variations in the diameter of the ingot. b) Temperature instabilities cause microscopic resistivity variations in both radial and axial directions. • The dislocation-free attribute of CZ crystals refers to macroscopic (edge and screw) dislocations. • Small dislocation laps, however, can be formed during the growth of the main crystal by the condensation of excess point defects as the crystal cools from the solidification temperature (1421°°C) down to abut 950°°C. • During this cooldown, the solubility of the point defects created at temperatures near meltdown is reduced, until the crystal is supersaturated with point defects. • If these point defects can diffuse sufficiently, they will tend to arrive at sites at which they can agglomerate and thereby be removed from solution. • If the pull-rate is high enough, the solidified region cures with sufficient rapidity so that the excess point defects are immobilized or quenched in the lattice and can’t agglomerate. • Interstitial silicon and oxygen have been suggested as the point defect species responsible for forming such agglomerates. 11 • For crystals in which the pull-rate has not been sufficiently high, the presence of the resultant dislocation loops will cause the crystal to exhibit swirl patterns when wafers are subjected to defect-delineation chemical etching. • When CZ silicon crystals were first grown, the process required highly skilled operators to control all the important growth parameters including melt temperature, ingot diameter, pull-rate, and rotation. • Now such parameters are monitored by microcomputers, resulting in more reproducible control of the physical and chemical aspects of the pulling process. • A variety of growth process sequences can be carried out by modern crystal growth systems, with ''one button'' operations that automatically take the system from meltdown to shutdown. • Impurities are incorporated into the CZ crystal as it solidifies, together with the silicon by adding precise amounts of silicon alloy (heavily doped with the impurity of choice) into the crucible with the EGS. • As the silicon solidifies, only a fraction of the impurity concentration that was present in the molten volume that solidified is incorporated into the crystal. • The remaining fraction remains in the melt so that the melt becomes progressively more concentrated with the impurity. (Melt enrichment) • As a result as the ingot grows, the molten material arriving at meltcrystal interface contains an ever-larger proportion of impurity atoms and the ingot also becomes more heavily doped along its length. 12 Czochralski Crystal Growing Equipment The equipment used in the Czochralski process consists of four subsystems. 1) Furnace: crucible, susceptor, rotation mechanism, heater and power supply, and growth chamber. 2) Crystal-pulling mechanism: seed cable or chain, rotation mechanism, seed chuck, and crystal handling device. 3) Ambient control: chamber gas source, flow controller, and vacuum /exhaust system. 4) Control system: computer-based controller: and sensors. • Furnace - The material chosen for CZ silicon crucibles is fused silica which has the properties of high melting point, thermal stability, and of being relatively non-reactive with molten silicon. • The molten silicon to some extent does corrode the fused silica crucible, especially during the higher temperature melt-in period. • Substantial quantities of oxygen and silicon become dissolved into the melt. Some of this oxygen becomes incorporated into the crystal, initially taking the form of an interstitial impurity. • The purity of the crucible silica is also important, since the silica impurities can limit the upper values of resistivity possessed by ingots grown in the crucible (B and P contamination). • Silica has no distinct melting point, but gradually softens with increasing temperature. • Near the melting point of silicon, the silica material of the crucible becomes so soft that it requires the support of a heat resistant and rigid outer crucible (susceptor). 13 • Such susceptors are fabricated from high purity graphite, which exhibits adequate temperature and cleanliness properties. • The other components in the chamber that are subjected to high temperatures are also fashioned from graphite, including the pedestal (on which the susceptor sits, and which can rotate as well as raise or lower the susceptor, heater elements, insulation package. and heat shield. • Carbon contamination of the melt occurs primarily from graphite dust particles, reaction of the hot graphite parts with oxygen introduced from oxygen or water leaking into the chamber and reaction of the susceptor/pedestal with the silica crucible to form CO. • Keeping carbon pieces free of carbon dust, maintaining leak-tight growth systems, and using inert purge gases to swap out any CO gas that may form reduces carbon contamination. • Graphite resistance heaters connected to a dc power supply melt the silicon charge. • Large pullers require tens of kilowatts of power for operation. • The use of CVD-deposited silicon nitride as an alternative crucible material has also been demonstrated. • Nitride crucibles also exhibit some dissolution which causes the crystal to be doped with nitrogen, which behaves as a weak donor in silicon. • Crystal Pulling Mechanism - the mechanism which pulls the crystal from the melt and simultaneously rotates it, must perform this function with minimal vibration and sufficient precision. • Most systems use a cable or chain to pull the crystal, but their major problem is a tendency for the crystal to swing under certain operating conditions. • The process engineer must design the pulling process to avoid these critical conditions. 14 • In larger pullers, the hot crystals have become to large to be manually handled so that crystal unloading fixtures and carts are used to transmit the ingots from the furnace to the cropping and evaluation areas. • Ambient Control - The environment in the chamber must be kept free of reactive gases (O2, CO, etc.). • This is accomplished by continually purging the chamber with an inert gas (e.g. Ar) so that as this gas is pumped out of the chamber by the vacuum system, any contaminating gases such as CO or SiO are also removed. • Growth at a reduced pressure in the chamber can be used to alter evaporation from the melt. • A typical consumption rate of inert gas for this purpose is ~1500 liters/kg of silicon grown. 15 Control System - The process parameters, such as pull-rate, crucible rotation, seed rotation, melt temperature, gas flow, and crystal diameter, are controlled in modern pullers with digital computer systems. • Completely automated cycles (one-button operation) require manual intervention only for loading the crucible with EGS and Recipes that result in various crystal properties are stored in the computer memory, allowing the system to produce nearly identical crystals from run-to-run. • Other control systems features may include central computer interfacing capability, data logging and printing, CRT terminals, and tape or magnetic disk program storage. • Focusing an infrared temperature sensor on the melt-crystal interface, and monitoring changes of the meniscus temperature controls ingot diameters during growth. • The pull-rate mechanism and chamber heater is controlled by the output of the sensor, and the diameter is adjusted by changes in the pull-rate. • The level of the melt is detected by laser beam reflection. • The grown single crystal ingot undergoes routine evaluation of resistivity, impurity content, crystal perfection, size, and weight. • Sections of the ingot, which are crystallographically defective, irregularly shaped, or undersized, are cut off and discarded as are the seed and butt (or tang ends). • Loss of the ingot material may approach 50% at this point. • Since ingots do not grow perfectly round, nor with sufficiently uniform diameters, they must shaped to the desired form and dimension. • Ingots are deliberately grown slightly larger than the final desired wafer diameter, and a grinding operation removes the excess material as it reduces the ingot to a cylindrical shape of precise diameter. 16 • Exact diameter dimensions are required for making wafers compatible with automated process and wafer transmit equipment. • Since silicon is a hard, brittle material (registering 72.6 on the Rockwell ''A'' hardness scale), grinding machines with industrial grade diamond wheels are used to perform this cylindrical shaping process. • The grinding step is followed by an etch step that removes the grinding work damage. • The ingot diameter is reduced about 0.25-1.0 cm by grinding and etching. • One or flats are next ground along the length of the ingot. • The largest, called the primary flat, is usually positioned relative to a specific crystal direction. • The primary flat orientation is found by using x-ray diffraction techniques. • Automated wafer handling equipment utilizes the primary flat to obtain correct alignment, and in addition, devices on the wafer can be oriented to specific crystal directions with this flat as a reference. • Smaller flats are called secondary flats, and they are utilized to identify the orientation and conductivity type of the wafer. • Since automated equipment relies on the flats for correct mention, the flat dimensions must be precisely machined. • The sawing operation that produces silicon slices from the shaped ingot also defines the surface orientation, thickness, taper, and bow of the slice. • The ingot is rigidly mounted to maintain exact crystallographic orientation during the sawing process. • Wafer thickness is primarily set by the sawing operation, although some material is also removed by subsequent operations. 17 • For a 150 mm wafer with a final thickness 675 µm, a total of ~1200 µm of ingot silicon is needed including 675 µm final wafer thickness, 400 µm for kerf loss during sawing, 50 gm lapping loss, 50 gm etching loss and 25 µm polishing loss. • Larger wafers must be thicker to allow them to withstand thermal processes (epitaxy, oxidation, and diffusion) and handling during VLSI fabrication, so that fewer wafers per unit length of ingot are possible than for smaller wafers. • The most common mode of slicing is inner diameter slicing (annulus) using stainless steel blades with diamond particles bonded to their edges . • Continuous monitoring with deflection sensors is required to assure that slices are sawed adequately free of bow, taper, work damage, and saw marks. • Cutting speeds are in the neighborhood of 0.05 cm /second with only one slice cut at a time by the saw. • A laser to is used create an alphanumeric dot-matrix character identification code on the front of the wafer near the primary flat can then be employed to identify the manufacturer, conductivity type, resistivity, flatness, wafer number, and device type. • Automatic code readers at various stages of processing can also track wafers and provide data on wafer movements. • The thickness of the wafers is sufficiently variable that a lapping and grinding step is next employed to bring all slices to within the specified thickness tolerance. • This step also serves to reduce bow and warp, and to increase wafer flatness. • Both sides of the slice are lapped using a mixture of Al2O3 and glycerin, using a succession of increasingly finer polishing grits in multiple lapping steps. 18 • This process can achieve flatness uniformities of 2 µm. • The edges of the silicon slices are then shaped (rounded) to reduce the incidence of chipping during normal wafer handling, and helps minimize film buildup on the edge of the wafer during photoresist and epitaxial processes. • The work damage and contamination caused by the previous shaper: steps is next removed. • This damaged and contaminated layer is chemically etched away using a wet etch procedure for this step typically consisting of an enchant solution of hydrofluoric, nitric, and acetic acids to attack the silicon. • A chemical-mechanical polishing step is accomplished by mounting unpolished slices onto a carrier, and placing them on a polishing machine. • A powered platen drives an appropriate polishing pad material across the wafer surface. • A colloidal silica slurry of Sodium hydroxide and fine (~ 10 nm) SiO2 particles, is dripped onto the table. • The frictional heat of the sliding mounted wafers causes the sodium hydroxide to oxidize the silicon which is then abraded away by the silica particles • Following the polishing cycle (in which a layer of about 25 µm is removed) the wafers are subjected to series of chemical dips and rinses to remove the polish slurry. 19 20 21 22 23 24