(1%), Low-Noise (4.4 μVRMS)

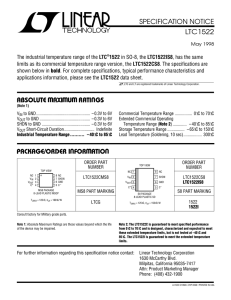

advertisement