Design of a planar inductor for DC-DC converter on flexible

advertisement

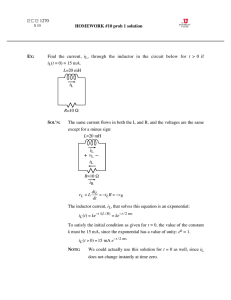

Design of a planar inductor for DC-DC converter on flexible foil applications Jurica Kundrata University of Zagreb, Faculty of Electrical Engineering and Computing Unska 3, 10000 Zagreb, Croatia E-mail: jurica.kundrata@fer.hr Abstract—This paper presents the design of a planar inductor for a DC-DC converter for flexible foil applications. The design challenges related to the flexible foil structure and the DC-DC converter requirements are analysed. The main design challenges are due to the constraints on the inductor physical size, the proximity of a conductive plane to the inductor and very high operating frequency of the DC-DC converter. The methodology of the inductor design is based primarily on EM simulations of the inductor structure and on the evaluation of the simulation results in the context of the resulting lumped-element electrical model. The simulations are verified by measurements of the inductors processed on the FR4 substrate which presently emulates the flexible foil substrate. Index Terms—thick film inductor, electromagnetic modelling I. I NTRODUCTION A. State of the art The electronics on flexible foils is getting popular as it offers new innovative applications in the areas of wearable electronics, lightning devices and displays [1]–[4]. Such applications require power supplies embedded in the flexible foil. Switching-mode power supplies are a de-facto standard in the present DC-DC power conversion applications [5]. Switching-mode power supplies require an energy storage element to work properly and inductors are often used to fulfil the required function. In the case of the flexible foil applications this inductor has to be embedded on the foil as well. Usually, a planar inductor design based on spiral geometry is used. Spiral planar inductors are modelled and characterized quite well [6]–[9]. Many conclusions based on the research of planar inductors processed on the Si substrate in the integrated circuits can be applied on the inductors implemented in the flexible foil technology, but some specific power applications in the flexible foil can pose a set of unique design challenges. B. Design challenges The inductor is designed for a buck-type DC-DC converter that drives an OLED tile realized on the flexible foil. Numerous design challenges are related to designing an inductor for a flexible foil application. The constraints placed on the physical size of the inductor are one of the design challenges. The most obvious physical constraint is the thickness of the metal layer the inductor is This work was supported by the European Commision under the Seventh Framework Programme (FP7) through project IMOLA Intelligent light management for OLED on foil applications (Grant Agreement No. 288377). patterned in. Flexible foil application of the inductor implies a planar layout of the inductor as the multi-layered layouts are unrealisable because of the limited total thickness of the foil. The physical constraint specific to this implementation is the limited available area for the placement of the planar inductor. The OLED tile size ranges from 30 x 30 to 125 x 35 mm2 and an inductor must be placed on the area of a single OLED tile. The area enveloped by an inductor is closely related to the maximally realizable inductance of the inductor thus the available area for the placement of the inductor is an important design challenge. The structure of the OLED tile and its application in a flexible foil presents the next specific design challenge. In the context of the inductor design the cathode of the OLED tile represents a uniform metal plane acting as a ground plane. This ground plane is only separated from the inductor by a thin foil. A ground plane in close proximity to the inductor presents a design challenge as the inductor currents are mirrored over the ground plane. The mirrored currents, i.e. eddy currents reduce the total magnetic flux induced by the inductor and consequentially the total selfinductance of the inductor. The requirements of the DC-DC converter in the context of the electrical characteristics of the inductor are the next important design challenge. The value of the inductance of the inductor is vital to the operation of the DC-DC converter. The resistance and the parasitic capacitance of the inductor directly affect the efficiency of power conversion. The inductor has to preserve its inductive properties in the frequency range that covers the switching frequency of the converter as well as the first few higher harmonics of the driving PWM signal. It sets a requirement on the dynamic behaviour of the inductor, namely that the resonant frequency of the inductor needs to be beyond that frequency range. The planned DC-DC converter places the inductor requirements that are shown in Table I. It should be noted that the maximum resistance requirement will be treated as a requirement placed on the DC value of the inductor resistance because the OLED tile behaves primarily as a capacitive load thus stabilizing the current that runs through the inductor and minimizing its ripple component. II. M ATERIALS AND METHODS A. Electromagnetic simulations The described flexible foil substrate requires a planar inductor structure because of its thin geometry. The thin inductor structure is simulated in the COMSOL Multiphysics. Its RF module is used as the 3D EM solver for this problem. TABLE I THE INDUCTOR REQUIREMENTS OF THE DC-DC CONVERTER TABLE II THE VALUES OF THE DESIGN PARAMETERS Design parameter Electrical characteristics Required value Series inductance, Ls Series resistance, Rs Parasitic capacitance, Cp Resonant frequency, fr 3 to 5 µH <1Ω < 50 pF > 50 MHz Track width, w Track spacing, s Number of turns, N Outer diameter, d Track metal Track thickness Top/bottom dielectric thickness Range value 0.25 to 2 mm 0.25 to 1 mm 1 to max. 28 mm (const.) Cu 35 µm 200 µm Fig. 2. The π-model of the inductor that accounts for the port and interport capacitances and the skin effect. B. Electrical model Fig. 1. The geometry of the inductor model used in the electromagnetic simulations. The geometry of the model used in EM simulations is based on the smallest OLED tile dimensions as it represents the worst case scenario in the context of the inductor total area and thus its inductance. The inductor model is based on a spiral rectangular geometry and it is shown in Fig. 1. The geometry is determined by the outer diameter of the rectangular spiral d, the track width w, the track spacing s and the number of turns of the spiral N . The positions of the ports P1 and P2 are also marked in the figure. The simulated substrate has two dielectric layers and three metal layers. The inductor is wound in M1 (top metal) and the exit towards the port P2 is performed in M2 layer. The bottom metal M3 serves as the ground plane if it is used. The operating frequency of the DC-DC converter determines the frequency range of interest that is analysed in EM simulations. The inductor is driven by a PWM signal from the DC-DC converter which is essentially a rectangular waveform. The analysed frequency range includes the switching frequency of the converter and its higher harmonics and it is determined by the frequency from 1 to 200 MHz. The upper frequency limit is set to include the resonant behaviour of the inductor in the analysis. The electromagnetic simulations are primarily used to investigate the influence of the different design parameters on the electrical characteristics of the inductor. The design parameters are swept in different ranges. The values of the design parameters are shown in the Table II. A lumped-element electrical model is developed to evaluate the electrical characteristics of the inductor in the context of the requirements and to accurately describe the behaviour of the inductor in the frequency range relevant to the operation of the DC-DC converter. In the analysis of the simulation and measurement results a π-model was used and its topology is shown in Fig. 2. The π-model consists of the port capacitances C1 and C2 , the interport capacitance C3 , the interport inductance L1 and the ladder network R1 -R2 -L2 . The capacitances C1 , C2 and C3 account for different resonances of the inductor while the ladder network R1 -R2 -L2 describes the frequency dependant resistance of the inductor, i.e. the skin effect present at the operating frequency of the DC-DC converter [10]. Physically, the capacitances C1 and C2 represent the capacitances of the inductor tracks towards the ground plane. As the geometry of the inductor tracks is asymmetrical in the context of its ports, it is expected that the capacitances C1 and C2 are not equal. The capacitance C3 represents the interwinding capacitance of the inductor. The parameters of the electrical model are extracted using a developed algorithm implemented in MATLAB. The algorithm is described by the flowchart shown in Fig. 3. The algorithm is based on three steps. In the first step the inductance L1 is calculated from the interport impedance. In the following step the capacitances C1 , C2 and C3 are calculated from the resonant and antiresonant frequencies. The third step is based on fitting the ladder network R1 R2 -L2 . Fig. 3. The algorithm used in the extraction of the electrical model parameters. Fig. 4. The layout of the inductor matrix used for verification of the electromagnetic simulations. C. Physical verification The results of the electromagnetic simulations are verified by measurements of the inductors. The inductors are processed on the FR4 substrate. The FR4 substrate has two 200 µm thick dielectric layers and can be considered a good emulation of a flexible foil substrate. Multiple inductors with varied track width and spacing are processed in the form of a matrix. The track widths are 0.5 mm, 1 mm and 2 mm and the track spacing 0.25 mm, 0.5 mm and 1 mm. Both variations are made simultaneously thus accounting for 9 unique inductor designs, as shown in Fig. 4. The same layout is processed in two versions. The first version is realized as a PCB with a single FR4 layer and two layers of metallization, while the second version was realized with an additional FR4 layer with a metal sheet. This metal sheet acted as the ground plane. The measurements are made using a vector network analyser. The ports used in the layout are designed to allow their de-embedding at the reference plane ∆-∆0 shown for the top-left inductor in Fig. 4. A separate layout was developed and used for the Short-Open-Load-Through (SOLT) calibration of the vector network analyser. Fig. 5. The amplitude frequency characteristics of the Z11 and Z12 parameters for the simulated data. Fig. 6. The amplitude frequency characteristics of the Z11 and Z22 parameters for the simulated data with marked resonant frequencies. III. R ESULTS A. Frequency characteristics The frequency characteristics of the inductor are analysed on the inductor example determined by the following set of design parameters w = 1 mm, s = 1 mm, N = 7. The results of the electromagnetic simulations in the context of its Zparameters are presented in Figs. 5 and 6. In Fig. 5 the frequency characteristics of the Z11 and Z12 parameters are presented. Several resonant frequencies can be identified in these characteristics. The frequency characteristics of the interport impedance Z12 has a single local maximum that can be identified as antiresonant behaviour. This implies a parallel LC network between the ports of the inductor which is presented in the electrical model with the interport capacitance C3 (Fig. 2). The frequency characteristic of the port impedance Z11 has two local extremes. One extreme is a local maximum and matches the previously identified antiresonant behaviour of Z12 and the second extreme is a local minimum. This local minimum can be identified as resonant behaviour and implies the existence of the port capacitances. These port capacitances are presented in the inductor model by the capacitances C1 Fig. 7. The dependence of the port capacitances C1 and C2 on the track width with total turn spacing s + w = 1.25 mm and N = 11. Fig. 8. The dependence of the port capacitances C1 in the context of the track width and the number of turns of the inductor with total turn spacing s + w = 1.25 mm. and C2 . The frequency characteristics of the Z11 and Z22 port impedances are compared in Fig. 6. The identified resonant and antiresonant behaviour is emphasized by separate markers. It is to be noted that the antiresonant frequency fa is identical for both ports, but the resonant frequencies fr1 and fr2 are slightly different. This was expected as the port capacitances C1 and C2 are also slightly different because of the asymmetrical inductor structure. In the context of the DC-DC converter requirements the resonant behaviour of this inductor design example is well above the required frequency limit of 50 MHz. B. Design parameter sweeps The design parameter sweeps are the primary method of exploring different inductor designs. The parameter sweeps described in the methodology of this work yield a large database of simulation results. The analysis of this database is presented in a series of figures that represent only a selection of simulation results and are later used for defining a set of design guidelines for the planar inductors. Figs. 7, 8 and 9 show the dependences of the electrical model capacitances C1 , C2 and C3 w.r.t. different design parameters, while Fig. 10 shows such a dependence of the series inductance Ls . The port capacitance dependence on the track width and the interrelationship of the port capacitances C1 and C2 is shown in Fig. 7. Two observations of the results are made. The first observation is that the port capacitances are not equal. This asymmetry of the port capacitances is in accordance to the asymmetric inductor structure. The second observation is that the value of the port capacitances is proportional to the track width. As the total spacing of the turns (s + w) and the number of turns are kept constant, the track width in this figure can be directly correlated with the total track area. This observation is expected because the capacitance of a capacitor is directly proportional to the area of its plates. The port capacitance C1 dependence on the track width and the number of turns is shown in Fig. 8. In this figure the observation concerning the port capacitance dependence on the track width from Fig. 7 is confirmed. This observation Fig. 9. The dependence of the interport capacitances C3 in the context of the track spacing and the number of turns of the inductor with total turn spacing s + w = 1.25 mm. is expanded with the dependence on the number of turns. The dependence of the port capacitance on the number of turns is expected because increasing the number of turns increases the total track area as well. This effectively increases the plate area of the capacitor that represents the port capacitance in conjunction with the ground plane. The interport capacitance C3 dependence on the track spacing and the number of turns is shown in Fig. 9. Two observations are made based on this figure. The first observation is that the interport capacitance is inversely proportional to the track spacing. The interport capacitance is based primarily on the capacitance between neighbouring inductor turns. It is expected that, if the space between the tracks is increased while maintaining the same track length, the capacitance is decreased. The second observation is similar to the observation of the port capacitance dependence on the number of turns. The interport capacitance is increased as the number of turns is increased and thus the length of the tracks is increased. It should be noted that the dependence of the interport capacitance on the number of turns is nonlinear because the dependence of the track length on the number of Fig. 10. The dependence of the series inductance Ls in the context of the track width and the track spacing while maintaining the series resistance constant Rs = 1 Ω. turns is nonlinear as well, i.e. the inner turns of the inductor spiral contribute the least to the track length. The dependence of the series inductance Ls on the track width and the track spacing is shown in Fig. 10. These simulation results are made in the context of the DCDC converter requirements for the series resistance of the inductor. The required number of turns to achieve the upper resistance limit for each combination of the track width and track spacing was calculated and used in the simulations. An observation is made based on these results. The inductance achievable in the context of the resistance requirement is at the maximum for the combination of minimal track width and minimal track spacing. When the track width and/or the track spacing increase, the inductance of the inductor decreases. This observation is interpreted by understanding that a narrower turn with minimal spacing can envelope a greater area and thus produce greater inductivity. Another effect should be considered; while the wider turns can support a greater number of turns in the context of limited inductor resistance, the number of turns in the case of a planar inductor suffers from the effect of diminishing returns. The inner turns are contributing the least to the total inductance of the planar inductor. In the context of the DC-DC converter requirements the capacitances of the inductor are significantly lower than the required maximum capacitance, while the inductance is below the required range of values. C. Physical verification The results of the electromagnetic simulations are verified by measuring a set of inductors with different design parameters. The results of the physical verification are presented in Figs. 11 and 12. These figures show the correlations between the measured and simulated data. The correlation of the extracted inductance L of the inductor is given in Fig. 11. The simulated inductance correlates with the measured inductance well. The effect of the metal plane on the inductance and the resonant frequency can be observed in these results. As expected introducing the metal plane in the substrate of the designed inductors decreases its inductance approximately Fig. 11. The correlation between the measured and simulated data in the context of the extracted inductance of the inductor. Fig. 12. The correlation between the measured and the simulated data in the context of the resonant frequency of the inductor. by a factor of 5 because of the mirroring of the inductor currents and reduction of the magnetic flux. The correlation of the resonant frequency fa is shown in Fig. 12. The simulated resonant frequency correlates with the measured resonant frequency rather well with a slight offset. The probable cause to the offset is the uncertainty of the processed substrate thickness compared to the one used in the simulations. In the context of the DC-DC converter requirements the inductance of a few inductor designs without the metal plane falls within the required range of values. With the introduction of the metal plane in the substrate design, none of the design cases conform to the requirements, i.e. the inductor is too small. IV. D ISCUSSION A. Design guidelines Based on the observations made on the results of the simulations several guidelines for designing a planar inductor can be set. Each guideline corresponds to a single design parameter of the inductor. The first design guideline corresponds to the track width. Based on the observations of the results the track width should be minimized. This guideline minimizes the value of the port capacitances and maximizes the value of the inductance in the context of the required inductor resistance. The second guideline is related to the track spacing. The observations of the results imply that the track spacing should be optimized between the requirements on the resonant frequency and the requirements on the inductance. The resonant frequency of the inductor is closely related to the value of the interport capacitance. If the requirements on the resonant frequency are more relaxed, then the general guideline is to minimize the track spacing in order to maximize the inductance of the inductor. The third guideline is based on the number of turns. The results have shown that the increased number of turns increases the parasitic capacitances of the inductor thus a smaller number of turns of the inductor is more desirable. In the context of the resistance requirement, narrower tracks with smaller spacing have a smaller number of turns than the wider tracks with greater spacing. Coincidently the narrower turns with smaller spacing are more desirable in the context of the inductance. To sum up, the number of turns should be minimized which can be indirectly achieved by minimizing the track spacing and the track width while respecting the resistance requirement. B. Further development The results have shown that the metal plane in close proximity to the inductor severely degrades its inductance. This ground plane effect is due to the inductor currents mirrored in the metal plane. There are several possible ways to shield the inductor from the metal plane and its degrading effects. One possible solution is the application of patterned ground shields (PGS) [11]–[13]. These shields are an additional conductive layer between the inductor and the metal plane which is patterned in such a way that the path of the induced eddy currents is effectively broken. Another possible solution to the ground plane effect problem is the application of the ferrite polymer composite (FPC) layer between the inductor and the metal plane [14]– [16]. This FPC layer, because of its significant permeability, literally shields the inductor from the metal plane. The described solutions have the potential to restore the inductance of the inductor to the values present in the substrate cases without the metal ground plane below inductor. Further inductance enhancement can be achieved by applying an additional FPC layer above the inductor structure thereby creating a well-defined magnetic path for the magnetic flux induced by the inductor. V. C ONCLUSIONS The design of the planar inductor for DC-DC converter applications is presented. The design is primarily based on investigating the design parameters by electromagnetic simulations. An electrical model is used to analyse the results of the simulations. An algorithm used to extract the electrical model parameters is presented. The electromagnetic simulations are physically verified by measuring the inductor designs processed on the FR4 substrate. Based on the analysis of the results a set of design guidelines is presented. The design guidelines recommend minimizing the track width and the track spacing while adapting the number of turns to the resistance requirement to achieve the maximal inductance. The degrading effect of the ground plane on the inductance of the inductor is analysed. The solutions using the patterned ground shields or ferrite polymer composite are proposed. R EFERENCES [1] I. Manunza, A. Sulis, A. Bonfiglio, ”Organic semiconductor field effect transistors for unconventional applications: flexible sensors and wearable devices,” Proc. Int. Work. Wearable and Implantable Body Sensor Networks, 2006, International Workshop on BSN 2006, pp. 3-5, April 2006. [2] C. D. Kim, J. S. Yoo, J. K. Lee, S. Y. Yoon, Y. I. Park, I. B. Kang; I. J. Chung, ”Full color flexible displays on thin metal foil with reduced bending radius,” Proc. Flexible Electronics and Displays Conference and Exhibition, 2009, pp. 1-4, Feb. 2009. [3] J.-S. Yoo, S.-H. Jung, Y.-C. Kim, S.-C. Byun, J.-M. Kim, N.-B. Choi, S.-Y. Yoon, C.-D. Kim, Y.-K. Hwang, I.-J. Chung, ”Highly Flexible AM-OLED Display With Integrated Gate Driver Using Amorphous Silicon TFT on Ultrathin Metal Foil,” J. Display Technology, vol. 6, no. 11, pp. 565-570, Nov. 2010. [4] E.C.W. de Jong, B.J.A. Ferreira, P. Bauer, ”Toward the Next Level of PCB Usage in Power Electronic Converters,” IEEE Trans. Power Electronics, vol. 23, no. 6, pp. 3151-3163, Nov. 2008. [5] Q. Li, M. Lim; J. Sun, A. Ball, Y. Ying, F. Lee, K.D.T., ”Technology road map for high frequency integrated DC-DC converter,” IEEE Proc. Applied Power Electronics Conference and Exposition (APEC), 2010, pp. 533-539, Feb. 2010. [6] M. Zolog, D. Pitica, O. Pop, ”Characterization of Spiral Planar Inductors Built on Printed Circuit Boards,” Proc. Int. Electronics Technology, Spring Seminar, pp. 308-313, May 2007. [7] H.-H. Lee, J.-Y. Park, ”Characterization of Fully Embedded RF Inductors in Organic SOP Technology,” IEEE Trans. Advanced Packaging, vol. 32, no. 2, pp. 491-496, May 2009. [8] J. Olivo, S. Carrara, G. De Micheli, ”Modeling of printed spiral inductors for remote powering of implantable biosensors,” Proc. Int. Symp. Medical Information and Communication Technology (ISMICT), 2011, pp. 29-32, March 2011. [9] Y. Cao, R.A. Groves, X. Huang, N.D. Zamdmer, J.-O. Plouchart, R. A. Wachnik, T.-J. King, C. Hu, ”Frequency-independent equivalentcircuit model for on-chip spiral inductors,” IEEE J. Solid-State Circuits, vol. 38, no. 3, pp. 419-426, Mar 2003. [10] X. Sun, G. Carchon, W. De Raedt, ”An optimized model of skin effect for on-chip spiral inductors,” IEEE Proc. Radio Frequency Integrated Circuits (RFIC) Symposium, pp. 445-448, June 2004 [11] C. P. Yue, S. S. Wong, ”On-chip spiral inductors with patterned ground shields for Si-based RF IC’s”, IEEE J. Solid-State Circuits, vol. 33, no. 5, pp. 743-752, 1998. [12] S.-M. Yim , T. Chen, K. K. O, ”The effects of a ground shield on the characteristics and performance of spiral inductors”, IEEE J. Solid-State Circuits, vol. 37, no. 2, pp. 237-244, 2002. [13] J. Ko, K. Kim, J. Byun, H. Kim, ”Parameter extraction and optimal design of spiral inductor using evolution strategy and sensitivity”, IEEE Trans. Magnetics, vol. 46, no. 8, pp. 28312834, 2010. [14] E. J. Brandon, E. E. Wesseling, V. Chang and W. B. Kuhn, ”Printed microinductors on flexible substrate for power applications”, IEEE Trans. Compon. Packag. Technol., vol. 26, p. 517, 2003. [15] I. Kowase, T. Sato , K. Yamasawa, Y. Miura, ”A planar inductor using Mn-Zn ferrite/polyimide composite thick film for low-Voltage and large-current DC-DC converter”, IEEE Trans. Magn., vol. 41, no. 10, pp. 3991-3993, 2005. [16] Z. Pengli, W. Yanmin, S. Rong, ”Synthesis and magnetic properties of Ni-Zn ferrite @polyaniline/epoxy composites for embedded inductor applications,” Proc. Int. Symp. Advanced Packaging Materials (APM), 2011, pp. 16-19, Oct. 2011.