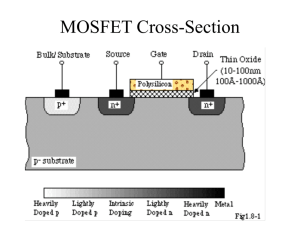

MOSFET I-V characteristics: general consideration

advertisement

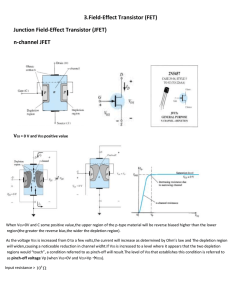

MOSFET I-V characteristics: general consideration The current through the channel is V I= R The gate length L + - where V is the DRAIN – SOURCE voltage V-GS V G + S D Semiconductor Here, we are assuming that V << VT (we will see why, later on) The channel resistance, R (W is the device width): R= L q n μ aW = L q ns μ W where nS = (ci/q) × (VGS – VT) The channel current is: I = V (q nS μ W) /L = V q μ W (ci/q) × (VGS – VT) /L I = μ W ci × (VGS – VT) V /L 1 MOSFET transconductance In most MOSFET applications, an input signal is the gate voltage VG and the output is the drain current Id. The ability of MOSFET to amplify the signal is given by the output/input ratio: the transconductance, gm = dI/dVGS. I = μ W ci × (VGS – VT) V /L From this: (V is the Drain – Source voltage) gm = V μ W ci /L Key factors affecting FET performance (for any FET type): μ I and gm L I and gm High carrier mobility μ and short gate length L are the key features of FETs 2 Modern submicron gate FET Source Drain V-groove quantum wire transistor Gate 2 μm Operating frequency – up to 300 GHz 3 Drain current saturation in MOSFET The gate length L + - VGS- + V G S D Semiconductor When no drain voltage V is applied, the entire channel has the same potential as the Source, i.e. VCH = 0. In this case, as we have seen, nS = (ci/q) × (VGS – VT) where VGS is the gate – source voltage and VT is the threshold voltage When the drain voltage V is applied, the channel potential changes from VCH = 0 on the Source side to VCH= V on the drain side. In this case, the induced concentration in the channel also depends on the position. 4 Drain current saturation in MOSFET The gate length L + - VGS- + V G S D Semiconductor With the drain voltage V is applied, the actual induced concentration in any point x of the channel depends on the potential difference between the gate and the channel potential V(x) at this point. This is because this local potential difference defines the voltage that charges the elementary gate – channel capacitor. On the source end of the channel (x=0, VCH=0): nS(0) = (ci/q) × (VGS – VT). On the drain end of the channel (x=L, VCH= V): nS(L) = (ci/q) × (VGS – VT - V) < nS(0) At any point between source and drain, nS(L) < nS(x) = (ci/q) × [VGS – VT – V(x)] < nS(0) 5 Drain current saturation in MOSFET VGS V G S D Semiconductor nS VGS > VT Id V=0 V1 > 0 V2 > V1 V3 = VGS-VT L V x 6 MOSFET Modeling 1. Constant mobility model Assuming a constant electron mobility, μn, using the simple charge control model the absolute value of the electron velocity is given by, dV vn = μnF = μn dx With the gate voltage above the threshold, the drain current, Id, is given by dV ns dx Id dV = dx W μn ci (VGT −V ) Id = Wqμ n Rewriting, Where W is the device width Where VGT = VGS – VT. dV vs dx dependence represents a series connection of the elementary parts of MOSFET channel (for the series connection, voltages add up whereas current is the same). 7 (VGT −V )×dV = Id W μ n ci dx Integrating along the channel, from x=0 (V=0) to x=L (V=VDS), we obtain: For, VDS << VGT, For, larger VDS , W μn ci Id = VGT VDS L Id = Wμ n ci ⎛ V ⎞ ⎜ VGT − DS ⎟ V DS L ⎝ 2 ⎠ Linear region Sub-linear region Sub-linear 8 Channel pinch off and current saturation Pinch off occurs when VG – VCH = VT at the drain end; nS (L) =0; the current Id saturates When, VDS = VSAT = VGS − VT where VSAT is the saturation voltage. From the Id – V dependence, at VDS=VSAT = VGT, Id = Wμ n ci ⎛ V ⎞ ⎜ VGT − DS ⎟ V DS L ⎝ 2 ⎠ The saturation (pinch off) current, Wμ n ci 2 Id = Isat = VGT 2L 9 Transconductance Defined as gm = dId dVGS V DS From the equations for the drain current, Id, derived above, we find that ⎧βVDS , gm = ⎨ ⎩βVGT , for VDS << VSAT for VDS > VSAT where W β = μ n ci L High transconductance is obtained with high values of the low field electron mobility, thin gate insulator layers (i.e., larger gate insulator capacitance ci = εi/di), and large W/L ratios. 10 2. Velocity saturation model In semiconductors, electric field F accelerates electrons, i.e. the drift velocity of electron increases: v=μF However, at high electric fields this velocity saturates In modern short channel devices with channel length of the order of 1 µm or less, the electric field in the channel can easily exceed the characteristic electric, Fs field of the velocity saturation vs Fs = μn 11 Electric field in the channel 1.2 18 0.8 0.6 0.4 0.2 Electric Field (kV/cm) 1.2 Potential (V) 16 1 1 14 1 12 1.2 10 8 6 4 2 0 0 0 1 2 3 4 5 Distance (µm) 0 1 2 3 4 5 Distance (µm) Surface Concentration (1012 1/cm2) the electric field in the channel in the direction parallel to the semiconductorinsulator interface dV Id v = μ F = μ F= n n n dx qμ nns (V )W 1.4 1.2 1 0.8 0.6 1 0.4 1.2 0.2 0 0 1 2 3 4 5 Distance (µm) Potential, electric field, and surface electron concentration in the channel of a Si MOSFET for VDS = 1 and 1.2 V. L = 5 µm, di = 200 Å, µn = 800 cm2/Vs, VGS = 2 V, VT = 1 V. 12 Once the electric field at the drain side of the channel (where the electric field is the highest) exceeds Fs, the electron velocity saturates, leading to the current saturation. In short-channel MOSFETs, this occurs at the drain bias smaller than the pinch-off voltage VDS = VGT. Id dV = dx W μn ci (VGT −V ) Field at drain Saturation condition, Id dV F ( L) = x=L = dx W μn ci (VGT −VDS ) ISAT Fs = μ nci (VGT − VSAT )W 13 Saturation current versus gate-to-source voltage for 0.5 µm gate and 5 µm gate MOSFETs. Dashed lines: constant mobility model, solid lines: velocity saturation model. 14 MOSFET saturation current accounting for velocity saturation: Isat = gch VGT ⎛V ⎞ 1 + 1 + ⎜ GT ⎟ ⎝ VL ⎠ 2 where VL = FsL and the channel conductance gch = q µn ns W / L, where ns=ci VGT/q When FS L >> VGT (MOSFET with long gate or no velocity saturation): Isat = gch VGT ⎛V ⎞ 1 + 1 + ⎜ GT ⎟ ⎝ VL ⎠ 2 gch I sat ≈ VGT 2 Wμ n ci 2 Id = Isat = VGT 2L (Expression obtained before on slide 9) When FS L << VGT (MOSFET with short gate or early velocity saturation): Isat = gch VGT ⎛V ⎞ 1 + 1 + ⎜ GT ⎟ ⎝ VL ⎠ 2 I sat ≈ gch VL (Note that gch is controlled by VGT) 15 Source and drain series resistances. Source and drain parasitic series resistances, Rs and Rd, play an important role, especially in short channel devices where the channel resistance is smaller. Gate Source R s R d Drain Vds= Id R s + VDS + Id R d VGS = Vgs − Id Rs VDS = Vds − I d (Rs + Rd ) 16 The measured transconductance (extrinsic) dId gm = dVgs The intrinsic transconductance (VGS and VDS being intrinsic voltages) Vds =const dId g mo = dVGS V = const DS g mo gm = 1 + g mo R s + gdo ( R s + Rd These parameters are related as Where gd0 is the drain conductance dI d g do = dVDS ) VGS =const In the current saturation region (VDS > VSAT), gd0 ≈ 0 Similarly, extrinsic drain conductance can be written as, gd = gdo 1 + gm o R s + g ( R s + R do d ) 17 The saturation current in MOSFET with parasitic resistances: Isat = gcho Vgt ( 1 + gcho Rs + 1 + 2gcho Rs + Vgt / VL ) 2 where VL = FsL and gcho = ciVgtµnW/L. 160 160 140 120 Drain Current (mA) Drain Current (mA) 140 100 80 60 40 20 120 100 80 60 40 20 0 0 0.5 1 1.5 2 2.5 Drain-to-Source Voltage (V) 0 0 0.5 1 1.5 2 2.5 Drain-to-Source Voltage (V) MOSFET output characteristics calculated for zero parasitic resistances and parasitic resistances of 5 Ω. Gate length is 1 µm 18 MOSFET capacitance-voltage characteristics VGS S G V D Semiconductor To simulate MOSFETs in electronic circuits, we need to have models for both the current-voltage and the capacitance-voltage characteristics. As MOSFETs is a three terminal device, we need three capacitances: Cgs, Cgd and Cds. Capacitance (differential) is defined as C = dQ/dV. For example, Cgs = dQs/dVgs (where Qs is the channel charge between S and G) Therefore, the total channel charge QN has to be divided (partitioned) between the source and drain charges. How should we partition QN between Qs and Qd? It is clear from the device symmetry that at zero drain bias Qs = Qd. If the total channel charge is QN, then Qs = 0.5 QN and Qd = 0.5 QN. 19 MOSFET capacitance-voltage characteristics In the saturation regime, the charge distribution is no longer symmetrical: Qs > Qd In this case, we let Qs = FpQN and Qd = (1 – Fp)QN, where Fp is the partitioning factor. In saturation, Fp > 0.5 The challenge using this model is to determine Fp as a function of Vgs and V 20 Meyer model for MOSFET capacitance (used in SPICE) 2⎤ ⎡ 2 ⎢ ⎛ VGT −VDS ⎞ ⎥ Cgs = Ci 1 − ⎜ ⎟ +C f 3 ⎢ ⎝ 2VT −VDS ⎠ ⎥ ⎣ ⎦ 2 ⎡⎢ ⎛ VGT Cgd = Ci 1 − ⎜ 3 ⎢ ⎝ 2VT −VDS ⎣ ⎞ ⎟ ⎠ 2⎤ ⎥ +C f ⎥ ⎦ Ci = ci × W × L is the channel capacitance The capacitance Cf is the fringing capacitance. C f ≈ βc ε s W where βc ≈ 0.5 In saturation, VDS has to be replaced by VSAT (where VSAT = VGT) This results in CGS SAT = (2/3) Ci+Cf; CGd SAT = Cf 21 Meyer model for MOSFET capacitance (used in SPICE) 0.7 C GS/C i 0.6 C/Ci 0.5 0.4 0.3 CGD/C i 0.2 0.1 0.0 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 VDS/VSAT 22