1100 - Vos and Ib - slides

advertisement

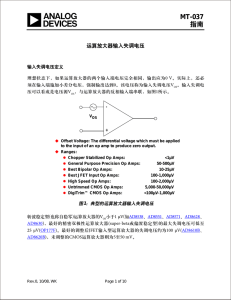

Input Offset Voltage (VOS) & Input Bias Current (IB) TIPL 1100 TI Precision Labs – Op Amps Presented by Ian Williams Prepared by Art Kay and Ian Williams Input Offset Voltage - VOS VOUT VOS = 50!V 2 Input Offset Voltage - VOS Input offset from mismatch of input transistors VOUT 3 Offset Voltage Specs and Distribution OPA827 4 Simulate Input Offset Voltage V U1 OPA350 - VM1 -150uV Vcm 2.5 + + VEE 5 R1 1k + + V VM2 -150uV Vload 2.5 5 Drift Slope – Positive and Negative OPA835 OPA835 For this example VOS drift is defined as: ( ) !V os Vos T1 " Vos ( 25C) !T T1 " 25C 6 Drift Slope – Common Definition Vosi at Temp 160 140 (-40C, 100uV) Vosi (uV) 120 (85C, 150uV) 100 80 60 40 (25C, 30uV) 20 0 -40 -20 0 20 40 60 80 100 Temp (degC) ! Vos !T ! Vos !T = = ( ) ( ) Vos T1 ! Vos( 25C) + Vos T T12 ! Vos( 25C) T 1 ! T2 100"V ! 30"V + 150"V ! 30"V 85C ! ( !40C) = 1.52 "V °C 7 Application Example R2 99k + Vosi 0.1mV Vout = (1mV+ 0.1mV)*(100) = 110mV + R3 1k R1 1k VOS introduces 10% error! Vin 1m 8 Input Offset Drift Calculations R2 99k + Vosi drift 1.5uV/C x (T – 25C) + Vosi 0.1mV Vout + R3 1k R1 1k Temp (°C) VOS Initial + Drift +1.5uV/C VOS Initial + Drift -1.5uV/C -25 °C 25uV 175uV 0 °C 62.5uV 137.5uV 25 °C 100uV 100uV 50 °C 137.5uV 62.5uV 85 °C 190uV 10uV 125 °C 250uV -50uV Vin 1m Vosi = Vosi_room + Vosi_drift" ( T ! 25C) Example calculations: !V Vosi = 100!V + 1.5 " [ ( 25C) ! 25C] = 100!V C At 25C !V Vosi = 100!V + 1.5 " [ ( 125C) ! 25C] = 250!V C At 125C 9 Range of Offset - !V to mV Op Amp VOS (max) (high grade) VOS Drift (max) (high grade) Technology OPA333 10 !V 0.05 !V/°C Zero Drift CMOS OPA277 20 !V 0.15 !V/°C Precision Bipolar OPA188 25 !V 0.085 !V/°C Auto-Zero CMOS OPA192 25 !V 0.5 !V/°C CMOS OPA211 50 !V 1.5 !V/°C Precision Bipolar OPA827 150 !V 1.5 !V/°C (typ.) JFET input, Bipolar, Precision OPA350 500 !V 4 !V/°C (typ.) CMOS OPA835 1.85 mV 13.5 !V/°C High Speed Bipolar LM741 3.00 mV 15 !V/°C Bipolar commodity (lower cost) 10 Input Bias Current - IB 150 nA VOUT 210 nA Input bias offset current: IB_OS = IB1 – IB2 = 210 nA – 150 nA = 60 nA 11 Simple Bipolar, No IB Cancellation Vcc R1 R2 Ib1 Vin1 Vin2 Ib2 Q1 Q2 Bias current in bipolar amplifiers is from input transistor base current. It is typically larger than in FET-input amplifiers and it flows into the input terminals. IS1 12 Bipolar with IB Cancellation Vcc Ib Cancel Circuit R1 R2 Ib1 Vin1 Vin2 ! Q1 ! IS1 Ib2 Q2 The input bias currents are mirrored and summed back in to cancel the bias current. This has the effect of significantly reducing input IB. Note that when this is done, IB can flow in both directions. Also, IB_OS is no longer smaller then IB. IB_OS = IB1 – IB2 Ib Cancel Circuit 13 Bias Current for CMOS Vcc Vcc Bias current in FET-input amplifiers is mainly from leakage into ESD protection diodes. R1 R2 Q1 Q2 Ib1 Vin1 Vcc IS1 Vin2 Ib2 14 IB over Temperature OPA350 OPA277 CMOS amplifier: In this case you see a dramatic increase in bias current at 25 °C. Note the logarithmic graph, which doubles every 10 °C. Bipolar amplifier: In this case you see a dramatic increase in bias current at 75 °C. 15 IB Calculation – OPA211 at High Temp. Using nodal analysis Point for nodal analysis Vin R1 R1 1k R2 99k Rf + Ib = 0 Using superposition set Vin=0V - Ib 200nA R3 1k + Vin 1m Vin ! Vout Vin Vin % " Vout = Rf ( # Ib + + & R1 Rf $ ' Ib 200nA Ib 150nA + 0 0 % Vout = Rf ( "# Ib + + = Ib ( Rf Rf & R1 $ ' In this example Vout_Ib = ( 200nA) ( ( 99k! ) = 20mV 99 Vout_vin = 1mV( "# + 1 %& = 100mV $1 ' Vout_total = 20mV_100mV = 120mV 16 Range of Bias Current – fA to nA Op Amp IB (max) (high grade) IB at max temp. Technology OPA129 100 fA 20 pA (typ.) Difet – Ultra Low Bias Current OPA627 5 pA 1nA Difet – Precision High Speed OPA350 10 pA 500 pA (typ.) CMOS OPA827 50 pA 50 nA max JFET input, Bipolar, Precision OPA333 70 pA 150 pA (typ) Zero Drift CMOS OPA277 1 nA 2 nA (max) Precision Bipolar OPA211 125 nA 200 nA Precision Bipolar OPA835 400 nA 530 nA High Speed Bipolar LM741 80 nA 0.2 !A (max) Bipolar commodity (lower cost) 17 Thanks for your time! Please try the quiz. 18