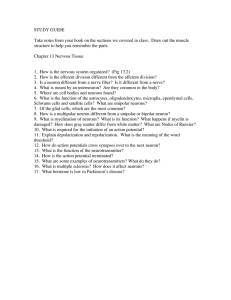

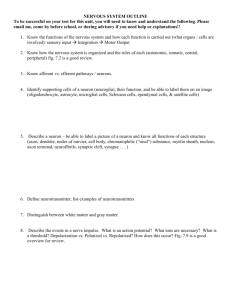

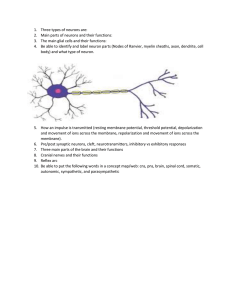

Document

advertisement