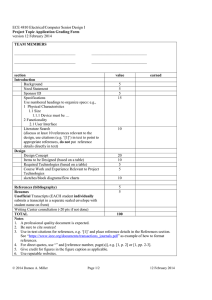

Miller capacitance and Gain-Bandwidth Product Miller Effect

advertisement

Miller capacitance and

Gain-Bandwidth Product

Saeeid Tahmasbi Oskuii (saeta621@student.liu.se)

Behzad Mesgarzadeh (behme822@student.liu.se)

1

Miller Effect

• Miller Theorem

• Miller Capacitance

•

•

•

•

•

Miller Effect in digital circuits

Miller multiplier

Impact of Miller Capacitance on propagation delay

Impact on Power consumption

Applications of Miller Effect

• Gain Bandwidth Product

• Conclusion

2

1

Miller Theorem

An important phenomenon that occurs in many analog and digital

circuits is related to ”Miller Effect”, as described by Miller in a

theorem.

Miller theorem describes the way to convert a floating load into

two grounded loads, in such way that the voltages and currents

are remained unchanged.

X

Z Y

X

I

I

I

Z1

Z2

Y

3

Miller Theorem (Cont’d)

X

Z Y

X

I

I

I

Z1

Z2

Y

V −V

V

Y ,A= Y

I= X

Z

V

X

V

X

V −V

Y Z =

=Z I =Z X

1

1

1

Z

Z

V

1− Y

V

X

V −V

X

Y Z =

V =Z I =Z

Y

2

2

2

Z

Z

V

1− X

V

Y

Z

Z =

1 1− A

Z =

2

Z

1−

1

A

4

2

Miller Theorem (Cont’d)

It is important to know when this theorem is valid. Miller’s theorem

does not stipulate the conditions under which this coversion is

valid. If the impedance Z forms the only signal path between X and

Y, then the conversion is often invalid.

An example of improper use of Miller effect::

X

R1

Y

R2

X

Y

R1+R2

R2

-R2

5

Miller Capacitance

1

1

­

° Z1 = (1 + A)Cs = C s C1 = C (1 + A)

1

1

Assume Z = °®

1

1

1

=

C2 = C (1 + )

Cs

°Z 2 =

1

A

(1 + )Cs C2 s

°

A

¯

C

-A

-A

C(1+A)

1

C(1+ A

-)

6

3

Miller Capacitance (Cont’d)

Miller capacitance for large gain:

C

-A

-A

AC

C

­°1 + A ≈ A

A >> 1 ® 1

1+ ≈ 1

°̄ A

7

Miller Effect in digital circuits

Vout

Vin

C M = C gdp + C gdn

∆V

Vin

CM

Vout

∆V

Vin

Vout

2C M

2C M

8

4

Miller Effect in digital circuits

Vout

Vin

Vout

CM

−

Instantanous Input Capacitance:

C (Vin ) =

iM

∂Q

M =C

∂V

in

M

∂Vout

∂Vin

Instantanous

Input Capacitance

Vin

Vin

[1 − A(Vin )]

Vin

9

Miller Multiplier

C (Vin ) =

iM

∂Q

M = C [1 − A(V )]

in

M

∂V

in

Miller Multiplier =

CiM

CM

As the input voltage varies,the Miller Capacitance

follows the gain curve.The Multiplier is 1 across nearly

the whole input range and rises to about 30 in a narrow

range about V inv .

10

5

Impact on propagation delay

C

M

2C

M

2C

M

• Although the average

Miller Multiplier for a full

swing signal is 2, for slowly

varying signal in the high

gain region of the inverter

can be 20 or more.

11

Impact on power consumption

CM

2C

M

2C

M

4 Times Greater Capacitance Increases Power Consumption

12

6

Frequency Response

A Three pole Transfer Function:

H ( s) =

K

s

s

s

(1 + )(1 + )(1 + )

ω1

ω2

ω3

∠H ( jω ) =

{

0°

ω << ω 1

270° ω >> ω 3

13

Stability Issue (Phase Margin)

20 log10 H ( jω )

φ M = 180 + ∠H ( jω c )

-20 dB/Dec

0 dB

When: H ( jω c ) = 1

-40 dB/Dec

-60 dB/Dec

ω 2 ω3

ω1

∠H ( jω )

ω

ω

For Stability Phase

Margin Must be

Greater Than 0.

-90

Phase Margin

-180

-270

14

7

Negative Phase Margin

20 log10 H ( jω )

-20 dB/Dec

0 dB

An Unstable System

ω

ω1

∠H ( jω )

2

ω

ω3

jω

ω

-90

-180

Phase Margin

-270

15

Compensation

jω

Assume this node gives dominant pole (

ω3

ω1

ω2)

ω2

Before Compensation

CM

σ

jω

1

-A1

2

C2

-A 2

3

ω1

ω3

ω2

After Compensation

σ

16

8

Compensation (cont’d)

Effects of Miller Capacitance in Frequency Compensation:

1. Closes Dominant pole toward Origin

2. Causes to Split First and Second poles

3. Increases Phase Margin and Make System Stable

But:

REDUCES BANDWIDTH !!

17

Miller Effect Between Wires

∆V

C

∆V

2∆V

2C

2C

It seems that there is a 2 times larger capacitance

between the wires.

18

9

Gain Bandwidth Product

At high frequencies the gain of the static

CMOS gate is much smaller than DC gain.

Gain

A( f )

ADC

1

f

fc

f1

19

GBP (Cont’d)

Above cutoff frequency,gain rolls off linearly

with frequency crossing unity at unity-gain

frequency.

In this high frequency region, the gainbandwith product is constant:

fA( f ) = f1

( f > fc )

20

10

GBP (Cont’d)

Calculating

f1:

For small-signal sine wave:

dvout i g m vin

= =

C

C

dt

At the point of unity gain:

ω1 =

gm

I

1

1

≈ DSS = f1 =

C VDDC τ

2πτ

21

GBP (Cont’d)

Example:

τinv = 30ps f1 = 5.3GHz

As we know: ADC ≈

Assuming:

4

(VGS −VT )(λn + λp )

λn + λ p = 0.2,VGS − VT = 1

ADC = 20 f c = 265MHz

22

11

Conclusion

•

•

•

•

Miller capacitance in digital

applications usually slows down the

speed of the circuits and increases the

power consumption.

In analog circuits Miller effect can be

used to stabilize the system.

Miller capacitance between two wires

reduces noise margin and speed.

Gain-Bandwith product is a constant

value above the cutoff frequency.

23

12