Second-Order Sallen-Key Filters Properties of Sallen

advertisement

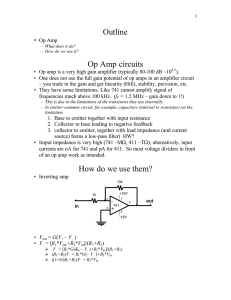

Second-Order Sallen-Key Filters S.K. Low-Pass Filter S.K. High-Pass Filter R C R R + 0 - 0 Vin C Vout Q= (A-1)R R 1 , RC Av = A, C ωc = 0 C + 0 - 0 Vin Vout R 1 3− A S.K. Band-Pass Filter C 0 0 C Vout 2R R Q= 1 3− A S.K. Band-Reject Filter 2C + 0 - Vin (A-1)R R R R 1 , RC Av = A, ωc = 0 (A-1)R 1 ωo = RC 1 Q= 3− A Av = AQ R C 1 RC 1 Q= 4 − 2A Av = A ωo = R 0 + 0 - C 0 Vin Vout R/2 R (A-1)R Properties of Sallen-Key Filters: 1. Simplicity of the design 2. Non-Inverting Amplifier (positive Gain) 3. Replication of elements Limitations of Sallen-Key Filters: 1. The Gain and Q are related 2. Q must be > ½, since A must be > 1 Other Active Filters Band Pass 1: Cf Rf Ri H (s) = − Ci Vin Vout 1 s Rf C f Rf Ri ⎛ 1 1 s2 + ⎜ + ⎜ R f C f Ri Ci ⎝ ⎞ 1 ⎟⎟ s + Ri Ci R f C f ⎠ Band Pass 2: R3 C2 R2 C1 Vin H (s) = Vout R1 − 1 s R2C2 ⎛ C + C2 ⎞ 1 s2 + ⎜ 1 ⎟s + || R C C R R ⎝ 3 1 2 ⎠ ( 1 2 ) R3C1C2 Band Pass 3: R2 C2 R1 C1 Vin 1 s R1C2 H (s) = ⎛ C + C2 ⎞ 1 s2 + ⎜ 1 ⎟s + R1R2C1C2 ⎝ R2C1C2 ⎠ − Vout Band Reject 1: R1 ⎛ 2 R3 ⎞ 1 s2 + s ⎜ − ⎟+ 2 R4 ⎝ R 2 C R1R4C ⎠ C R1R2 H (s) = 2 1 R3 + R4 s2 + s + 2 R2C C R1R2 R2 C C R3 Vin Vout R4 Other Active Filters Properties & Design Hints • These amplifiers are “inverting amplifiers” (negative gain) • BPF1 is restricted to Q > ½. • BPF2 can have a Q < ½ if C1 ≠ C2 . • Both gain and Q can be controlled with the circuit elements. • BRF1 does not have a true zero on the imaginary axis R 2 unless 3 = . R1R4 R2 • A design may not require a true null, but a notch. The zero can be adjusted to control the “dip” in the response. • Typical design: Specify the gain, Q, and resonant frequency, and then solve for the circuit elements. o Requires some assumptions for the values of R’s and C’s (problem is under-determined). Choose R to be large (> 1 k) when possible. Possibly choose relationships (such as C1 = k × C2 ). o Equations for remaining elements can be nonlinear. o Not all values of Q, Av, and ωo are necessarily possible. o Gain may not be as important as Q and resonant frequency if the amplifier is one stage of a system design.