Lecture Notes Session 12

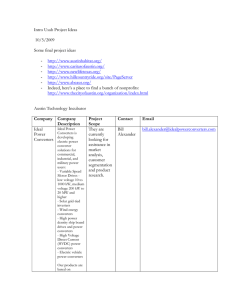

advertisement

EE247 Lecture 12 • Administrative issues Midterm exam Tues. Oct. 24th o You can only bring one 8x11 paper with your own written notes (please do not photocopy) o No books, class or any other kind of handouts/notes, calculators, computers, PDA, cell phones.... o Midterm includes material covered to end of lecture 14 EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 1 EE247 Lecture 12 Today: – Example of Switched-Capacitor filters NOT followed by an ADC! – Data converters • • • • ADC & DAC transfer curve Sampling, aliasing, reconstruction Amplitude quantization Static converter error sources – Offset & full-scale error – DNL & INL EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 2 Summary of Last Lecture • Switched-Capacitor Filters (continued) – Effect of non-idealities – Bilinear switched-capacitor filters – Filter design summary • Comparison of various filter topologies • Data Converters (continued today) EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 3 Last Lecture Questions • Based on the CODEC example, class may have the impression that S.C. filters are always followed by an ADC! • Assumption not accurate – Example- Switched-capacitor filters used in the transmit path of ISDN ICs EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 4 Data Transmission Over Existing Twisted-Pair Phone Lines Backbone Digital Network Central Office Xmitter Customer Twisted Pair Xmitter Receiver Receiver 3 to 5km POTS • Data transmitted over existing voice grade phone lines covering distances close to 3.5miles – Voice-band MODEMs – ISDN – HDSL, SDSL,…… – ADSL EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 5 Data Transmission Over Twisted-Pair Phone Lines ISDN (U-Interface) Transceiver Backbone Digital Network Central Office Xmitter Customer Twisted Pair Xmitter Receiver Receiver 3 to 5km POTS • • • • • Full duplex transmission (RX & TX signals sent simultaneously) 160kbit/sec baseband data (80kHz signal bandwidth) Standardized line code 2B1Q (4 level code 3:1:-1:-3) Max. desired loop coverage 18kft (~36dB signal attenuation) Final required BER (bit-error-rate) 10-7 Æ (min. SNDR=27dB) EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 6 Analog Front-End 2nd order Butterworth S.C. Filter 2b S.C. DAC Class A/B Line Driver fs=2.56MHz fs=20.48MHz To avoid stringent requirements for nonlinear echo canceller: Æ high linearity analog circuitry needed (~ 75dB) EECS 247 Lecture 12: Data Converters 13bit Double-Loop Peak signal frequency Æ80kHz © 2006 H. K. Page 7 Data Converters EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 8 Data Converters • Stand alone data converters – Used in variety of systems – Example: Analog Devices AD9235 12bit/ 65Ms/s ADC- Applications: • Ultrasound equipment • IF sampling in wireless receivers • Hand-held scopemeters • Low cost digital oscilloscopes EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 9 Data Converters • Embedded data converters – Cost, reliability, and performance Æ integration of data conversion interfaces along with DSPs – Main challenges • Feasibility of integrating sensitive analog functions in technologies optimized for digital performance • Down scaling of supply voltage • Interference & spurious signal pick-up from on-chip digital circuitry • Portable applications dictate low power consumption EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 10 D/A Converter Transfer Characteristics MSB b1 b2 b3 • An ideal digital-toanalog converter: – Accepts digital inputs b1-bn – Produces either an analog output voltage or current – Assumption (will be revisited) • Uniform, binary digital encoding • Unipolar output ranging from 0 to VFS LSB ……..… bn V0 D/A Nomenclature: N = # of bits VFS = f u l l s cal e o u tp u t Δ = mi n . s t ep s iz e → 1L SB Δ= VFS 2N V o r N = lo g2 F S → r es ol u ti o n Δ EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 11 D/A Converter Transfer Characteristics MSB b1 b2 b3 N = # of bit s VFS = f u l l s cal e o u t p u t Δ = m i n . st ep s i z e → 1L S B Δ= LSB ……..… D/A bn V0 VFS 2N V0 = VFS N bi ∑ i i =1 2 N = Δ × ∑ bi × 2 N −i , i =1 bi = 0 or 1 binary-weighted EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 12 D/A Converter Exampe: D/A with 3-bit Resolution Exa mp l e : N = 3 MSB LSB b1 b2 b3 1 0 1 Ass ume VFS = 0 .8V In put cod e i s 1 01 V0 = Δ (b1 × 22 + b2 × 21 + b3 × 20 ) T hen : Δ =VF S / 23 = 0. 1V V0 D/A → V0 = 0.1V (1 × 22 + 0 × 21 + 1 × 20 ) = → V0 = 0.5V Note : MSB → VF S / 2 & L S B → VFS / 2 N EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 13 Ideal D/A Transfer Characteristic • Ideal DAC introduces no error! Analog Output VFS Ideal Response • One-to-one mapping VFS /2 from input to output Step Height (1LSB =Δ) VFS /8 000 001 010 011 100 101 110 111 EECS 247 Lecture 12: Data Converters Digital Input Code © 2006 H. K. Page 14 A/D Converter Transfer Characteristic • For an ideal analog-to-digital converter with uniform, binary digital encoding & a unipolar input range for 0 to VFS MSB b1 b2 b3 LSB ……..… bm Vin A/D w here N = # of b i t s VFS = f ul l scal e ou t put Δ = step s i ze Δ= VFS N ot e : D ( bi = 1,al l i ) → VFS − Δ 1 ⎞ ⎛ → VFS ⎜ 1 − ⎟ ⎝ 2N ⎠ 2N EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 15 Ideal A/D Transfer Characteristic Digital Output • Ideal ADC introduces error 111 Æ(+-1/2 Δ) Δ = VFS /2 N N= # of bits 110 101 100 011 • This error is called ``quantization error`` 010 001 1LSB Analog input 000 0 EECS 247 Lecture 12: Data Converters Δ 2Δ 3Δ 4Δ 5Δ 6Δ 7Δ © 2006 H. K. Page 16 Example: Non-Linear A/D Converter For Voice-Band Telephony Applications Coder Output (DIGITAL) Non-linear ADC and DAC used in voice-band CODECs • To maximize dynamic range with lower # of bits • Coding scheme called A-law & μ-law -VFS -VFS/2 -VFS/4 Coder Input (ANALOG) • Also called companding Ref: P. R. Gray, et al. "Companded pulse-code modulation voice codec using monolithic weighted capacitor arrays," IEEE Journal of Solid-State Circuits, vol. 10, pp. 497 - 499, December 1975. EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 17 Data Converter Performance Metrics • Data Converters are typically characterized by static, time-domain, & frequency domain performance metrics : – Static • • • • • Monotonicity Offset Full-scale error Differential nonlinearity (DNL) Integral nonlinearity (INL) – Dynamic • • • • • • Delay, settling time Aperture uncertainty Distortion- harmonic content Signal-to-noise ratio (SNR), Signal-to-(noise+distortion) ratio (SNDR) Idle channel noise Dynamic range & spurious-free dynamic range (SFDR) EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 18 Typical Sampling Process CT ⇒ SD ⇒ DT time Continuous Time Physical Signals Sampled Data (e.g. T/H signal) Clock "Memory Content" Discrete Time EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 19 Discrete Time Signals • A sequence of numbers (or vector) with discrete index time instants • Intermediate signal values not defined (not the same as equal to zero!) • Mathematically convenient, non-physical • We will use the term "sampled data" for related signals that occur in real, physical interface circuits EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 20 Uniform Sampling y(kT)=y(k) t= 1T k= 1 2T 2 3T 3 4T 4 5T 5 6T ... 6 ... • Samples spaced T seconds in time • Sampling Period T ⇔ Sampling Frequency fs=1/T • Problem: Multiple continuous time signals can yield exactly the same discrete time signal (aliasing) EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 21 Data Converters • ADC/DACs need to sample/reconstruct to convert from continuous time to discrete time signals and back • We distinguish between purely mathematical discrete time signals and "sampled data signals" that carry information in actual circuits • Question: How do we ensure that sampling/reconstruction fully preserve information? EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 22 Aliasing • The frequencies fx and Nfs ± fx, N integer, are indistinguishable in the discrete time domain • Undesired frequency interaction and translation due to sampling is called aliasing • If aliasing occurs, no signal processing operation downstream of the sampling process can recover the original continuous time signal! • Let's look at this in the frequency domain... EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 23 Sampling Sine Waves Voltage Time domain fs = 1/T time y(nT) Amplitude Frequency domain fs - fin fin EECS 247 Lecture 12: Data Converters fs + fin fs 2fs … f © 2006 H. K. Page 24 Signal scenario before sampling Amplitude Frequency Domain Interpretation fin fs /2 fs 2fs …….. f Discrete Time Amplitude Signal scenario after sampling Æ DT ÆSignals @ nfS ± fmax__signal fold back into band of interest ÆAliasing Continuous Time 0.5 EECS 247 Lecture 12: Data Converters f/fs © 2006 H. K. Page 25 How to Avoid Aliasing • • Must obey sampling theorem: fmax_Signal < fs/2 Two possibilities: 1. Sample fast enough to cover all spectral components, including "parasitic" ones outside band of interest- usually not practical 2. Limit fmax_Signal through filtering EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 26 Brick Wall Anti-Aliasing Filter Amplitude Filter Continuous Time 0 fs 2fs ... f Discrete Time 0 0.5 f/fs Sampling at Nyquist rate (fs=2fsignal) Æ required brick-wall anti-aliasing filters EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 27 Practical Anti-Aliasing Filter Amplitude Filter Continuous Time 0 fs/2 fs 2fs ... f • Practical filter: Nonzero "transition band" • In order to make this work, we need to sample faster than 2x the signal bandwidth • "Oversampling" EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 28 Practical Anti-Aliasing Filter Desired Signal Parasitic Tone Attenuation Continuous Time 0 B fs/2 0 B/fs 0.5 fs-B fs ... f Discrete Time EECS 247 Lecture 12: Data Converters f/fs © 2006 H. K. Page 29 Data Converter Classification • fs > 2fmax Nyquist Sampling – "Nyquist Converters" – Actually always slightly oversampled (e.g. CODEC fsigmax 3.4kHz Æ ADC sampling 8kHz) • fs >> 2fmax Oversampling – "Oversampled Converters" – Anti alias filtering is often trivial – Oversampling is also used to reduce quantization noise, see later in the course... • fs < 2fmax Undersampling (sub-sampling) EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 30 Sub-Sampling Amplitude BP Filter Continuous Time 0 fs ... f Discrete Time 0 0.5 f/fs • Sub-sampling Æ sampling at a rate less than Nyquist rate Æ aliasing • For signals centered @ an intermediate frequency Æ Not destructive! • Sub-sampling can be exploited to mix a narrowband RF or IF signal down to lower frequencies EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 31 Where Are We Now? Analog Input • We now know how to preserve signal information in CTÆDT transition Analog Preprocessing Sampling (+Quantization) A/D Conversion 000 ...001... 110 DSP D/A Conversion • How do we go back from DTÆ CT? Anti-Aliasing Filter ? Analog Postprocessing Analog Output EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 32 Ideal Reconstruction x(k) ⇒ x(t) • The DSP books tell us: x(t ) = ∞ ∑ x(k ) ⋅ g (t − kT ) k = −∞ g (t ) = sin( 2πBt ) 2πBt • Unfortunately not all that practical... EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 33 Zero-Order Hold Reconstruction • How about just creating a staircase, i.e. hold each discrete time value until new information becomes available? 1 Amplitude 0.6 0.2 -0.2 • What does this do to the frequency content of the signal? -0.6 -1 sampled data after ZOH 0 10 20 30 Time [μs] EECS 247 Lecture 12: Data Converters • Let's analyze this in two steps... © 2006 H. K. Page 34 1) DTÆ CT: Infinite Zero Padding Time Domain DT sequence Frequency Domain ... ... 0.5 Zero padded DT sequence Infinite Interpolation: CT Signal! f/fs ... ... 0.5/i 1.5/i 2.5/i f/fs 0.5fs 1.5fs 2.5fs f ... ... EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 35 2) Add a Hold Function ... ... Tp Ts • Hold pulses for Tp period • Using the Fourier transform of a rectangular impulse: H( f ) = Tp sin(πfT p ) Ts EECS 247 Lecture 12: Data Converters πfT p © 2006 H. K. Page 36 Hold Pulse Tp=Ts 1 0.9 | H ( f ) |= 0.8 0.7 Tp sin(πfT p ) πfT p Ts abs(H(f)) 0.6 0.5 0.4 0.3 0.2 0.1 0 0 0.5 1 1.5 f/fs 2 2.5 EECS 247 Lecture 12: Data Converters 3 © 2006 H. K. Page 37 ZOH Spectral Distortion 1 Continuous Time Pulse Train Spectrum X(k) 0.5 0 0 0.5 1 1.5 2 2.5 3 1 ZOH Transfer Function ("Sinc Distortion") ZOH 0.5 0 0 0.5 1 1.5 2 2.5 3 0 0.5 1 1.5 2 2.5 3 1 ZOH output, Spectrum of Staircase Approximation 0.5 0 f/fs EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 38 Smoothing Filter 1 Again: • A brick wall filter would be nice • Oversampling helps to reduce filter order 0.9 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 0 0.5 1 1.5 2 2.5 3 f/fs EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 39 Summary • Sampling theorem fs > 2fmax, usually dictates anti-aliasing filter • If theorem is met, CT signal can be recovered from DT without loss of information • ZOH and smoothing filter reconstruct CT from DT signal • Oversampling helps reduce order & complexity of anti-aliasing & smoothing filters EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 40 Next Topic Analog Input • Done with "Quantization in time" • Next: Quantization in amplitude Analog Preprocessing Anti-Aliasing Filter Sampling (+Quantization) A/D Conversion DSP 000 ...001... 110 D/A Conversion D/A+ZOH Analog Postprocessing Smoothing Filter Analog Output EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 41 Amplitude Quantization • Amplitude quantization Æ quantization “noise” • Static ADC/DAC performance measures – Offset – Gain – INL – DNL EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 42 Ideal ADC ("Quantizer") • Quantization step: Ideal converter with infinite # of bits ADC characteristics • Full-scale input range: -0.5Δ … (2N-0.5)Δ • E.g. N = 3 Bits Digital Output Code Δ (= 1 LSB) 7 6 5 4 3 2 1 0 -1 0 1 2 3 4 5 6 7 8 VFS Æ VFS= -0.5Δ to 7.5Δ ADC Input Voltage [ Δ] EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 43 Quantization Error • Difference between analog input and output of the ADC converted to analog via an ideal DAC • Called: :Quantization error Residue Quantization noise Vin Residue ADC EECS 247 Lecture 12: Data Converters Ideal DAC - Σ + εq (Vin ) © 2006 H. K. Page 44 • For an ideal ADC: • Quantization error is bounded by –Δ/2 … +Δ/2 for inputs within full-scale range Quantization error [LSB] Digital Output Code Quantization Error 7 6 5 4 3 2 1 0 -1 ideal converter with infinite bits ADC characteristics 0 1 0 1 2 3 4 5 6 7 8 2 3 4 5 6 ADC Input Voltage [Δ] 7 8 0.5 ADC Model Vin + Dout 0 -0.5 εq (Vin ) -1 EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 45 ADC Dynamic Range • Assuming quantization noise is much larger compared to circuit generated noise: D.R.Maximum = 10 log Full Scale Signal Power Quantization Noise Power • Crude assumption: Same peak/rms ratio for signal and quantization noise! Peak Full Scale Peak Quantization Noise V = 20 log FS = 20 log 2 N = 6.02 × N [ dB ] Δ D.R.Maximum = 20 log Question: What is the quantization noise power? EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 46 Quantization Error Let us assume Vin is a ramp signal with amplitude equal to ADC full-scale Vin_Ramp VFS Time Quantization error [LSB] Δ/2 Time 0 −Δ/2 Note: Quantization error waveformÆ periodic and also ramp EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 47 Quantization Error Need to find the rms value for quantization error waveform: ε eq2 = = 1 T +T / 2 ∫ −T / 2 Δk2 + Δ / 2k k −Δ / 2k → ε eq2 = → ε eq = ∫ 2 (k × t ) d t = Δ k + Δ / 2k ∫ −Δ / 2k 2 12 Æ Independent of k −Δ/2k 0 Δ/2k Time −Δ/2 Δ 12 εq=k.t Δ/2 2 t dt Δ2 Quantization error (k × t ) d t In general above equation applies if: • Input signal much larger than 1LSB • Input signal busy • No signal clipping EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 48 Quantization Error PDF • • • Uniformly distributed from –Δ/2 … +Δ/2 provided that – Busy input – Amplitude is many LSBs – No overload Zero mean Variance e2 = +Δ / 2 2 e Δ2 ∫ de = 12 −Δ / 2 Δ • Not Gaussian! Pdf 1/Δ +Δ/2 -Δ/2 Ref: W. R. Bennett, “Spectra of quantized signals,” Bell Syst. Tech. J., vol. 27, pp. 446-72, July 1988. error B. Widrow, “A study of rough amplitude quantization by means of Nyquist sampling theory,” IRE Trans. Circuit Theory, vol. CT-3, pp. 266-76, 1956. EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 49 Signal-to-Quantization Noise Ratio • If certain conditions are met (!) the quantization error can be viewed as being "random", and is often referred to as “noise” • In this case, we can define a peak “signal-to-quantization noise ratio”, SQNR, for sinusoidal inputs: 2 1 ⎛ 2N Δ ⎞ ⎜ ⎟ 2 ⎜⎝ 2 ⎟⎠ = 1.5 × 22N SQNR = Δ2 e.g. N 8 12 16 20 12 = 6.02N + 1.76 dB SQNR 50 dB 74 dB 98 dB 122 dB Ac curate for N>3 • Actual converters do not quite achieve this performance due to other errors, including – Electronic noise – Deviations from the ideal quantization levels EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 50 SQNR Measurement SQN R peak = 6.02N + 1.76 dB Ideal 20log(SQNR) Realistic 6dB/octave 0dB Dynamic Range Vin [dB] EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 51 Static, Ideal Macro Models ADC Vin + εq Dout DAC Din EECS 247 Lecture 12: Data Converters Vout © 2006 H. K. Page 52 Cascade of Data Converters ADC Vin + DAC Vout εq DAC ADC Din + εq EECS 247 Lecture 12: Data Converters Dout © 2006 H. K. Page 53 Static Converter Errors Deviations of characteristic from ideal – Offset – Full scale error – Differential nonlinearity, DNL – Integral nonlinearity, INL EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 54 ADC Offset Error DAC Ref: “Understanding Data Converters,” Texas Instruments Application Report SLAA013, Mixed-Signal Products, 1995. EECS 247 Lecture 12: Data Converters ADC © 2006 H. K. Page 55 Full Scale Error Actual full scale point Ideal full scale point DAC Ideal full scale point Full scale error Full scale error Actual full scale point EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 56 Offset and Full Scale Errors • Alternative specification in % Full Scale = 100% * (# of LSB value)/ 2N • Gain error can be extracted from offset & full scale error • Non-trivial to build a converter with extremely good gain/offset specs • Typically gain/offset is most easily compensated by the digital pre/post-processor • More interesting: Linearity measuresÆDNL, INL EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 57 Offset and Full-Scale Error 7 Digital Output Code Note: Æ For further measurements (DNL, INL) connecting the endpoints & deriving ideal codes based on the non-ideal endpoints elliminates offset and fullscale error ADC characteristics ideal converter 6 Full-scale error 5 4 3 2 1 Offset error 0 -1 0 EECS 247 Lecture 12: Data Converters 1 2 3 4 5 6 ADC Input Voltage [LSB] 7 8 © 2006 H. K. Page 58 ADC Differential Nonlinearity DNL = deviation of code width from Δ (1LSB) ADC characteristics ideal converter 8 7 -0.4 LSB DNL error Æ Endpoints connected Æ Ideal characterisctics derived Æ DNL measured Digital Output Code 6 5 4 3 0 LSB DNL error 2 1 +0.4 LSB DNL error 0 -1 0 1 2 3 4 5 6 7 8 9 ADC Input Voltage [Δ] EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 59 ADC Differential Nonlinearity • Ideal ADC transitions point equally spaced by 1LSB • For DNL measurement, offset and full-scale error is eliminated • DNL [k] (a vector) measures the deviation of each code from its ideal width • Typically, worst-case DNL along with the vector for the entire code is reported EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 60 ADC Differential Nonlinearity Example A 3bit ADC is designed to have an ideal LSB=0.1V The measured transitions levels for the end product is shown in the table below, compute the DNL Transition # Ideal transition point [V] Real transition point [V] 1 0.05 0.02 2 0.15 0.13 3 0.25 0.2 4 0.35 0.37 5 0.45 0.42 6 0.55 0.5 7 0.65 0.68 EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 61 ADC Differential Nonlinearity Example 1- Find the average code width (LSB size) Code # Code Width [V] DNL [LSB] LSB=(Last transition-first transition)/(2N-2) 0 - - 1 0.11 0 LSB=(0.68-0.02)/6=0.11V 2 0.07 -0.37 2- Find all code widths 3 0.17 0.55 Width[k]=Transition[k+1]Transition[k] 4 0.05 -0.55 3- Divide code width by LSB 4- Find DNL: 5 0.08 -0.27 6 0.18 0.64 DNL[k]=(W[k]-LSB 7 - - EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 62 ADC Differential Nonlinearity Example 1 Max. DNL DNL [LSB} 0.5 0 -0.5 -1 0 1 2 3 4 5 6 7 Code # Code # Code Width [V] 0 - - 1 0.11 0 2 0.07 -0.37 3 0.17 0.55 4 0.05 -0.55 5 0.08 -0.27 6 0.18 0.64 7 - - EECS 247 Lecture 12: Data Converters DNL [LSB] © 2006 H. K. Page 63 ADC Differential Nonlinearity Examples ADC characteristics ideal converter 8 7 6 5 4 3 Missing code (+0.5/-1 LSB DNL) 2 1 0 Digital Output Code Digital Output Code 7 -1 ADC characteristics ideal converter 8 6 5 4 3 2 Non-monotonic (> 1 LSB DNL) 1 0 0 1 2 3 4 5 6 7 8 9 ADC Input Voltage [Δ] EECS 247 Lecture 12: Data Converters -1 0 1 2 3 4 5 6 7 8 9 ADC Input Voltage [Δ] © 2006 H. K. Page 64 ADC DNL • DNL=-1 implies missing code • For an ADC DNL < -1 not possible • Can show: al l i ∑ DN L[i ] = 0 • For a DAC DNL can be < -1 EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 65 DAC Differential Nonlinearity • To find DNL for DAC – Draw end-point line from 1st point to last – Find ideal LSB size – Find segment sizes: segment [m]=V[m]-V[m-1] DN L[ m] = s egment[ m] − V [ L SB ] V [ L SB ] • Unlike ADC DNL, for a DAC DNL can be <-1LSB EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 66 DAC Differential Nonlinearity EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 67 Impact of DNL on Performance • Same as a somewhat larger quantization error, consequently degrades SQNR • How much – later in the course... • People sometimes speak of "DNL noise", i.e. "additional quantization noise due to DNL" EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 68 ADC Integral Nonlinearity INL = deviation of code transition from its ideal location Digital Output Code • A straight line through the endpoints is usually used as reference, i.e. offset and full scale errors are ignored in INL calculation 7 6 5 -1 LSB INL 4 3 • Ideal converter steps is found for the endpoint line, then INL is measured 2 • Note that INL errors can be much larger than DNL errors and vice-versa 0 1 -1 0 1 2 3 4 5 6 ADC Input Voltage [Δ] EECS 247 Lecture 12: Data Converters 7 8 © 2006 H. K. Page 69 ADC Integral Nonlinearity Best Fit versus End-Point • End-Point – Ideal converter steps is found for the endpoint line, then INL is measured • Best-Fit +1/2 LSB INL 7 Digital Output Code – A straight line through the endpoints is used as reference, i.e. offset and full scale errors are ignored in INL calculation – A best-fit line (in the leastmean squared sense) – Ideal converter steps is found then INL is measured Note: Typically INL smaller for best-fit compared to end-point EECS 247 Lecture 12: Data Converters 6 5 -1/2 LSB INL Best Fit 4 3 2 1 0 -1 0 1 2 3 4 5 6 ADC Input Voltage [Δ] 7 8 © 2006 H. K. Page 70 ADC Differential Nonlinearity Example Code # Can show: IN L[ m] = m −1 ∑ i =1 DNL [LSB] INL [LSB] 0 - - 1 0 0 Æ INL is found by computing the cumulative sum of DNL 2 -0.37 0 3 0.55 -0.37 For the previous example: Note: INL for the last code=0 4 -0.55 0.18 5 -0.27 -0.37 6 0.64 -0.64 7 - 0 DN L[i ] EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 71 ADC Differential Nonlinearity Example Max. DNL 1 Code # DNL [LSB] 0.5 INL [LSB] 0 - - 1 0 0 2 -0.37 0 1 3 0.55 -0.37 0.5 4 -0.55 0.18 0 5 -0.27 -0.37 6 0.64 -0.64 - 0 0 -0.5 -1 INL [LSB] DNL [LSB] 0 1 2 3 4 -0.5 -1 0 1 2 3 4 5 Max. INL 5 6 6 7 7 7 Code # EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 72 DAC Integral Nonlinearity EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 73 DAC DNL and INL * Ref: “Understanding Data Converters,” Texas Instruments Application Report SLAA013, Mixed-Signal Products, 1995. EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 74 Example: INL & DNL Large INL & Small DNL Large DNL & Small INL EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 75 Monotonicity • Monotonicity guaranteed if | INL | ≤ 0.5 LSB The best fit straight line is taken as the reference for determining the INL. • This implies | DNL | ≤ 1 LSB EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 76 Non-Monotonic DAC DN L[ m] = Analog Output [LSB] s eg ment[ m] − V [ L SB ] V [ LSB] 7 s eg ment[ 4 ] − V [ L SB ] 6 DN L[ 4 ] = V [ LSB] − 0. 5 − 1 = = − 1 . 5[ L S B ] 1 2. 5 − 1 DN L[ 5] == = 1.5[ L SB ] 1 5 • DNL< -1LSB for a DAC Æ Non-monotonicity • When can nonmonotonicity can cause major problems? 2 4 3 1 Digital Input 0 000 001 010 011 100 101 110 111 EECS 247 Lecture 12: Data Converters © 2006 H. K. Page 77 Non-Monotonic ADC • Code 011 associated with two 111 transition levels ! 110 Digital Output 101 • For non-monotonic ADC ÆDNL not defined 100 011 010 001 Analog input 000 0 EECS 247 Lecture 12: Data Converters Δ 2Δ 3Δ 4Δ 5Δ 6Δ 7Δ © 2006 H. K. Page 78