AND9083 - MOSFET Gate-Charge Origin and its Applications

advertisement

AND9083/D

MOSFET Gate-Charge

Origin and its Applications

Introduction

www.onsemi.com

APPLICATION NOTE

32 V

+

ID

0 à 10 V

+

−

VDS

−

VGS

10

9

8

ID = 30 A, VDS = 5 V

30 A

7

6

5

ID = 5 A, VDS = 30 V

4

Figure 2. Inductive Switching

3

2

QSW

35

VGS, GATE−TO−SOURCE VOLTAGE (V)

10

1

0

0

5

10

15

20

25

30

35

QG, TOTAL GATE CHARGE (nC)

Figure 1. NTD5805N Gate-to-Source Voltage vs.

Total Charge

Inductive Switching

In switch-mode power supplies, MOSFETs switch

inductive loads. Figure 2 shows a basic buck circuit with high

side MOSFET turn on transition. Before the high side

MOSFET is turned on, inductor current is flowing through the

low side MOSFET’s body diode (VBD). The turn-on transition

is broken down into three regions (Figure 3). These regions

will be individually explained. Figure 4 shows the transition

through these regions in terms of output characteristics. Gate

charge can be derived from the non-linear capacitance

curves, which are fully characterized at a range of VDS

(VGS = 0 V) and VGS (VDS = 0 V) as shown in Figure 5.

© Semiconductor Components Industries, LLC, 2016

February, 2016 − Rev. 2

9

8

ID

VDS

30

QG

7

6

20

5

VGP

15

4

3

2

25

10

VTH

A

1

0

B

C

5

0

0

ID, DRAIN CURRENT (A),

VDS, DRAIN−SOURCE VOLTAGE (V)

VGS, GATE−TO−SOURCE VOLTAGE (V)

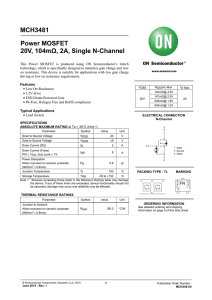

Engineers often estimate switching time based on total

drive resistances and gate charge or capacitance. Since

capacitance is non-linear, gate charge is an easier parameter

for estimating switching behavior. However, the MOSFET

switching time estimated from datasheet parameters does not

normally match what the oscilloscope shows. This is due to

differences between the parameters taken from the datasheet

and the application conditions. For example, in Figure 1 the

gate charge of NTD5805N was characterized at two

different conditions and results varied greatly. If datasheet

values are characterized at conditions different from the

user, the differences will introduce error in the estimation.

This article will explain how to better estimate gate charge

from datasheets and their applications. For simplicity in this

article, power MOSFET NTD5805N’s datasheet [1] is used

with circuit conditions of 32 V and 30 A.

10

20

30

QG, TOTAL GATE CHARGE (nC)

Figure 3. Gate-to-Source Voltage

and Switching vs. Total Charge

1

Publication Order Number:

AND9083/D

AND9083/D

VGS = 5.5 V − 10 V

100

3000

VGS = 5.2 V

80

2500

C, CAPACITANCE (pF)

ID, DRAIN CURRENT (A)

90

5V

70

60

4.5 V

50

40

C

4.2 V

VGP

B

30

4V

20

1

2

3

30

1000

A

Coss

B

3.5 V

0

C

1500

500

A

10

0

Ciss

2000

Crss

0

10

40

5

0

VGS

VDS, DRAIN−TO−SOURCE VOLTAGE (V)

5

10

15

20

25

30

35

40

VDS

GATE−TO−SOURCE OR DRAIN−TO−SOURCE VOLTAGE (V)

Figure 4. On-Region Characteristics for Different

Gate-to-Source Voltages

Figure 5. Capacitance Variation

Region A: MOSFET QGS

Region C: MOSFET Remaining Total Gate Charge

This is the region where gate-to-source voltage (VGS)

rises from 0 V to its plateau voltage (VGP). When the gate

rises from 0 V to its threshold voltage (VTH), the MOSFET

is still off with no drain current (ID) flow and drain-to-source

voltage (VDS) remains clamped. Once gate voltage reaches

VTH, the MOSFET starts conducting and ID rises. Its VDS is

still clamped to VDD + VBD until all inductor current is

being supplied by the MOSFET. In this region, gate current

is used to charge the input capacitance (Ciss) with its VDS

being clamped. Since voltage across gate-to-drain changes

from VDD to VDD – VGP, charge is stored from the input

capacitance curve at that range. It can be approximated by

Equation 1.

This is the region where the MOSFET enters into ohmic

mode operation as seen in the ID−VDS curve (Figure 4). VGS

rises from VGP to driver supply voltage (VGDR). Both ID and

VDS remain relatively constant. ID is still clamped by the

inductor current. As VGS increases, the channel

(VDS = I * RDS(ON)) continue to be more enhanced and VDS

dropped slightly. The charge needed is shown as region C in

Figure 5 and can be calculated by Equation 3.

Q GS ^

ŕ

V DD

V DD * V GP Ciss(V DS) @ dV

QC ^

DD * V GP

GP

GP

Ciss(V GS) @ dV

(eq. 3)

It was explained above how different sections of gate

charge are formed. Circuit conditions determine gate charge

boundaries between regions A, B and C (Figure 6). The

range is set by VDD and VGDR. VGP can be found from

ID−VDS curves at inductor current (ID) and supply voltage

(VDD). With these three voltages found, gate charge equals

to area under those capacitance regions. An example is

shown in Table 1 employing methodology described the

same circuit conditions as characterization data in Figure 1

using only simple estimations. Total gate charge (QGTOT) is

the total amount charge stored by the MOSFET on its gate

up to the driver voltage. Switching gate charge (QSW) is the

amount charge needed to complete ID and VDS transitions.

(eq. 1)

This is the region where VGS is held at VGP and remains

flat. ID clamps to inductor current and VDS clamping effect

is gone, MOSFET’s VDS starts to drop. It can be seen from

ID−VDS curve (Figure 4) that VGS remains relatively

constant at fixed ID with varying VDS. This is the origin of

the flat plateau seen on the gate charge curve. During this

region, the gate current is used to charge the reverse transfer

capacitance (Crss). VDS is decreasing from VDD + VBD to

ID * RDS(ON). Thus the voltage across Crss (gate-to-drain

capacitance) changes from {(VDD + VBD) − VGP} to

{(ID * RDS(ON)) − VGP}. The polarity of voltage is reversed.

Charge (Equation 2) needed for this transition is shown as

the area under region B capacitance curve of Figure 5.

ŕ V0

V

)ŕ

0

GDR

Getting the Gate Charge for Different Conditions

Region B: MOSFET QGD

Q GD ^

ŕ VV

Crss(V DS) @ dV )

(eq. 2)

Crss(V GS) @ dV

www.onsemi.com

2

AND9083/D

GATE−TO−SOURCE OR DRAIN−TO−SOURCE VOLTAGE (V)

VGS

VDS

3000

C, CAPACITANCE (pF)

2500

2000

C

1500

A

1000

500

B

0

VGDR

VGP(ID)

VDD − VGP(ID)

VDD

Figure 6. Circuit Parameters Effects

Table 1. ESTIMATION OF GATE CHARGE BASED ON METHOD DESCRIBED

Parameters

VDD = 30 V, ID = 5 A

VDD = 5 V, ID = 30 A

Refer to

VGP

3.6 V

4.2 V

ID – VDS Curve

Region A − Charge

3.6 V * 1.7 nF ≈ 6.1 nC

4.2 V * 1.9 nC ≈ 8.0 nC

Region B − Charge

(30 V – 3.6 V) * 0.2 nF +

3.6 V * 1.1 nF ≈ 9.2 nC

(5 V – 4.2 V) * 0.4 nF +

3.6 V * 1.1 nF ≈ 4.9 nC

Region C − Charge

(10 V – 3.6 V) * 2.7 nF ≈ 18 nC

(10 V – 4.2 V) * 2.7 nF ≈ 15.95 nC

QGTOT

33 nC

29 nC

Capacitance Curve

Sum A, B & C

VTH

2.7 V

2.7 V

Datasheet Value

QSW

(3.6 V – 2.7 V) / 3.6 V * 6.1 nF +

9.2 nC ≈ 11 nC

(4.2 V – 2.7 V) / 4.2 V * 8.0 nF +

4.9 nC ≈ 7.8 nC

QA(after VTH) + QB

32 V

Resistive Switching

LED and heating coil are examples of resistive switching.

The main difference between inductive and resistive

switching is that there is no clamping of drain current

involved. Before reaching its threshold voltage, the FET is

off. When the MOSFET starts to turn-on in the saturation

region, VDS is dependent on resistive load and voltage

supply. Once the FET is in ohmic mode, the MOSFET and

the load become a simple resistor divider. There is no flat

plateau region as both VDS and ID are changing resulting in

increasing VGS (Figure 9 region E). Fortunately, QSW and

QGTOT are unchanged from inductive switching.

32 / 30 W

+

0 à 10 V

+

−

ID

VGS

Figure 7. Resistive Switching

www.onsemi.com

3

VDS

−

AND9083/D

QSW

35

ID

VDS

8

30

25

7

6

20

5

4

15

3

10

2

VTH

F

E

1

0

5

D

0

0

10

20

100

90

ID, DRAIN CURRENT (A)

VGS, GATE−TO−SOURCE VOLTAGE (V)

9

ID, DRAIN CURRENT (A),

VDS, DRAIN−SOURCE VOLTAGE (V)

10

80

70

60

50

40

F

30

E

20

10

0

30

D

0

QG, TOTAL GATE CHARGE (nC)

10

20

30

40

VDS, DRAIN−TO−SOURCE VOLTAGE (V)

Figure 8. Gate-to-Source Voltage and Switching

vs. Total Charge (Resistive Switching)

Figure 9. On-Region Characteristics for Different

Gate-to-Source Voltages

Gate Charge Applications

charge (QSW) is the amount of current the gate driver needed

to supply to complete the switching transitions of drain

voltage and current. Gate charge loss (PQG) is power

dissipated due to charging and discharging of the gate.

One important aspect of MOSFET applications is the

power losses. There are several power loss components.

Conduction loss is power dissipated in the resistive element

(RDSON) of the channel. Switching loss (PSW) is power

dissipated in switching current and voltage. Switching gate

P QG + Q GTOT@VGDR @ V GDR @ F SW

(eq. 4)

Q SW + Q GS(afterVth) ) Q GD

(eq. 5)

T SW(ON) + Q SWń

ǒ

Ǔ

ǒ

Ǔ

V GDR * V GP

V GP

, T SW(OFF) + Q SWń

R DR ) R G

R DR ) R G

(eq. 6)

P SW(inductive) + 0.5 @ V DD @ I D @ ǒT SW(ON) ) T SW(OFF)Ǔ @ F SW

(eq. 7)

P SW(resistive) + 0.25 @ V DD @ I D @ ǒT SW(ON) ) T SW(OFF)Ǔ @ F SW

(eq. 8)

inductive switching or short-circuit performance can also be

evaluated.

Derivations above do not apply to zero voltage switching

applications. For example in synchronous rectification,

MOSFET has a negative diode voltage drop across VDS

(body diode conduction) before it is turned on. They can still

be derived from the capacitances (VGS side) and ID−VDS

curve using the same idea.

40

QGTOT@10 VGS

GATE CHARGE (nC)

35

Conclusion

With different circuit conditions, it has been shown how

datasheet gate charge parameters changes. Only simple

mathematics is needed in getting the right gate charge.

The origins of gate charge are analytically explained.

Through understanding of MOSFET gate charge, more

accurate estimations can be made in designing for different

circuit conditions (Figure 10). Trade offs are evaluated in

selecting gate drive schemes. A lower gate drive voltage

would save some energy but must be balanced between

higher on-resistance. Using methods described by D. Lee in

[2], extreme operating conditions like repetitive unclamped

30

25

ID = 1 A

ID = 50 A

20

15

QSW

10

5

0

0

10

20

30

VDS, DRAIN−TO−SOURCE VOLTAGE (V)

Figure 10. NTD5805N Gate Charge at Various

Conditions

www.onsemi.com

4

40

AND9083/D

APPENDIX A: ESTIMATION WITHOUT CAPACITANCE-vs-VGS CURVE

3000

C, CAPACITANCE (pF)

2500

Ciss

2000

1500

1000

Coss

500

0

10

5

Vgs

Crss

0

5

10

Vds

15

20

25

30

35

40

GATE−TO−SOURCE OR DRAIN−TO−SOURCE VOLTAGE (V)

Figure 11. NTD5805N Capacitance Curves

Since most of the MOSFETs datasheet are without

Capacitance-vs-VGS curve (shaded part of the Figure 11),

estimation will have to be made based on the available

information. The missing Capacitance-vs-VGS curves will

concern region B and region C.

Figure 12. Circuit Parameters Effects

For region C, we can estimate the gate charge after

VGP(ID) due to its constant capacitance.

For region B, we can assume VGP(ID) are relative constant

in modern trench MOSFET devices. Due to the high trench

density (high transconductance), a large change in drain

current, ID, only resulted in small increase in gate plateau

voltage, VGP(ID).

www.onsemi.com

5

AND9083/D

For example using 40 V NTMFS5C442NL,

220

VDS = 3 V

160

200

3.8 V

180

160

ID, DRAIN CURRENT (A)

ID, DRAIN CURRENT (A)

180

4.0 V

10 V to 4.5 V

3.6 V

140

3.4 V

120

3.2 V

100

80

3.0 V

60

2.8 V

40

140

120

100

80

TJ = 25°C

60

40

TJ = 125°C

20

20

0

TJ = −55°C

0

0

0.5

1.0

1.5

2.0

2.5

3.0

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

VDS, DRAIN−TO−SOURCE VOLTAGE (V)

VGS, GATE−TO−SOURCE VOLTAGE (V)

Figure A. On-Region Characteristics

Figure B. Transfer Characteristics

4.0

Figure 13. NTMFS5C442NL Datasheet Curves

for every 15 A increase or decrease in drain current. We can

conclude that VGP for modern trench MOSFET devices are

relative constant due to high transconductance.

From Figure A and B of NTMFS5C442NL, we can see

that when Gate-to-Source voltage, VGS, changed from 3.0 V

to 3.2 V the drain current, ID, increase by 30 A. Therefore,

it implied gate plateau VGP change by approximately 0.1 V

Table 2. NTMFS5C442NL DATASHEET PARAMETERS

Parameter

Symbol

Test Condition

Min

Typ

Max

Total Gate Charge

QG(TOT)

VGS = 4.5 V, VDS = 32 V, ID = 50 A

−

23

−

Total Gate Charge

QG(TOT)

VGS = 10 V, VDS = 32 V, ID = 50 A

−

50

−

Threshold Gate Charge

QG(TH)

−

5.0

−

−

9.8

−

−

6.7

−

−

3.1

−

Gate-to-Source Charge

QGS

Gate-to-Drain Charge

QGD

Plateau Voltage

VGP

VGS = 4.5 V, VDS = 32 V, ID = 50 A

Figure 14. NTMFS5C442NL Capacitance Curves with Datasheet Test Conditions

www.onsemi.com

6

Unit

nC

V

AND9083/D

Region A = QGS = 9.8 nC (estimated from curve = 3.1 V * 3100 pF = 9.6 nC)

Region B = QGD = 6.7 nC

Region C = QGTOT – QGS – QGD = 33.5 nC

Calculate for Different Test Conditions

For example at VGS = 6 V, VDS = 20 V, ID = 20 A:

Figure 15. NTMFS5C442NL Capacitance Curves with New Test Conditions

Region A = 3.1 V * 3100 pF = 9.6 nC

Region B = 6.7 nC – (12 V * 100 pF) = 5.5 nC

Region C = 33.5 nC / (10 V – 3.1 V) * (6 V – 3.1 V) = 14.1 nC

Figure 16. Graphic Representation of Change in Above NTMFS5C442NL Estimation

www.onsemi.com

7

AND9083/D

Figure 17. Gate Charge Comparison between Test Conditions

The change in gate change can be seen in Figure 16 with

new test condition in shaded regions.

REFERENCES

[1] ON Semiconductor, “Power MOSFET 40 V

NTD5805N Datasheet”,

http://www.onsemi.com/pub_link/Collateral/

NTD5805N−D.PDF

[2] ON Semiconductor, “MOSFET Transient Junction

Temperature Under Repetitive UIS/Short-Circuit

Conditions”,

http://www.onsemi.com/pub_link/Collateral/

AND9042−D.PDF

[3] ON Semiconductor, “Power MOSFET 40 V

NTMFS5C442NL Datasheet”,

http://www.onsemi.com/pub_link/Collateral/

NTMFS5C442NL-D.PDF

ON Semiconductor and the

are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed

at www.onsemi.com/site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation

or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets

and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each

customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended,

or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which

the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or

unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and

expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim

alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable

copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81−3−5817−1050

www.onsemi.com

8

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

AND9083/D