HAL, Inc.

advertisement

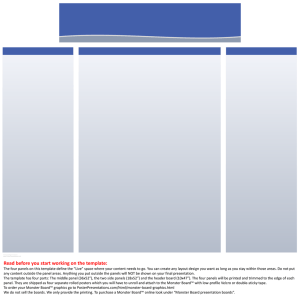

HAL, Inc.1 1. Background It is May 1992. HAL, Inc. is a major manufacturer of computers and computer components. In their Lubbock, TX plant they make printed circuit boards (PCB's, also referred to as ``panels''), which are used by other plants in the company in a variety of computer products. The Lubbock plant, built in 1982, represents an $80 million investment and has approximately 450,000 square feet of manufacturing space. The plant makes two families of products: 1. Small Panels: 10" x 15" panels are the original product of the facility and are used primarily for mainframe computer cards. There are roughly 40,000 different types of small panels, most of which are made for replacement parts in older computers. The overall demand for small panels is gradually declining. 2. Large Panels: 19.5" x 24" panels are a newer product, introduced in 1987, used primarily for personal computer cards. The larger size serves to reduce the cost per card and therefore most new cards are produced in this format. There are currently about 150 different types of large panel, but this number is steadily increasing. Both product families follow the same basic sequence of manufacturing operations, which is as follows: • • • • • • • • • • Treater Process: woven fiberglass cloth is impregnated with epoxy to make ``prepreg'', the insulator used in multilayer printed circuit boards. Lamination: layers of copper and prepreg are pressed together to form cores (blank boards). Machining: the cores are trimmed to size. Circuitize: through a photographic exposing and subsequent etching process, circuitry is produced in the copper layers of the blanks, giving the cores ``personality'' (i.e., a unique product character). Optical Test and Repair: the circuitry is scanned optically for defects, which are repaired if not too severe. Drilling: Holes are drilled in the boards to connect circuitry on different planes. (Note - that circuitized boards may return to the Lamination process to build up multi-layer boards). Copper Plate: the boards are run through a copper plating bath, which deposits copper inside the holes, thereby connecting the circuits on different planes. Pro-Coat: a protective plastic coating is applied to the boards. Sizing: boards are cut to final size. In most cases, multiple cards are manufactured on the same board and are cut into individual cards at the sizing step. Depending on the size of the card, there could be as few as two cards on a panel, or as many as twenty. End-of-Line-Test: an electrical test of each board's functionality is performed. Some of these processes (Treater, Lamination, Copper Plate) are shared between the two product families. Because of volumes and because it is difficult to switch between the two panel sizes, the other processes have been dedicated to a single product family (e.g., there are separate circuitize lines for 10 x 15's and and large panels). Before 1990, the Large Panel Line had such low volumes and such a small range of part numbers that it was not a major problem. Order acceptance and scheduling were handled by the Production Control Department. The Manufacturing Engineering Department kept track of capacity data and studied equipment and process improvements. The Manufacturing Department ran the line and, because the number of products was small, became accustomed to a de-facto rule of running only one part number per day on a process. This made managing the line easy, since few changeovers were required, demand for consumables was predictable, and operators could develop a strong sense of pacing. By 1990, however, the number of large panels had increased to around 100 and the de-facto rule of ``one product per day'' was no longer viable (although managers and operators were still fond of citing it as a goal). Capacity was estimated by Manufacturing Engineering to be 2000 panels per day, but a more typical daily output was around 1 Wallace J. Hopp 1996 1 1000 panels per day.2 In addition, although the actual amount of processing time required to make a printed circuit board was less than one day, manufacturing cycle times had steadily grown over time and were averaging close to 35 days at this point in time and customer service (the fraction of orders delivered on time) was running at about 50\%. Just prior to these events, the HAL Corporation had begun promoting the use of just-in-time concepts within its plants. Linda Brown, an internal consultant, was charged with implementing JIT in the Lubbock plant. She chose to concentrate on the more established 10 x 15 Line and wrote several documents describing basic JIT principles, held workshops with the personnel in charge of the line, and gave frequent reports to upper management on the sorry state of the line. However, Linda was promoted to a position outside the Lubbock facility before any concrete action plan was evolved. No attention at all was devoted to the Large Panel Line. The net result was that the Lubbock management team was left with a deep cynicism about the applicability of JIT to their system. In the fourth quarter of 1990, a new plant manager, Salvatore Petitto, took over the plant. Convinced that the plant was producing well below its capacity−he often cited Manufacturing Engineering capacity estimates−he summarily increased the target capacity for the large panel line by 50\% to 3000 panels per day. He also instituted a policy of holding a 4:00 meeting of all first line managers and directly confronted those who failed to make throughput numbers or had excessive WIP in their sectors. Mr. Petitto's first focus was Pro-Coat, which had been seriously underperforming for months and had been using an outside vendor (at a cost of roughly $14 per panel) to make up capacity shortfalls. Through a combination of additional staffing and procedural changes, Pro-Coat had been able to increase throughput from roughly 1200 boards per day to 2800 boards per day between December 1990 and April 19913 He then turned his attention to Circuitize, which was also experiencing throughput problems and, even more seriously, frequently had in excess of a week's worth of WIP in it. This time, quality improvements and procedural changes were implemented that improved throughput slightly, but reduced WIP in half by the early 1992. After these two successes, Mr. Petitto's policy of holding 4:00 meetings seemed to lose some of its momentum. Despite a few additional staffing and equipment additions, average throughput for the entire large panel line had stalled at around 2400 panels per day and cycle time in the line was still close to 30 days. Mr. Petitto began to challenge the first line managers to adopt more JIT mechanisms, but encountered serious resistance, largely as a result of the negative experience with JIT two years earlier. Other problems that surfaced in the meetings included: • Manufacturing consistently held that the schedules prepared by Production Control were a joke. Production Control responded that they were merely using the customer orders (customers were exclusively other HAL plants that ``stuffed'' the raw circuit boards) and the approved MRP system to generate releases and due dates. The problem, they contended, was that Manufacturing constantly perverted the schedule (by means of expediters who re-prioritized work already in the plant) to try to meet the needs of high-priority customers. • No single process center was a consistent source of the majority of trouble. During one interval, the Copper Plater was down for almost two weeks, building a huge queue and ruining schedule performance. Soon afterward, a large buildup of WIP occurred at Drills. Then a problem with two of the Lamination Presses caused the line to run out of the appropriate core blanks, so that although there was plenty of WIP in the line, the WIP required to meet 2 The capacity calculations made by Manufacturing Engineering were complicated by the fact that different boards required different amounts of processing at different stations. To compensate, complexity factors were defined, which represented the number of standard panel equivalents of a given board. This was done by arbitrarily defining one of the of the boards to have a complexity factor of 1.0 and then defining the complexity factors of the other boards to be the ratio of time required at Drilling to that required by the standard board. For instance, a board that required twice as much time at Drills as the standard board would have a complexity factor of 2.0. This system was chosen because it was generally felt that Drills was a bottleneck. However, because rates of other processes were also a function of board type, it was recognized that the bottleneck would ``float.'' Considerable controversy about the identity of the ``true bottleneck'' existed among the managers and engineers. 3 Actual throughput has not always achieved the 2800 boards per day rate due to failure of the rest of the line to produce sufficient input to Pro-Coat. However, when there has been sufficient WIP, Pro-Coat has been able to achieve the 2800 rate on a consistent basis 2 schedule was not available. This type of occurance was cited as evidence that the bottleneck ``floated'', making the line exceedingly difficult to manage. Mr. Pettito was unable to identify an obvious candidate for focused attention as he had done with Pro-Coat and Circuitize. • Manufacturing complained that the capacity numbers generated by Manufacturing Engineering, now at 3000 panels per day were unrealistic. However, when engineers from Manufacturing Engineering demonstrated their calculations, involving rate data from the equipment manufacturers adjusted by 14 different detractors (setups, operator efficiency, down time, yield loss, etc.), Manufacturing personnel were unable to give convincing arguments as to why these numbers were unreasonable. But, they argued, 3000 (standard) panels per day must be wrong since this rate had never been achieved in the history of the Large Panel Line. Mr. Petitto countered that this merely showed that Manufacturing was not doing its job. Moreover, he contended that if the target rate were reduced, workers wouldn't have incentive to strive to get better. • Managers in Circuitize complained that the continual evolution of the products prevented them from stabilizing their processes. As one of them commented, ``As soon as we get decent yields for boards with n lines per inch, we get products with 2n lines per inch and our problems start all over again.'' • Managers in End-of-Line Test complained that there had been periods of high yield loss and/or rework due to problems that should have been caught earlier in the process. As one of them pointed out ``When we lose a finished multi-layer board, we're throwing away something like $200. It would have been more like $2 if we'd caught it at the core blank level, or $20 if we caught it at the first pass through Circuitize.'' Everyone agreed that the extreme pressure to get volumes up might be encouraging people to push work through rather than stop it for anything other than the most glaring quality problems. • Almost everyone felt that the uneven demand placed on the Large Panel Line by the board stuffing plants made managing the line difficult. Every year, the line experienced a slow period in January and early February, during which it was difficult to find enough work to keep the workers busy. By March, however, demand would jump, the line would get overloaded, and the cycle of costly overtime and, with a few minor lulls, capacity vendoring would start again and continue through December. 2. Data As part of the ongoing discussion about the capacity of the Large Panel Line, Manufacturing Engineering put together a rough set of capacity numbers for the processes that represent the basic process flow through the Large Panel Line.4 The numbers, summarized in Table 1, are defined as follows: • Number of Machines: the number of tools, generally identical, in a given process center. • Base Speed: the rate of a single machine in panels per hour without considering any of the detractors. • Efficiency: the fraction of time a machine is up, not counting downtime due to setups or failures (i.e., the overall availability of a machine, therefore, must be computed by further reducing this efficiency according to the time lost to setups and failures). • Lot Size: the average number of panels run between setups. • Setup Time: the average setup time between lots, in hours. • Mean Time to Failure: the average time until a machine fails, in hours. • Mean Time to Repair: the average repair time of a machine, in hours. 4 Some products require additional steps, such as Gold Plating, which might require the boards to be sent outside the plant to vendors. However, virtually all the products on the Large Panel Line passed through this basic sequence. 3 Tool Press (Core) Thopmson Press IP Preclean IP Expose IP D.E.S. IP Optrotech Verify-Repair-Weld Chlorite Presses Machining VNO TruDrills Smear Remove Blast Cu Plate EP Preclean EP Expose EP D.E.S. EP Optrotech EP Anal/Repair Probimer Coat Probimer Expose Dev/Cure/Entek White ID Halving Router View 1220 Water Wash PDI 4000 EPC Analyze No. Mach. 2 2 3 4 3 6 16 1 3 1 31 1 1 2 1 2 1 3 0 1 5 1 2 1 2 2 1 3 3 Base Speed 105 133 95 67 67 40 14 342 68 701 8.1 343 176 90 271 136 223 79 0.044 180 60 180 257 200 149 220 431 143 77.5 Efficiency 99 80 82 81 85 80 100 76 99 95 80 99 84 90 74 81 85 74 100 90 80 83 82 68 80 76 87 75 85 Lot Size 135 72 2,792 72 2,100 72 72 10,103 135 72 131 6,628 3,010 4,067 3,300 72 3,657 1,088 45 3,492 72 3,492 72 2,820 72 2,430 12,938 72 72 Setup Time 0.06 0.03 0.0 0.13 0.0 0.04 0.01 0.0 0.06 0.25 0.6 0.0 0.0 0.0 0.0 0.1 0.0 0.0 0.0 0.0 0.05 0.0 0.35 0.0 0.13 1.0 0.0 0.17 0.1 MTTF 155 57 18 47 22 63 147 22 155 72 232 147 200 16 22 47 35 63 1 12 57 42 28.5 40 35 750 20 120 57 MTTR 1.8 3.0 3.0 3.0 3.0 7.0 3.0 3.0 1.8 3.0 9.7 3.0 2.0 3.0 3.0 3.0 3.0 7.0 0.0 1.3 3.0 1.3 1.5 3.0 3.0 2.0 2.0 2.0 3.0 Table 1: Capacity Data for Large Panel Line. A basic layout of the process centers in the Large Panel Line is shown in Figure 1 3. Your Mission Mr. Pettito is growing increasingly impatient with the slow progress at improving throughput, reducing cycle time, and raising the level of customer service. The 4:00 meetings have revealed a host of problems, but no consensus on solutions. He is looking to you for general guidance concerning where to look for leverage and ideas for reshaping the entire system. Because he is concerned that Corporate will eventually decide to outsource the entire PCB manufacturing process, he is willing to consider virtually any alternative. However, he must be careful to make sure that the Lubbock plant is cost competitive with non-HAL PCB producers. 4 Drills Copper Plate EOL Sizing EOL Test Internal Test & Repair Procoat Circuitize External Test & Repair Lamination Machining Lamination Presses Figure 1: Layout of Large Panel Line. 5 Treater Tower