EEE 531: Semiconductor Device Theory I

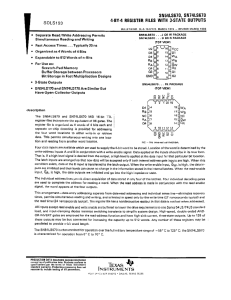

advertisement

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

1. Introduction to MOSFET operation

EEE 531: Semiconductor Device Theory I

1. Introduction

• First operational device was

made in 1947 at Bell Labs.

• Since then, the MOSFET

dimensions have been continuously scaled to achieve

more functions on a chip.

5

Critical Dimension

Dimension [micrometers]

• Firs proposal for a MOSFET

device was given by

Lilienfeld and Heil in 1930.

Cell Edge

1

0.1

0.05

1990

1995

2000

Year

2005

year

From

FromSIA

SIAroadmap

roadmapfor

for

semiconductors

semiconductors(1997)

(1997)

EEE 531: Semiconductor Device Theory I

2010

• MOSFET is a four-terminal device. Basic device configuration is illustrated on the figures below.

Side-view of the device

Basic device parameters:

Top-view of the device

channel length L

channel width W

oxide thickness dox

junction depth rj

substrate doping NA

EEE 531: Semiconductor Device Theory I

• There are basically four types of MOSFETs:

(a) n-cnannel, enhancement mode device

G

ID

S

D

n+

symbol

n+

p-type SC

VT

VG

(b) n-cnannel, depletion mode device

G

S

D

n+

symbol

ID

n+

p-type SC

VT

EEE 531: Semiconductor Device Theory I

VG

(c) p-cnannel, enhancement mode device

ID

G

S

D

p+

VT

symbol

VG

p+

n-type SC

(d) p-cnannel, depletion mode device

ID

G

S

D

p+

symbol

p+

n-type SC

EEE 531: Semiconductor Device Theory I

VT

VG

• The role of the Gate electrode for n-channel MOSFET:

VVGG==00

VVGG >>VVTT

source

source

drain

drain

Positive gate voltage does two things:

(1) Reduces the potential energy barrier seen by the electrons from

the source and the drain regions.

(2) Inverts the surface, and increases the conductivity of the

channel.

EEE 531: Semiconductor Device Theory I

• The role of the Drain electrode for n-channel MOSFET:

dn/dE

VVGG==0,0,VVDD>>00

dn/dE

source

Large potential barrier allows only few

electrons to go from the source to the drain

(subthreshold conduction)

drain

EC

dn/dE

VVGG>>VVTT,,VVDD>>00

dn/dE

source

Smaller potential barrier allows a large

number of electrons to go from the source

to the drain

EEE 531: Semiconductor Device Theory I

drain

EC

• Qualitative description of MOSFET operation:

G

(a)

(a) VVGG>>VVTT,,VVDD>>00(small)

(small)

S

D

n+

Variation of electron density

along the channel is small:

n+

p-type SC

I D VD

G

(b)

(b)VVGG>>VVTT,,VVDD>>00(larger)

(larger)

S

Increase in the drain current

reduces due to the reduced

conductivity of the channel at

the drain end.

EEE 531: Semiconductor Device Theory I

D

n+

n+

p-type SC

G

(c)

(c)VVGG>>VVTT,,VVDD==VVGG--VVTT

S

D

n+

Pinch-off point. Electron

density at the drain-end of the

channel is identically zero.

n+

p-type SC

G

(d)

(d)VVGG>>VVTT,,VVDD>>VVGG--VVTT

S

D

n+

Post pinch-off characteristic.

The excess drain voltage is

dropped across the highly resistive pinch-off region denoted by L.

EEE 531: Semiconductor Device Theory I

+

n

L

p-type SC

• IV-characteristics (long-channel devices):

ID

(c)

(d)

(b)

Linear

region

(a)

Saturation

region

VD

EEE 531: Semiconductor Device Theory I

Conduction band Ec [eV]

N A 8 1017 cm 3 , d ox 3 nm

VG 0.8 V, VD 20 mV, VT 0.33 V

drain

source

Di

sta

nc

e

[

m]

m]

Distance [

EEE 531: Semiconductor Device Theory I

VG 0.8 V, VD 20 mV

Accumulation of carriers

Electron density [m-3]

Surface inversion

drain

source

Dista

nce [

m]

EEE 531: Semiconductor Device Theory I

D

ce

n

a

t

is

]

m

[

VG 0.8 V, VD 0.2 V, VT 0.33 V

Electron density [m-3]

Negating effect of the drain

drain

source

Dista

nce [

m]

EEE 531: Semiconductor Device Theory I

D

ce

n

a

t

is

]

m

[

Conduction band Ec [eV]

VG 0.8 V, VD 0.56 V, VT 0.33 V

source

drain

Distance [m]

EEE 531: Semiconductor Device Theory I

]

m

[

D

e

c

an

t

is

Electron density [m-3]

VG 0.8 V, VD 0.56 V, VT 0.33 V

drain

source

Distance

[m]

EEE 531: Semiconductor Device Theory I

ce

n

a

t

Dis

]

m

[

VG 0.8 V, VD 0.9 V, VT 0.33 V

Electron density [m-3]

Pinched-off

channel

drain

source

Distanc

e [m]

EEE 531: Semiconductor Device Theory I

ce

n

a

st

i

D

]

m

[

VG 0.8 V, VD 1.56 V, VT 0.33 V

Contour plot

0.1

0.08

0.06

source

an

ce

[

m

]

0.04

Distance [m]

Di

st

Conduction band Ec [eV]

3D View

0.02

drain

0

0

0.05

0.1

Distance [m]

EEE 531: Semiconductor Device Theory I

0.15

VG 0.8 V, VD 1.56 V, VT 0.33 V

Electron density [m-3]

Pinched-off channel

drain

source

Distance

[m]

EEE 531: Semiconductor Device Theory I

]

m

[

e

c

n

a

t

Dis

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

2. Gradual channel approximation for current calculation

(A) square-law theory

(B) bulk-charge theory

(C) transconductance, output conductance

and series resistance

(D) limitations of the two models

EEE 531: Semiconductor Device Theory I

2. Gradual channel approximation

• This model is due to Shockley.

• Assumption: The electric field variation in the direction

parallel to the SC/oxide interface is much smaller than the

electric field variation in the direction perpendicular to the

interface:

z

G

W

x

S

D

y

oxide

n+

L

n+

p-type SC

EEE 531: Semiconductor Device Theory I

dFy

dFx

dx

dy

• Recall the expressions for the threshold voltage for real

MOS capacitor:

Gate voltage :

1

2qN Ak s 0 2 F VFB

Cox

Qit Q f

Qot

Qm

1

MS

ot

m

q

Cox Cox

Cox

Cox

VT 2 F

Flat band voltage : VFB

• Beyond the point that determines the onset of strong inversion (s=2F), any excess charge on the gate balanced with

excess charge in the semiconductor, is given by:

QG QB Q N Ctot VG VT Q N Cox VG VT Q B

QB QB s QB 2 F

• Based on how we consider QB, we have:

(A) Square-law theory: QB = 0

(B) Bulk-charge theory: QB0

EEE 531: Semiconductor Device Theory I

(A) Square-law theory

• The charge on the gate is completely balanced by QN(x), i.e:

QN ( x ) Ctot VG VT V ( x )

VS= 0

EFS

x=0

V(x)

x

VD

EC

EFD= EFS - VD

• Total current density in the channel:

dn

dV

J n qn n F ( x) qDn

qn n

dx

dx

negligible

Note: Total current density approximately equal to the

electron current density (unipolar device).

EEE 531: Semiconductor Device Theory I

• Integrating the current density, we obtain drain current ID:

W

yc ( x )

dV

W

dx

yc ( x )

dV

I D dz dy qn( x, y ) n ( x, y )

dx

0

0

qn( x, y ) n ( x, y )dy

0

Q N ( x ) eff

dV

QN ( x ) eff W

dx

High-resolution transmission electron

micrograph of the interface

between Si and SiO2

(Goodnick et al., Phys. Rev. B 32, p. 8171, 1985)

2.71 Å

dV

CoxW eff VG VT V ( x )

dx

Effective

Effectiveelectron

electronmobility,

mobility,

in

inwhich

whichinterface-roughness

interface-roughness

isistaken

takeninto

intoaccount.

account.

EEE 531: Semiconductor Device Theory I

3.84 Å

• The role of interface-roughness on the low-field electron

mobility:

Phonon

Coulomb

N A 7 10 cm

500

3

2

1000

17

Mobility [cm /V-s]

2

Mobility [cm /V-s]

1500

(aN + bN

s

400

-1

)

depl

N

300

200

-1/3

s

experimental data

uniform

step-like (low-high)

retrograde (Gaussian)

100

0

10

15

10

16

10

17

10

18

-3

Doping [cm ]

12

10

13

10

-2

Inversion charge density N [cm ]

s

Interface-roughness

Bulk

Bulksamples

samples

EEE 531: Semiconductor Device Theory I

Si

Siinversion

inversionlayers

layers

• The experimentally observed universal mobility behavior is

due to the dominant surface-roughness influence on the lowfield electron mobility under strong inversion conditions.

• Various models proposed for the variation of the effective

transverse electric field upon the inversion (Ns) and depletion (Ndepl) charge density:

Stern and Howard:

F eff

Matsumoto and Uemura:

Krutsick and White:

(a=0.5 and b<1)

F eff

3211 N s N depl

F eff 0.5N s N depl

<z>

0.5N s 1 Ndepl

W

EEE 531: Semiconductor Device Theory I

• There are several empirical expressions for the effective

field dependence of the low-field electron mobility:

Effective-field dependence:

n ,eff

1105

1 Feff / 30.5

0.657

, p ,eff

342

1 Feff / 15.4 0.617

Gate-voltage dependence:

n ,eff

0

, 0.02 0.08 1 / V

1 (VGS VT )

• Universal mobility

behavior:

eff

N A3 N A2 N A1

N A1

N A2

N A3

Feff

EEE 531: Semiconductor Device Theory I

• We now use the conservation of current argument, to get:

VD

L

I D dx W eff Cox VG VT V ( x)dV

0

0

ID

W eff Cox

L

VG VT VD 12 VD2 , for VD VG VT

• This last result represents the expression for the current,

valid up to the pinch-off point.

• The current expression beyond the pinch-off point, at which

VD VG VT QN ( L) 0

is obtained by construction, to give:

ID

W eff Cox

2L

VG VT 2 , for VD VG VT

EEE 531: Semiconductor Device Theory I

(B) Bulk-charge theory

• Square-law theory assumes that excess QG is solely balanced

by QN, and that W=WT=const. along the channel.

• The violation of this assumption is clearly shown on the

figure below:

Depth [m]

N A 8 1017 cm 3 , d ox 3 nm

VG 0.8 V, VD 1.56 V, VT 0.33 V

source

drain

Length [m]

EEE 531: Semiconductor Device Theory I

• Taking into account the contribution by the bulk charges, the

more exact electron density is given by:

Q N ( x ) Cox VG VT V ( x ) QB ( x )

where:

QB ( x ) qN A W ( x ) WT

2k s 0

2k s 0

2 F V ( x ), WT

2 F

W ( x)

qN A

qN A

• Following the same steps as in the square-law theory, we

get:

W eff Cox

VD

2

1

4

ID

VG VT VD 2 VD 3 VW F 1

L

2 F

2k s 0 qN A 2 F WT qN A

VW

Cox

Cox

EEE 531: Semiconductor Device Theory I

3/ 2

3VD

1

4 F

• The pinch-off voltage VDsat, is obtained from the condition

that QN(L)=0, which gives:

VDsat

V V

VW

G

T

VG VT VW

1

4 F

2 F

2

VW

1

4 F

• Comparison between the two theories:

ID

Square-law

NA

increasing

Bulk charge

VD

EEE 531: Semiconductor Device Theory I

(C) Transconductance, drain conductance, series resistance

• Using square-law theory and for small VD, we get:

ID

W eff Cox

L

VG VT VD

I D

gm

VG V

transconducance:

W eff Cox

L

D const .

I D

drain conductance: g d

VD V

W eff Cox

G const .

• For large values for VD, we get:

gm

W eff Cox

L

VG VT ,

EEE 531: Semiconductor Device Theory I

gd 0

L

VD

VG VT

• The simplified low-frequency and high-frequency MOSFET

small-signal equivalent circuits are shown below:

id

G

vgs

gmvgs

rd

D

G

vds

vgs Cgs

id

Cgd

D

gmvgs

rd

vds

S

S

Low-frequency

High-frequency

• The cut-off frequency (frequency for which the short-circuit

current gain equals one) is given by:

gm

1

L

fT

, ttr

2 C gs C gd

2ttr

veff

Transit time of the electrons in the channel

EEE 531: Semiconductor Device Theory I

• Assumption made in the previous derivations is that the

entire voltage drop is across the channel.

• In real devices, both the drain and the source resistances Rd

and Rs may play an important role, thus limiting the device

performance.

VDS

VGS VG Rs I D

VDS VD Rs Rd I D

VGS

oxide

n+

RD

RS

n+

p-type SC

EEE 531: Semiconductor Device Theory I

• These series resistances modify the transconductance and the

output conductance:

I D

gm

VG V

D const .

I

gd D

VD V

G const .

gm0

1 g m 0 Rs g d 0 ( Rs Rd )

gd 0

1 g m 0 Rs g d 0 ( Rs Rd )

Transfer characteristic

ID

Output characteristic

ID

Rs=Rd=0

Rs 0

Rd 0

Rs=Rd=0

VG3

VG2

VG1

VG

EEE 531: Semiconductor Device Theory I

VD

(D) Limitations of the square-law and bulk-charge theories:

(1) They do not include the subthreshold region.

(2) Both theories do not self-saturate. One must obtain the

post-pinch off characteristics by construction.

(3) The exact charge model self-saturates and naturally

includes the subthreshold.

EEE 531: Semiconductor Device Theory I

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

3. MOSFET subthreshold characteristics

EEE 531: Semiconductor Device Theory I

3. Subthreshold characteristics

• Above threshold current is governed by the channel

resistance. Drift current dominates.

• Below threshold current is barrier limited. Diffusion

current dominates.

• Recall PN junctions: Current depends exponentially on the

applied bias the excess minority carrier density at the

edge of the SCR depends exponentially on the applied

voltage.

• MOSFETs appear to have the same problem electrons

injected into the channel from the source also become

minority carriers and need to climb a potential barrier. The

important point in MOSFET operation is that the gate

electrode eliminates this barrier. Only in subthreshold the

barrier will play significant role in limiting the current flow

in the device.

EEE 531: Semiconductor Device Theory I

G

S

D

x

n+

n+

p-type SC

y

Accumulation condition

EF

Depletion condition:

• small inversion charge

• small drain current

• slight potential gradient

from source to drain

EF

Inversion condition

EF

EEE 531: Semiconductor Device Theory I

• Subthreshold current flows when the device is in weak

inversion:

F s 2 F

• In long-channel devices, the voltage drop VD is entirely

across the drain-substrate junction, which makes the in-plane

component of the field (Fx) small, and current is diffusion

limited:

dn

I D qAeff Dn

dx

Effective cross-section for the

subthreshold current

• If the electron diffusion length is much larger than L, the

electron density varies linearly when going from the source

(nss) to the drain (nsd):

x

n ( x ) n ss nss n sd

L

EEE 531: Semiconductor Device Theory I

nss= n(0) source end

nsd= n(L) drain end of the

channel

• Electron densities at the source and drain end of the channel:

q F

q s

EF

qVG

qVG VD

Ws

q F

q s

y-axis

qVD

EFp

EFn

WD

y-axis

Source end of the channel:

Drain end of the channel:

E F Ei ( y )

n ss ( y ) ni exp

k

T

B

( y )

n po exp

V

T

E Fn Ei ( y )

n sd ( y ) ni exp

k

T

B

( y ) V D

n po exp

V

T

EEE 531: Semiconductor Device Theory I

• We now interpolate the potential variation along the depth

with:

1

( y ) s F ( y 0) y s Fs y , Fs

2 qN Ak s 0 s

k s 0

Surface

potential

Surface electric

field

• Consider now the electron density at the source end of the

channel:

s Fs y

s

Fs y

n po exp n po exp

nss ( y ) n po exp

V

V

V

T

T

T

This term suggests that the effective thickness of the inversion

layer along the depth (y-direction) is:

yeff

EEE 531: Semiconductor Device Theory I

VT k s 0VT

Fs

qN A

qN A

2k s 0 s

• Substituting these results into the diffusion current expression gives:

ID

W 2 ni

n k s 0 VT

L NA

2

VT

s

1

s

e

2LDp

VT

1 e

VD VT

Important notes:

- The subthreshold current is nearly independent of VD if

VD > 3VT

- The subthreshold current depends exponentially on s

- The subthreshold current depends upon the ratio W/L

• For VD > 3VT, the subthreshold current simplifies to:

ID

VT s

b

e

s

VT

1 VT s

ln( I D ) ln(b) ln

2 s VT

1

d ln( I D )

VT

EEE 531: Semiconductor Device Theory I

VT

1 2 d s

s

• To obtain the expression for the subthreshold swing S, we

now utilize the relationship between the surface potential

and the gate voltage:

Qs ( s )

1

VG s

VFB s

2 qN Ak s 0 s VFB

Cox

Cox

dVG

C s ( s )

1

d s

Cox

• Combining the results for dln(ID) and dVG, gives:

2 1

C s ( s )

dVG

2 Cs

1 2

VT ln 10 1

S

d log( I D )

Cox a Cox

where a 2k s 0 / LDp Cox . If a >> Cs/Cox then:

C s ( s )

dVG

S

VT ln 101

S min 60 mV / decade

d log( I D )

Cox

EEE 531: Semiconductor Device Theory I

• The subthreshold swing tells us how fast we can turn the

device off. Devices with good turn-off characteristics have

subthreshold swings between 70 and 80 mV/decade.

Drain Current (A)

10 -4

10 -6

10

-8

• V

T

•

•

10 -10

Ioff

10 -12 •

0

Short-channel

device

Long-channel

device

0.2

0.4

0.6

0.8

Gate Voltage (V)

EEE 531: Semiconductor Device Theory I

1

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

4. Threshold voltage adjustment

EEE 531: Semiconductor Device Theory I

4. Threshold voltage adjustment

• The threshold voltage is an important device parameter

whose values should not fall outside certain prescribed

limits.

• The conflicting design requirements between reducing VD,

VT, Ileak, C, and increasing performance are schematically

shown in the figure below:

Reduce

Pswitch ~ VDD2

VT

Reduce

Pleak ~ VT

Increase

Performance

VDD

EEE 531: Semiconductor Device Theory I

Design space

is shrinking!

• We now recall the expressions for the threshold voltage to

understand which parameters are easily and reproducibly

changed to give the desired threshold voltage:

VT 2 F

VFB

Qs (2 F )

1

VFB 2 F

2qN Ak s 0 2 F VFB

Cox

Cox

Q f Qit (2 F )

1

Qm

MS

q

Cox

Cox

Cox

The variation of NA

makes significant

contribution here.

MS M sc EC E F bulk

M sc 0.5 E g k BT ln( N A / ni )

For each factor of 10 in doping concentration change,

this term changes by 2.3 kBT (not very much).

EEE 531: Semiconductor Device Theory I

• To summarize, threshold voltage controlling parameters are:

(A) Substrate doping

(B) Substrate bias via s

(C) Oxide thickness (useful for major threshold voltage

control, but not for threshold voltage adjustments).

(A) Substrate doping

• The key process parameter for threshold voltage control is

the substrate doping.

• For general, non-uniform doping density, the relationship

between VG and s is:

Depletion region depth

Qs ( s )

q W

VG s

VFB s

N B ( y ) dy VFB

Cox

Cox 0

EEE 531: Semiconductor Device Theory I

Acceptor-type

doping density

• The substrate doping concentration can be modified, for

example, using ion implantation process.

• Two limiting cases are interesting to consider:

- very shallow heavily-doped surface layer

- general ion-implanted impurity profile

• For very shallow surface layer, we have:

N B ( y ) N A Di (0)

Dose: # of atoms per unit area

q W

VG s

N A Di (0)dy VFB

Cox 0

qN AW qDi

Acceptors positive shift

s

VFB

Cox

Cox

Donors negative shift

EEE 531: Semiconductor Device Theory I

• For ion-implanted impurity profiles:

2

y

R

Di

p

Ni ( y)

exp

2

2R p

2R p

Ni ( y)

Di ion dose

Rp range

Rp straggle

Ni ( y)

Ni

R p

Di ( N i N A )d i

NA

NA

di

Rp

y (depth)

Real

Realion-implanted

ion-implantedprofile

profile

EEE 531: Semiconductor Device Theory I

y (depth)

Approximation

Approximationto

tothe

the

real

realprofile

profile

• Two special cases need to be considered for the step doping

profile:

di < W all implanted ions are in the SCR

qDi

1

VT VFB 2 F

2qN Ak s 0 2 F qDi di / 2k s 0

Cox Cox

small effect

di > W the depth over which we have implanted ions

exceeds the SCR depth

1

VT VFB 2 F

2qN i k s 0 2 F

Cox

Need to substitute for

different doping

EEE 531: Semiconductor Device Theory I

(B) Substrate bias

• Reverse, or back-biasing, is another method that has been

employed to adjust the threshold voltage.

q F

qs

EF

q F

qVBS

s

EFp

EFn

W

y-axis

s 2F onset of strong

inversion

W

s 2F VBS onset of strong

Energy-band diagram

for VBS = 0

EEE 531: Semiconductor Device Theory I

inversion

Energy-band diagram

for VBS 0

• From the energy-band diagrams shown in the previous slide,

it is clear that the surface will invert when s 2F VBS

• The threshold voltage is then given by:

1

VT VFB 2 F VBS

2qN i k s 0 2 F VBS

Cox

Important notes:

Back-biasing always

increases VT

Current-voltage relations

remain the same provided:

2F 2F VBS

VT

N A2 N A1

N A1

VBS

• It is generally desirable to have low substrate-bias sensitivity

(shallow channel implant +appropriate ion dose)

EEE 531: Semiconductor Device Theory I

(C) Threshold voltage extraction

• Criterion 1:

VT =VG for which ID=10 A (Not accurate, but easy to use)

• Criterion 2:

ID

The intercept on the ID = 0 axis

gives the threshold voltage.

VG

VT

EEE 531: Semiconductor Device Theory I

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

5. Small-geometry effects

- Subthreshold slope increase

- Short-channel effects

- Narrow-width effects

- Hot-carrier effects

- Discrete impurity effects

- Schematic description of realistic device structure

EEE 531: Semiconductor Device Theory I

5. Short-Channel Effects in Scaled Si-MOSFETs

VG

• Increase in the subthreshold current:

tox

ND+

VD

• Threshold voltage modification:

ND+

- short-channel effects

- narrow-width effects

- quantum-mechanical charge

description

L

NA

Long-channel device

VG/

N+D

- drain-induced barrier lowering

• Transconductance degradation:

tox/

VD/

N+D

- finite inversion layer capacitance

- depletion of the polysilicon gates

• Parasitic BJT action:

L/

- punch-through effect

- substrate current increase due to carrier

multiplication and regenerative feedback

NA

Scaled device

• Hot-carrier effects:

Minimum

Minimumchannel-length

channel-lengthbelow

belowwhich

which

significant

significantshort-channel

short-channeleffects

effectsare

are

expected

to

occur:

expected to occur:

L min A rj Tox (Ws WD )

2 13

-

oxide charging

velocity saturation

velocity overshoot

ballistic transport

• Classical statistical effects:

- random dopant fluctuations

EEE 531: Semiconductor Device Theory I

(A) Subthreshold Current and Threshold Voltage

ID [A]

• For a long-channel device, the

subthreshold current is

independent of VD, once VD>3VT

Device that shows

long-channel

behavior

NB=1015 cm-3

• The situation is rather different

for small devices, where one

observes:

ID [A]

increase in the subthreshold

Device with

severe shortchannel behavior

NB=1014 cm-3

swing

drain voltage dependence of

the subthreshold current due

to Drain Induced Barrier

Lowering (DIBL)

VG [V]

EEE 531: Semiconductor Device Theory I

(B) Short-channel effects

• In all our previous analysis, it was assumed that the gate

charge QG equals the sum of the electron charge QN and

depletion charge QB.

• Even in long-channel device, this is not strictly true. Part of

the channel charge is controlled by the source and drain, not

by the gate.

+VG

G

Only the charge in the shaded

area is controlled by the gate

S

D

n+

n+

p-type SC

EEE 531: Semiconductor Device Theory I

• With increasing VD, the amount of charge controlled by the

drain increases lower gate voltage is needed to invert the

channel, i.e. VT decreases.

• This, in turn, leads to increase in the drain current.

ID

Short-channel device

Long-channel device

VD

EEE 531: Semiconductor Device Theory I

• Graphical description of the problem:

L

rj

y

n+

W

L’

rj y

r j W 2 W 2 r j

1 2W / r j

L' L 2 y L 2 r j 1 2W / r j 1

• Total charge controlled by the gate (gate-width Z) is:

- long-channel device: QB ZL qN A ZL

- short-channel device:

QB' ZL

1

L L'

'

qN A Z ( L L' ) QB qN A

2

2L

EEE 531: Semiconductor Device Theory I

• Recall the expression for the threshold voltage:

QB

VT 2 F

VFB

Cox

• The threshold voltage shift is then given by:

'

rj

QB QB

qN AW r j

2W

2W

VT

1

1 VW 1

1

Cox

Cox L

rj

L

rj

Threshold Voltage (V)

Voltage (V)

5

4

V DD

3

2

VT

1

0

0.7

0.6

0.5

VT

(SCE)

Low Drain Voltage

0.4

0.3

VT

High Drain Voltage

(DIBL)

0.2

0.1

SCE: Short Channel Effect

DIBL: Drain-induced Barrier Lowering

0

0.1

1

Channel Length ( m)

EEE 531: Semiconductor Device Theory I

0.1

1

Channel Length ( m)

10

(C) Narrow-width effects

• The channel width also affects the threshold voltage, due to

the additional lateral component in the CSR width (the gate

controlled region extends on the sides, which gives:

L QB Z 12 qN A WT2

LZQ B' L QB Z 2 qN A 14 WT2

• The difference in charge is:

2

qN

W

QB' QB A T

2Z

• This gives the following threshold

voltage shift:

WT

QB' QB qN AWT2

VT

VW

Cox

2 ZCox

2Z

EEE 531: Semiconductor Device Theory I

Field

oxide

Gate oxide

WT

Extra depletion charge

Increase in

threshold voltage

• Graphical representation of the VT shift:

Variation of VT

with channel width Z

• The combined effect of both short-channel and narrow-width

effect gives:

W

W

W r j

VT VW 1 2 1 1

rj

Z L

Z

For more detailed expression and actual doping profiles,

numerical analysis is needed.

EEE 531: Semiconductor Device Theory I

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

5. Small-geometry effects

- Subthreshold slope increase

- Short-channel effects

- Narrow-width effects

- Hot-carrier effects

- Discrete impurity effects

- Schematic description of realistic device structure

EEE 531: Semiconductor Device Theory I

(D) Hot-carrier effects

• Under high bias conditions, the electrons at the drain end of

the channel become very energetic (hot). This can give rise

to several undesirable effects, such as:

Velocity saturation

Punch-through effect

Snapback breakdown (parasitic BJT action)

Oxide charging and tunneling currents

Velocity overshoot effect

• The ballistic transport effects, such as velocity overshoot lead

to smaller transit time of the carriers and are, therefore,

desirable effects.

EEE 531: Semiconductor Device Theory I

Velocity saturation

• Long-channel devices ID-VD curves nearly constant in

saturation

• Short-channel device Electric fields become very high and

the drift-velocity becomes constant (mobility decreases).

10

Drift velocity [cm/s]

7

T = 300 K

1

10

6

0.1

5

10

-1

10

10

0

10

1

10

2

0.01

10

3

Electric field [kV/cm]

EEE 531: Semiconductor Device Theory I

Average energy [eV]

10

Drift

Driftvelocity

velocityand

and

average

averageelectron

electron

energies

energiesfor

forbulk

bulkSi

Si

• A simplified expression is obtained using:

I D qAeff nvd , Aeff Zyeff

Device width

Effective thickness of the

inversion layer

i.e. the velocity-limited drain current equals to:

I D qZyeff nvd qyeff n Zvd Zvd Cox (VG VT )

QN

• Comparing the above expression with the mobility-limited

one for a long-channel device, we get:

vsat

eff VG VT

2L

EEE 531: Semiconductor Device Theory I

For VG -VT=5 V we

get L =1.25 m

(vsat = 107 cm/s)

Channel length = 0.2 m

Experimental

device

Calculated

IV-characteristics with

velocity saturation

EEE 531: Semiconductor Device Theory I

Calculated

IV-characteristics

without velocity

saturation effect

Punch-through effect

• Occurs when the source and drain depletion regions touch.

• The majority electrons in the source get injected into the

depletion region where they are swept by the high electric

field.

• Drain current is dominated by the space-charge current

(~VD2) and not by the inversion layer current.

• To eliminate this effect,

a punch-through stop is used.

This is done with deep ionimplantation process.

n+

Depletion region

boundaries

EEE 531: Semiconductor Device Theory I

n+

Device

Devicewith

withsevere

severeshortshortchannel

channeleffects

effects(Device

(Device2)

2)

ID [A]

ID [A]

Marginal

Marginallong-channel

long-channel

device

device(Device

(Device1)

1)

VD [V]

EEE 531: Semiconductor Device Theory I

VD [V]

Snapback breakdown

• Electrons near the drain region

impact ionize, i.e. generate

electron-hole pairs.

• Electrons are swept by the drain,

and holes go to the substrate,

forward-biasing the sourcesubstrate junction. This leads to

higher electron injection into the

substrate.

• More electrons in the substrate

means more impact ionization, i.e.

positive feedback effect.

• The snapback portion comes

because the source-substrate-drain

form a BJT in parallel to the

MOSFET that exhibits negative

resistance or snapback.

ID

EEE 531: Semiconductor Device Theory I

Short-channel

device

Long-channel device

VD

Oxide charging and tunneling currents

• Oxide charging, or charge injection and trapping, is another

undesirable effect.

• Electrons at the drain end of the channel have sufficient

energy to overcome the barrier at the Si/SiO2 interface and

be trapped in the oxide.

Since

Sincethe

theeffect

effectisiscumulative,

cumulative,

ititlimits

limitsthe

theuseful

useful‘life’

‘life’of

ofthe

the

device.

device. LDD

LDD regions

regions are

are used

used

to

toreduce

reduceoxide

oxidecharging.

charging.

EEE 531: Semiconductor Device Theory I

• Tunneling currents lead to gate leakage. The three types of

tunneling processes are schematically shown below:

B

Vox = B

Vox < B

Vox > B

tox

FN

•

•

•

•

FN/Direct

Direct

For tox 40 Å, Fowler-Nordheim (FN) tunneling dominates

For tox < 40 Å, direct tunneling becomes important

Idir > IFN at a given Vox when direct tunneling active

For given electric field: - IFN independent of oxide thickness

- Idir dependent on oxide thickness

EEE 531: Semiconductor Device Theory I

Current (A/ m)

• As oxide thickness decreases, gate current becomes more

important. It eventually dominates the off-state leakage

current (ID at VG = 0).

10-4

I on

10-6

10-8

I off

10-10

10-12

IG

10-14

10-16

0

50

100

150

200

Technology Generation (nm)

EEE 531: Semiconductor Device Theory I

250

Velocity overshoot effect

• We can describe the motion of the electrons between

collisions by simple Newton’s Law:

dvdx

m*

qFx

dt

• In a simplified approach (momentum balance equation for

an average carrier) that neglects diffusion, we have

dvdx

m * vdx

m*

qFx

dt

m

• For a uniform electric field applied at t=0, the solution of

the above equation is of the form:

q m

t

vdx (t )

Fx e

m*

m

EEE 531: Semiconductor Device Theory I

1

• When steady-state has been reached, the electrons have

traveled the distance:

m

d vdx (t )dt

0

2

q m

Fx

em *

• For Fx=10 kV/cm, we have that:

-> d 200Å for electrons in Si

• Why do we observe velocity overshoot?

(1) The energy relaxation time is larger than momentum

relaxation time

(2) At first, the electric field simply displaces the distribution function with little change on its shape.

(3) Later on, collisions broaden the distribution, the

electron temperature increases and drift velocity drops.

• Velocity overshoot effect reduces the electron transit time,

i.e. leads to faster devices.

EEE 531: Semiconductor Device Theory I

EEE 531: Semiconductor Device Theory I

Instructor: Dragica Vasileska

Department of Electrical Engineering

Arizona State University

Topics covered:

5. Small-geometry effects

- Subthreshold slope increase

- Short-channel effects

- Narrow-width effects

- Hot-carrier effects

- Discrete impurity effects

- Schematic description of realistic device structure

EEE 531: Semiconductor Device Theory I

(E) Discrete impurity effects

• In ultra-small devices, discrete impurity effects become important.

This is clearly seen in the experimental measurements shown

below.

Experimental investigations:

T. Mizuno, J. Okamura, A. Toriumi, IEEE Trans.

Electron Dev. 41, 2216 (1994).

J.T. Horstmann, U. Hilleringmann and K.F. Goser,

IEEE Trans. Electron Dev. 45, 299 (1998).

EEE 531: Semiconductor Device Theory I

• The atomistic nature of the impurity atoms leads to fluctuations in

the potential.

• The potential fluctuations affect the magnitude of the current and

the threshold voltage for devices fabricated on a same chip.

substrate

Simulated

Simulateddevices

deviceshave:

have:

LL==0.1

0.1m,

m,ZZ==50

50nm

nm

The

Theapplied

appliedvoltages

voltagesare:

are:

VVG ==00V,

V

=

10

mV

V, VD = 10 mV

G

D

[

drain

]

length [m]

h

pt

e

d

]

[m

drain

m

len

gth

source

Energy [eV]

Energy [eV]

Conduction band edge along

depth and parallel to the SC/oxide interface

source

width [m]

EEE 531: Semiconductor Device Theory I

• Influence on the subthreshold transfer characteristics:

Current flow

150

140

Width [nm]

drain

source

Width [m]

Conduction band edge

130

120

110

100

60

80

100

140

Length [nm]

Length [m]

10

D

[A]

10

I

The

Thespread

spreadof

ofthe

thetransfer

transfer

characteristics

characteristicsalong

alongthe

thegate

gate

axis

axisisisdue

duetotothe

thenon

nonuniforuniformity

of

the

potential

barrier

mity of the potential barrier

that

thatallows

allowsfor

forearly

earlyturn-on

turn-on

atatsome

someparts

partsof

ofthe

thechannel.

channel.

120

-7

T=300 K

V =10 mV

D

-8

17

N =8x10 cm

-3

A

10

10

-9

t =3 nm

ox

-10

I (discrete model)

D

10

-11

I

DAV

(discrete model)

I (continuum model)

10

D

-12

0.0

EEE 531: Semiconductor Device Theory I

0.1

0.2

0.3

V

G

[V]

0.4

0.5

0.6

• Threshold voltage fluctuations are clearly seen on the example

shown below, where we plot the # of channel dopant atoms (~ID)

as a function of VG for two devices taken at the ends of the

distribution of the statistical ensemble of 30 devices considered in

this study. All devices considered here have identical geometry.

6

4

3

statistical ensemble

of 30 devices with

identical geometry

(a)

Nav =312

(N)=70

2

1

0

# of channel electrons

Frequency

5

160

18

140

LG =WG =50 nm, NA =5x10

120

VD =0.1 V

-3

(b)

cm

100

80

N=284, VT =0.739 [V]

60

40

N=328, VT =0.86 [V]

20

0

280 290 300 310 320 330 340 350

Number of channel dopant atoms

EEE 531: Semiconductor Device Theory I

0.4

0.6

0.8

1.0

1.2

Gate voltage V

G

1.4

[V]

1.6

• Scatter plots of the threshold voltage versus the number of dopant

atoms clearly show that devices with larger channel width have

smaller threshold voltage fluctuations. We use LG=50 nm, NA=

5x1018 cm-3, Tox=2 nm in this study.

0.84

G

0.82

0.8

0.78

0.76

<V >=0.798 V

T

0.74

(V )= 29 mV

T

0.72

190

200

210

220

230

240

Number of channel dopant atoms

250

0.86

(b)

W =50 nm

0.84

G

0.82

0.8

0.78

<V >=0.799 V

T

0.76

(V )= 25 mV

T

0.74

380

Threshold voltage [V]

0.86

(a)

W =35 nm

Threshold voltage [V]

Threshold voltage [V]

0.86

(c)

W =100 nm

0.84

G

0.82

0.8

0.78

<V >=0.806 V

T

0.76

(V )= 20 mV

T

0.74

400

420

440

460

480

Number of channel dopant atoms

500

580

600

620

640

Vth

4 q 3 Si F k BT / q

Tox 4 N A

L W

3

4

q

N

Si F A

ox

eff eff

EEE 531: Semiconductor Device Theory I

680

Number of channel dopant atoms

• Analytical expression for the threshold voltage standard

deviation:

4

660

• Variation of the threshold voltage standard deviation with

substrate doping, oxide thickness and device width is shown

below.

4 q 3 T

Si B ox

Vth

2

ox

Approach 1 [1]:

4N

A

k T N

; B B ln A

Leff Weff

q

ni

4 4 q 3

Si B

Vth

Approach 2 [2]:

3

Tox 4 N A

k BT / q

4

q

N

ox

Si

B

A

Leff Weff

[1] T. Mizuno, J. Okamura, and A. Toriumi, IEEE Trans. Electron Dev. 41, 2216 (1994).

[2] P. A. Stolk, F. P. Widdershoven, and D. B. Klaassen, IEEE Trans. Electron Dev. 45, 1960

(1998).

40

60

100

=> approach 1

Vth

=> approach 2

Vth

=> our simulation results

15

5

=> approach 1

Vth

=> approach 2

Vth

=> our simulation results

0

18

1x10

3x10

10

Vth

Vth

20

Vth

60

40

Vth

40

30

[mV]

25

=> approach 1

Vth

=> approach 2

Vth

=> our simulation results

50

[mV]

80

30

Vth

[mV]

35

20

20

Vth

18

18

5x10

Doping density N

18

7x10

-3

A

[cm ]

0

0

1

2

3

4

Oxide thickness T

ox

[nm]

EEE 531: Semiconductor Device Theory I

5

10

20

40

60

80

100

120

Device width [nm]

140

(a)

L =50 nm, W =35 nm

G

G

1.3

N =5x10

18

A

-3

cm , T =3 nm

ox

1.2

high-end

1.1

low-end

center

1

0.9

160

180

200

220

240

260

280

300

Number of channel dopant atoms

1

200

180

160

140

120

100

80

60

40

20

0

(b)

5 samples of average

5 samples at

minimum

L =50 nm, W =35 nm, T =3 nm

G

G

0.8

ox

N =5x10

18

A

-3

cm

0.6

Moving slab

0.4

T

5 samples at

maximum

V correlation

Number of Devices

• Significant correlation was observed

between the threshold voltage and

the number of atoms that fall within

the first 15 nm depth of the channel.

1.4

Threshold voltage [V]

• To understand the role that the

position of the impurity atoms plays

on the threshold voltage fluctuations,

statistical ensembles of 5 devices

from the low-end, center and the

high-end of the distribution were

considered.

ND range

ND

0.2

depth

270

260

250

240

230

220

210

200

190

180

170

160

Number of Atoms in Channel

0

0

5

10

15

Depth [nm]

EEE 531: Semiconductor Device Theory I

20

25

20

• Significant correlation was observed

between the drift velocity (saturation

current) and the number of atoms that

fall within the first 10 nm depth of the

channel.

(b)

Drain current [A]

• Impurity distribution in the channel

also affects the carrier mobility and

saturation current of the device.

15

center

10

low-end

5

VG=1.5 V, VD= 1V

0

160

1.5 10

7

200

220

240

260

1

low-end

(c)

7

0.8

Correlation

1 10

center

5 10

6

280

Number of channel dopant atoms

(a)

Drift velocity [cm/s]

180

high-end

V =1.5 V, V =1 V

G

D

high-end

L =50 nm, W =35 nm

G

G

18

-3

average velocity

correlation

drain current

correlation

0.6

L =50 nm

G

0.4

W =35 nm

G

NA=5x10 cm

0

160

T =3 nm

0.2

180

200

220

240

260

ox

N =5x1018 cm-3

280

A

Number of channel dopant atoms

0

0

5

10

15

Depth [nm]

EEE 531: Semiconductor Device Theory I

20

25

(F) Schematic description of realistic device structures

Below shown is a schematics of realistic device structures

and highlight of some critical issues in device fabrication.

• Low resistivity

Interconnect metal (Al, Cu)

{

RC Delay

• Low K dielectric

• Ti, Co silicide?

Interlevel dielectric (Low K)

S

D

• Gate depletion

• Oxide integrity

W

G

Shallow Trench

Isolation (STI)

• Oxide thickness

LDD

Halo/pocket

Anti punchthrough

EEE 531: Semiconductor Device Theory I

• Short channel

effects (e.g., DIBL)

• Epi wafers?

• Cross-sectional micrograps of a 60-nm MOSFET built at

Bell Labs with 1.2 nm gate oxide.

In production 2010:

• 64-Gb DRAM

• 200-GHz transistor speeds

• 10-GHz processor clocks

EEE 531: Semiconductor Device Theory I