A New Bipolar Type Transistor Created Based on

advertisement

CHIN. PHYS. LETT. Vol. 29, No. 10 (2012) 107402

Express Letter

A New Bipolar Type Transistor Created Based on Interface Effects of Integrated

All Perovskite Oxides *

XIA Feng-Jin(夏丰金)1,2† , WU Hao(吴昊)3† , FU Yue-Ju(付跃举)1,4 , XU Bo(许波)1 , YUAN Jie(袁洁)5 ,

ZHU Bei-Yi(朱北沂)1 , QIU Xiang-Gang(邱祥冈)1 , CAO Li-Xin(曹立新)1 , LI Jun-Jie(李俊杰)1 ,

JIN Ai-Zi(金爱子)1 , WANG Yu-Mei(王玉梅)1 , LI Fang-Hua(李方华)1 , LIU Bao-Ting(刘保亭)4 ,

XIE Zhong(谢中)2 , ZHAO Bai-Ru(赵柏儒)1**

1

National Laboratory for Superconductivity, Institute of Physics and Center for Condensed Matter Physics, Chinese

Academy of Sciences, Beijing 100190

2

School of Physics and Microelectronic Science, Hunan University, Changsha 410082

3

School of Physics and Technology, Wuhan University, Wuhan 430072

4

College of Physics Science and Technology, Hebei University, Baoding 071002

5

Department of Materials Science, Wuhan University of Science and Technology, Wuhan 430081

(Received 18 September 2012 accepted by XIANG Tao)

Oxide transistor is the basic device to construct the oxide electronic circuit that is the backing to develop

integrated oxide electronics with high efficiency and low power consumption. By growing the perovskite oxide

integrated layers and tailoring them to lead semiconducting functions at their interfaces, the development of oxide

transistors may be able to perform. We realize a kind of p–i–n type integrated layers consisting of an n-type

cuprate superconductor, p-type colossal magnetoresistance manganite, and a ferroelectric barrier (i). From this,

bipolar transistors were fabricated at the back-to-back p–i–n junctions, for which the Schottky emission and

p–n junction barriers, as well as the ferroelectric polarization, were integrated into the interfaces to control the

transport properties; a preliminary but distinct current gain greater than 1.6 at input current of microampers

order was observed. These results present a real possibility to date for developing bipolar all perovskite oxide

transistors.

PACS: 85.30.Pq, 74.72.−h

DOI: 10.1088/0256-307X/29/10/107402

Many kinds of functional materials have been

used to fabricate special, unconventional transistor

devices. More than four decades ago, ferroelectrics

were selected to be the gate material in field effect transistors.[1] Since the 1990s, perovskite (correlated) oxides, high temperature cuprate superconductors (HTSCs) and colossal magnetoresistance (CMR)

manganites have been employed as the channel materials in field effect transistors.[2−4] More recently,

CMR manganite was used in a metal base Schottky

emission type transistor.[5] In these cases, the perovskite oxide HTSCs or CMR manganites, and the

oxide ferroelectrics were just used as one of the functional components in the developed transistors, while

the all perovskite oxide semiconducting type devices

(all perovskite correlated oxide devices) are mostly the

p–n junctions,[6−10] the development of transistors is

still a remained challenge. So far, several reports have

been shown that based on the layered structure of

perovskite (correlated) oxides, their heteroepitaxially

grown interfaces can be controlled to possess unusual

transport effects.[11−15] To develop all perovskite oxide transistors, therefore, possibly to develop the integrated oxide electronics with high efficiency and low

power consumption, firstly an important step is that

how we grow a type of heteroepitaxially integrated

perovskite oxide layers, and tailor it to get the semiconducting transport function in their interfaces. It is

well known that doping can transform perovskite ox-

ide HTSCs and CMR manganites into n- or p-type

(metallic- or semiconducting-type) materials; ferroelectrics can be polarized to act as the barrier (i) in

various junctions,[16] so that, we may grow them into

an all-perovskite oxide p–i–n junction type integrated

layers, which may be the right material to be used

to fabricate the bipolar transistors under the micro

(nano) engineering.

For an n–p–n type bipolar transistor, in basic principle, the charge carrier concentration 𝐶e in the n-area

of the emitter must be much higher than that in the

p-area,[17] 𝐶b , i.e., 𝐶e ≫ 𝐶b . To satisfy such requirement, we need to grow the all perovskite oxide p–i–n

junction type integrated layers by selecting suitable

materials. The metallic electron-doped cuprate superconductor La2−𝑥 Ce𝑥 CuO4 (LCCO) with optimal

doping of 𝑥 = 0.11 was selected to be the n-type layer,

since it has the Nd2 CuO4 (T′ -phase) structure[18] and

the highest 𝑇C (the highest electron concentration in

the normal state) in this family. The hole-doped manganite, La1−𝑥 Sr𝑥 MnO3 (LSMO) with 𝑥 = 0.12, was

selected to be the p-type layer on account of its intrinsic p-type semiconducting property.[19] The perovskite

oxide ferroelectric Ba0.5 Sr0.5 TiO3 (BST) was used as

the artificial depletion layer (barrier layer (i)) because

of its n-type semiconducting transport feature[20] and

its high Curie temperature and large dielectric constant, in addition, its lattice matches well with that

of both LCCO and LSMO (hereafter, it will be re-

* Supported by the Knowledge Innovation Program of the Chinese Academy of Sciences under Grant No KJCX2YW-W16, the

National Basic Research Program of China (2010CB630700), and the National Natural Science Foundation of China (10904116).

** Corresponding author. Email: brzhao@aphy.iphy.ac.cn

† These two authors contributed equally.

© 2012 Chinese Physical Society and IOP Publishing Ltd

107402-1

Express Letter

CHIN. PHYS. LETT. Vol. 29, No. 10 (2012) 107402

0

3.6

2.4

1.2

0.0

-1.2

-2.4

-3.6

2

24 K

0

100

Measured data

2D Fermi

liquid fitting

200

300

Temperature (K)

(c)

=300 K

-2 -1 0

1

Voltage (V)

2

(b)

2

1

0

0 100 200 300 400

2.5

2.0

1.5

1.0

0.5

0.0

-3

3

(10

-2

WScm)

~ 4200 K

(a)

(10

WScm)

3

(10

6

-4

9

WScm)

tion polarization) of BST occurs at around 1.47 V (as

observed in Fig. 1(c)). From these measurements, the

maximum polarization 𝑃 ≥3.5 µC/cm2 and 𝜀𝑟 ≥275 at

300 K were determined. These dielectric constant data

are basically consistent with that reported in Ref. [22].

On the other hand, our data also indicate that, for

BST, the critical thickness for ferroelectricity should

be smaller than 30 nm, which is somewhat similar to

that reported for other ferroelectric materials.[23] All

these results indicate that BST is suitable for use in

the nano-scale electronic devices.

Polarization (mC/cm )

ferred to as S′ to distinguish it from the semiconducting LSMO). Thus the integrated material that we need

to develop is an M–S′ –S p–i–n tri-layers, on which various passive devices can be fabricated, as well as n–p–

n-type bipolar transistors, which is our main purpose

in the present work.

Results: The phase structure and microstructure

of the integrated layers were tested by x-ray diffraction

and high-resolution transmission electron microscopy,

respectively. The transport properties of each layer

satisfied the requirements for the n–p–n-type bipolar

transistor were characterized. The resistivity of the

LCCO top layer; the longitudinal resistivity 𝜌𝑥𝑥 , Hall

resistivity 𝜌𝑥𝑦 , and charge carrier (hole) concentration

𝑛h of the LSMO layer; the mobility 𝜇e and the diffusion length 𝐿 of the electrons within the LSMO layer,

as well as the dielectric constant and polarization of

the BST layer, were all measured and estimated.

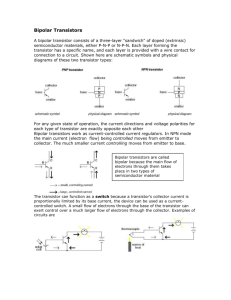

Electrical properties of each layer of integrated p–

i–n integrated layer : From Fig. 1(a), it can be seen

that the resistivity of the LCCO top layer is at the

order of 1 × 10−4 Ω·cm, it is the typical metallic transport feature in the normal state (the electrons concentration 𝑛e is at the order of 1 × 1021 cm−3 ), with

𝑇C ≥24 K. In Fig. 1(b), the black line gives the 𝜌𝑥𝑥 –𝑇

relation of the LSMO layer in the temperature range

from 4.5 K to 400 K, and we can see that there is an

insulator to metal transition at ∼260 K, above which

it is semiconducting, and 𝜌𝑥𝑥 ∼ 2.36 × 10−2 Ω·cm at

300 K. The red line shows the positive Hall resistivity 𝜌𝑥𝑦 ∼ 𝑇 of the LSMO layer in the temperature

range from 40 K to 300 K under a magnetic field of

5 T. At 300 K, 𝑅𝑥𝑦 = 244 Ω, 𝜌𝑥𝑦 ∼ 2.40 × 10−3 Ω·cm,

and the hole concentration 𝑛h is estimated to be

1.54 × 1018 cm−3 . The mobility of holes in the LSMO

layer is estimated to be 𝜇h ∼ 170 cm2 /V·s. Since the

effective mass of electron is smaller than that of hole,

the electron mobility 𝜇e within the LSMO layer should

be >170 cm2 /V·s, which is similar to the case of silicon

with an electron doping concentration of 1018 cm−3 at

300 K.[21] Based on the above carrier concentration,

the diffusion coefficient of electrons within the LSMO

layer is estimated to be 4.42 cm2 /s, thus the electron

diffusion length 𝐿 is about 2.10 × 10−5 cm (210 nm).

All these results confirm that the LSMO layer has intrinsic p-type semiconducting transport feature, and

can be used in the p-area of both emitter and collector, as well as the common base of the transistor. In

Figs. 1(c) and 1(d), the ferroelectricity, i.e., the hysteresis loop (𝑃 –𝑉 curve) and the relative dielectric

constant 𝜀𝑟 of the BST layer with thickness of 30 nm

are presented, respectively. Both were measured in

situ on the BST layer within LCCO/BST/LSMO layers with 30 µm × 100 µm in plane size, which is the

same as that of the emitter and collector shown in the

following. In this case, the hysteresis loop of the BST

layer should be determined by p–i–n junction feature,

and the polarization of BST is limited by its built-in

field, 1.47 V, which is estimated in the following. That

is, when the applied voltage is reached and larger than

1.47 V, the polarization of BST will be no longer to increase. That is, a maximum polarization (not satura-

Temperature (K)

290 (d) =300 K

285

280

275

270

265

260 0.0 0.2 0.4 0.6 0.8 1.0

Voltage (V)

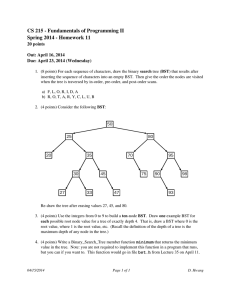

Fig. 1. Transport characteristics of the integrated layers.

(a) Resistivity 𝜌(𝑇 ) of the LCCO top layer in the temperature range of 4.5–300 K. 𝑇C ≥24 K, 𝜌(𝑇 ) is in the order

of 10−4 Ω·cm, and obeys the 2D Fermi liquid model in

the temperature range from ∼80 K to above 300 K with

𝑇𝐹 ∼ 4200 K. (b) Resistivity 𝜌𝑥𝑥 (𝑇 = 4.5–400 K, black

line) and Hall resistivity 𝜌𝑥𝑦 (𝑇 = 40–300 K at 𝐻 = 5 T,

red line)) of the LSMO layer, a metal-insulator transition in 𝜌𝑥𝑥 (𝑇 ) occurs at ∼260 K; above which 𝜌𝑥𝑥 (𝑇 ) is

in semiconducting nature. In the temperature range of

220–250 K, 𝜌𝑥𝑦 (T) shows scattering due to the magnetoresistance effect. (c) The ferroelectricity and (d) dielectric

constant of the BST layer are in situ measured on the integrated layers with the same areas as that of emitter and

collector.

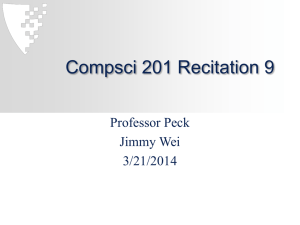

Configuration of the transistor on p–i–n junction

type integrated layers: On the (M–S′ –S) p–i–n integrated layers, bipolar transistors consisting of backto-back p–i–n junctions (emitter and collector) were

fabricated by ion beam and focus ion beam (FIB) etching described as follows: the LCCO layer is the n-area

of the emitter (NAE), and the n-area of the collector

(NAC); the LSMO layer is the p-area of the emitter

and collector, and the common base of the transistor (Fig. 2(a)). The thickness of the BST layer within

which the depletion layer of the p–i–n junction forms

is 𝑡b = 20–30 nm, which should be adjusted to ensure

the formation of the depletion layer, which will be

discussed in the following. The plane size of the emitter and collector were designed to be 30 µm × 100 µm;

the length of the base (LSMO layer) is 30 µm, and its

width 𝑊b is in the range of 100–200 nm, less than the

electron diffusion length of 210 nm within the base. A

top view photomicrograph (Fig. 2(b)) shows the planar configuration of the bipolar transistor. The elec-

107402-2

Express Letter

CHIN. PHYS. LETT. Vol. 29, No. 10 (2012) 107402

trodes (leads) and the width of the base made by

FIB were examined by a scanning electron microscope

(SEM) (Figs. 2(c) and 2(d)); the width of the base,

𝑊b ∼ 180 nm, is shown here for a typical case. It can

be seen that, around the base, the amorphous BST

cover layer was damaged during the FIB etching, but

underneath, the etched groove (within the integrated

layers) is distinct, indicating that the integrated layers

have retained a perfect structure after the FIB etching.

(a)

Electrodes

LCCO

BST

LSMO

C

E

B

(here the minus means that the p-area of p–i–n junction is biased by negative voltage), the F-N tunneling

leakage current appears for both emitter and collector.

This tells us that the thickness of 20 nm is not suitable

for BST in the present p–i–n junction. In the case of

𝑡b ∼ 30 nm, both emitter and collector show typical

p–n junction type 𝐼–𝑉 curves (Figs. 3(a) and 3(b)),

which means that a complete depletion layer can form

within a 30-nm-thick BST layer. The rectifications of

both emitter and collector are larger than 200, which

were also determined from the ratio of the current values at ±3 V. From a simple comparison between the

𝐼–𝑉 curves tested for the cases of 𝑡b ∼ 20 nm and

𝑡b ∼ 30 nm, the depletion layer formed in the latter

can be deduced to be ≤ 10 nm in thickness.

Base

3

2

1

0

100 -6 -4 -2 0 2 4 6

(mA)

100 mm

Electrode

Collector

(mA)

BC

0

-4 -2 0 2 4

BE

2

) (A/V )

(d)

2

180 nm

(V)

-13.5 -1.5 V

-14.0

-14.5

p n:BE

300 K

-15.0

0.0 0.5 1.0 1.5 2.0

The rectification of the emitter and collector : Testing the rectification of the emitter and collector is an

important step to determine how large the thickness 𝑡b

of the BST layer should be to produce sufficient minority carriers for the current gain of the transistor. The

rectification measurements of the emitter and collector were performed under forward and reversed biases

of 𝑉𝑏𝑒 (bias voltage between NAE and base) and 𝑉bc

(biased voltage between NAC and base), respectively.

In the case of 𝑡b ∼20 nm, the 𝐼–𝑉 curves of the emitter and collector show a relatively larger current, up to

100 µA, but their rectifications are small, ≤10, which

are determined by the ratio of the current values obtained at ±3 V bias (Figs. 3(c) and 3(d)). It can be

seen that there are Fowler–Nordheim (F-N) type tunneling leakage currents[24] in the 𝐼–𝑉 curves (Figs. 3(e)

and 3(f)), which are derived from the 𝐼–𝑉 data at the

reversed bias (Figs. 3(c) and 3(d)). We can see that

when the bias 𝑉be (𝑉bc ) > −1.5 V (7.5 × 105 V/cm)

1/

-6 -4 -2 0 2 4 6

(d)

p-n:BC

300 K

-4 -2 0 2 4

(1/V)

-13.5

-14.0

(V)

(f)

-1.5 V

p n:BC

-14.5

300 K

0.0 0.5 1.0 1.5 2.0

-

ln(

ln(

Fig. 2. Configuration of bipolar oxide transistor: (a)

scheme of the p–i–n junction based bipolar transistor fabricated on (M–S′ –S) p–i–n integrated layers, (b) top-view

photomicrograph of the bipolar transistor device. The

leads and the base width are shown in the SEM images

of (c) and (d).

p-n:BC

300 K

BC

(e)

-

1.00 mm

(b)

50

0

2

Base

50

) (A/V )

BE

Pt

2

(mA)

Pt

p-n:BE

300 K

8

6

4

2

0

100

(c)

Electrode

Emitter

BC

BE

(b)

(c)

p-n:BE

300 K

(mA)

(a)

STO(001)

1/

(1/V)

Fig. 3. Rectifications (𝐼–𝑉 curves) of the emitter and collector of the bipolar perovskite oxide transistor devices at

300 K. 𝐼–𝑉 curves of emitter (a) and collector (b) of the

bipolar transistor: the thickness 𝑡b of the BST layer is

∼30 nm, the rectifications determined by the current ratio

at ±3 V, are larger than 200. The forward currents are all

in the order of µA, the forward voltages are ∼2 V, and the

breakdown voltages are larger than 6 V. (c) and (d) Rectifications (∼7–8) of the emitter (c) and collector (d) of

the bipolar transistor device on the integrated layers with

𝑡b ∼ 20 nm. The F-N tunneling leakage current can be

seen clearly from both (e) and (f), when the reversed bias

𝑉be (𝑉𝐵𝐶 ) > −1.5 V (7.5 × 105 V/cm); the 𝐼–𝑉 data at

the forward bias is the sum of the forward p–i–n junction

current and the F-N tunneling leakage current.

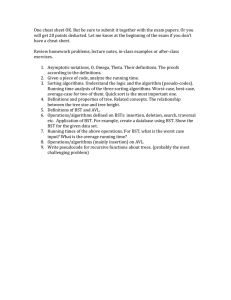

The current gain of the present bipolar transistors:

The current gain 𝛽 of the bipolar transistor is determined by the relation 𝛽 = (𝐼c − 𝐼ceo )/𝐼b ,[17] where 𝐼b

is the input current, 𝐼c and 𝐼ceo are the output currents of the collector with and without input current,

and are measured by using the common emitter mode

circuit,[17] where the input current 𝐼b comes from the

circuit between the emitter and base, the output current 𝐼c and 𝐼ceo are controlled by the bias voltage between NAE and NAC, 𝑉ce . Since the output current

𝐼ceo of the collector is measured when the input cur-

107402-3

Express Letter

CHIN. PHYS. LETT. Vol. 29, No. 10 (2012) 107402

beam (30 nA) was employed. The scanning electron

microscope was used to check the etched morphology

as described above (Fig. 2(c)).

120

100

80

60

40

20

0

1.0

0.8

0.6

m

m

0.4

m

0.2

-2 0 2 4 6 1.0 1 2 3 4 5

0.4

0.9

0.8

0.2

0.7

m

0.0

m

0.6

-0.2

m

-3-2-1 0 1 2 3 0.5 1.0 1.5 2.0 2.5 3.0

6

m

1.6

m

1.5

4

m

1.4

1.3

2

1.2

0

1.1

-2-6 -4 -2 0 2 4 6 1.0 1 2 3 4 5

Unit: mA

100

90

80

70

60

50

40

30

20

10

c

( A)

(a)

(mA)

c

(e)

(mA)

(b)

10 A

20 A

30 A

0

(c)

c

rent 𝐼b is zero, it is suggested to be the leakage current

between the emitter and collector; the output current

𝐼c is produced by the bias 𝑉ce and input current 𝐼b , in

order to get maximum current gain, the output current 𝐼c should be as large as possible. We search the

conditions to get large current gain by mainly testing

the BST layer thickness 𝑡b and base width 𝑊b , the former determines how large amount of minority carriers

can be emitted from the emitter, and the latter determines that how large amount of minority carriers can

diffuse from emitter to collector. So far, about sixty

bipolar transistor devices have been fabricated on our

(M–S′ –S) p–i–n junction type integrated layers.

Figure 4 presents the results obtained from the

tested three types of transistor devices. (1) For a type

of device: the thickness of the BST layer 𝑡b is ∼20 nm,

which is smaller than the required value 30 nm as mentioned above, so F-N tunneling type leakage exists, the

rectifications of both emitter and collector are small,

≤10; 𝑊b is ∼160 nm, which is smaller than the diffusion length 𝐿 (= 210 nm), a large amount of charge

carriers can diffuse from emitter to collector, but such

carriers are almost the leakage carriers. In this case,

the 𝐼c is large, while 𝛽 is small, it is in the range

of 0.95–0.98, no current gain is obtained. This reveals

an intrinsic problem that so long as the tunneling type

leakage current exists, no matter how large 𝐼c is, the

current gain is always strongly suppressed. The reason

for this is that when there is a tunneling current, the

barrier of p–i–n junction will be shorted and no longer

to play the role for p–i–n junction effect. In particular, when the 𝐼ceo is the tunneling current, it increases

rapidly with 𝑉ce , resulting in a sharp decrease of 𝛽. All

these can be seen in Figs. 4(a) and 4(b).

(2) For a type of device: the thickness of the BST

layer 𝑡b is ∼30 nm, the depletion layer can form within

it, and the good p–i–n junction forms, resulting in a

rectification larger than 200 for emitter and collector, as shown in Figs. 3(a) and 3(b). However, the

𝑊b (∼250 nm) is larger than the diffusion length 𝐿 of

electron in base, the minority carriers (electrons) emitted in emitter cannot diffuse through such wide base

from the emitter to the collector, i.e., the collector cannot be correlated by minority carrier transport to the

emitter, the 𝛽 is in the range of 0.90–0.95 (Figs. 4(c)

and 4(d)). This result may be understood from two

aspects: one is that the emitted minority carriers are

probably recombined by any kinds of the recombination centers which exist within the base; the other is

that the emitted minority carriers are probably accumulated within the base, which results in block of any

further diffusion of minority carriers. In the present

study, in order to reduce the probability of the recombination, the semiconducting type LSMO base with

a relative lower hole concentration of 1018 cm−3 has

been chosen. This concentration not only can limit

the number of recombination centers, but also can lead

to a relatively larger mobility and diffusion length for

the minority carriers in the base. Protecting the structure of the base during the FIB etching process is also

an effective way to reduce the occurrence of recombination centers within the base. Hence a small ion

0.5 mA

0.4 mA

0.3 mA

0.2 mA

0.1 mA

0 mA

(d)

0.1 A

0.2 A

0.3 A

5 mA

4 mA

3 mA

2 mA

1 mA

0 mA

ce

1 A

2 A

3 A

(f)

(V)

ce

(V)

Fig. 4. Characteristics of the bipolar perovskite oxide

transistor devices at 300 K as a function of 𝑉ce for different 𝐼b . (a) and (b) With 𝑡b ∼20 nm and a base width of

𝑊b ∼160 nm: (a) the large 𝐼ceo and 𝐼c lead to a negligible small current gain; (b) 𝛽 = 0.95–0.98. This low value

is due to the existence of an F-N type tunneling leakage

current in the emitter and collector, especially, 𝐼ceo increases with 𝑉ce , 𝛽 decreases with 𝑉ce rapidly. (c) and

(d) With 𝑡b ∼ 30 nm and a base width of 𝑊b ∼ 250 nm:

(c) due to the larger 𝑊b , the emitter and collector cannot

be correlated, so 𝐼c is very small (order of 0.1 µA), and in

(d) no current gain can be observed (𝛽 = 0.90–0.95). (e)

With 𝑡b ∼ 30 nm and a base width of 𝑊b ∼160 nm. Here

𝐼ceo and 𝐼c have reasonable values, i.e., 𝐼ceo is ≤0.5 µA (at

𝑉ce = 3 V). When the input current 𝐼b is on the order of

µA and is increased in steps of 1 µA; 𝐼c is in the range of 1–

6 µA. For each value of 𝐼b , 𝐼c (> 𝐼b ) is distinctly observed.

(f) Plot of 𝛽 versus 𝑉ce (or equivalently, 𝐼b ). When 𝐼b increases, then 𝛽 decreases; at 𝐼b = 1 µA, 𝛽 has a maximum

value ≥1.60 (at bias 2 V), and at 𝐼b = 2 µA, the maximum

of 𝛽≥1.20 (at bias 3.5 V). See text for details.

(3) For a type of device: the thickness of BST

layer 𝑡b is ∼30 nm and 𝑊b ∼160 nm, based on which

the depletion layer can form, and the minority carriers can diffuse from emitter to collector. We can

see that in Fig. 4(e), for various input currents 𝐼b , the

corresponding 𝐼c (> 𝐼b ) is distinctly observed. The

dependence of 𝛽 on 𝑉ce for different values of 𝐼b , is

plotted in Fig. 4(f), where there is a maximum current gain 𝛽 ≥= 1.60 at the bias of 2 V, i.e., 𝐼b = 1 µA

and 𝐼c >1.6 µA. This is indeed the current gain for

our bipolar perovskite oxide transistor. When the input current is increased, 𝛽 decreases, i.e., 𝐼b = 2 µA,

a lower maximum current gain of 𝛽≥1.20 is observed,

which occurs at a relative larger bias 3.5 V. The fact

that 𝛽 is larger for smaller input currents can be attributed to the increase in the effective diffusion constant of the minority carriers resulting from the electron concentration gradient setup in the base, while

the decrease of 𝛽 for larger input currents results from

107402-4

CHIN. PHYS. LETT. Vol. 29, No. 10 (2012) 107402

the accumulation of charge carriers in the base region,

that is, the large amount of minority carriers will also

lead to accumulation of charge carriers though the

width of base is smaller than the diffusion length, this

is similar to the case in conventional semiconductor

transistors.[17] All these data indicate that both the

suitable thickness of the BST layer and the width of

the base are the basic construction parameters to get

current gain of the bipolar oxide transistors. On the

other hand, for the bipolar oxide transistor, the current gain strongly depends upon the optimal working

voltages and input currents.

Vbi=(SB-DB)+PNB

PNB

SB

LSMO(p)

PNB

BST(n)

LCCO(n)

SB

BST(n)

LCCO(n)

0.85 eV

0.62 eV

Ec

Ec

Ev

Ev

0.62 eV

{static state

EF

SB

-

PNB

DB

PNB

+’-

+’-

+’-

DB

DB

DB

Electrons diffuse

EF +bias}

SB

+’DB

+

{bias state}

Electrons

Minority carriers

under the carriers

transport

(electrons)

concentration

under bias

Transport

gradient within

under bias

the base with

constant potential

Fig. 5. Barrier (band diagram) of the bipolar perovskite

oxide transistor devices. Upper: the barriers (built-in

field, 𝑉bi ) of the emitter and collector, which are established from the Schottky barrier (SB) at the LCCO/BST

interface and the p–n junction barrier (PNB) at the

BST/LSMO interface, and the depolarization barrier (DB)

of the BST (shown in the lower part). The barrier of the

whole transistor is constructed at the back-to-back emitter and collector. Lower: the barrier of the bipolar transistor under the forward bias (NAE is biased negatively

and NAC positively). The direction of the depolarization barrier DB of the BST layer is opposite to that of

SB, so it lowers the barrier at the LCCO/BST interface.

Combining the barrier as presented in the upper diagram,

the barrier of the p–i–n junction (emitter and collector)

is (SB−DB)+PNB=0.62 V+0.85 V, so that increasing the

forward bias further, the electrons as minority carriers are

emitted from the NAE to the base, and diffuse along the

base to the collector, finally, to be pulled by the bias 𝑉ce

to NAC to form the output current of the collector (see

text for details).

Discussion: In principle, the transport ability

of the present bipolar oxide transistor is determined by the barriers formed in the interfaces of

the (M–S′ –S) p–i–n junction type integrated layers

and the base width between intimately contacted p–

i–n junctions, so it is first necessary to understand

the band diagram of the (LCCO/BST/LSMO) p–

i–n junctions. It can be considered that the whole

built-in field 𝑉bi of the (LCCO/BST/LSMO) p–i–

n junction is formed by the barrier at the interface of metallic LCCO(n)/semiconducting BST(n)

and the barrier at the interface of semiconducting

BST(n)/semiconducting LSMO(p), and the polarization of the BST layer. According to Mott and

Schottky, there is a Schottky barrier (SB) at the

LCCO/BST interface,[25,26] and a p–n junction barrier

(PNB) near the interface of BST/LSMO, as shown in

Fig. 5. The height and direction of barrier SB is deter-

Express Letter

mined by the difference between the value of the work

function 𝑊𝑚 of LCCO and the affinity 𝜒𝑠 of BST.

To determine this, we grew a bi-layer of LCCO/BST

on an Nb-doped SrTrO3 (NSTO) substrate, and measured the current-voltage (𝐼–𝑉 ) characteristics (Pt

electrodes were deposited on the LCCO layer and the

NSTO substrate, NSTO is also in the metallic transport feature). The results were analyzed according

to the Schottky model with the method described

in Ref. [27]. From the 𝐼–𝑉 curve data, the value

of 𝑊𝑚 − 𝜒𝑠 = +0.62 V was determined. Here we

should take into consideration that, during the measurement, the BST layer is polarized by the applied

bias, the role of its depolarization barrier (DB) is to

lower the Schottky emission barrier, thus, here the

value of 𝑊𝑚 − 𝜒𝑠 = +0.62 V is actually the result of

SB−DB (Fig. 5), and the band bends upward from

BST to LCCO near the interface of BST/LCCO. The

height of PNB (𝑉pn ) is the difference between the

Fermi levels of BST and LSMO. According to the

definition of Fermi level, and based on the carrier

concentrations (𝑛h of LSMO ∼ 1.54 × 1018 cm−3 , 𝑛e

of BST ∼ 1016 cm−3 , and intrinsic carrier concentration 𝑛𝑖 ∼ 1010 cm−3 ), the value of 𝑉pn is estimated

to be ∼0.85 V, and the band bends upward from

BST to LSMO near the interface of BST/LSMO.

Therefore, the total barrier height of the junction

is 𝑉bi = (SB−DB) + PNB = 0.62 V + 0.85 V = 1.47 V

(combining upper part and lower part of Fig. 5), which

is indeed the integration of Schottky emission, p–n

junction barriers and ferroelectric polarization in the

interfaces. This is the barrier for the minority carriers

emitted from NAE to the base. This barrier height

is consistent with the forward bias voltages of 1.4–

2.0 V obtained from the data of 𝐼–𝑉 curves of emitter

and collector (Figs. 3(a) and 3(b)). From Fig. 5, we

can understand that, increasing the forward voltage

further, the LCCO/BST interface barrier is lowered,

the minority carriers then are emitted by overcoming the barrier (SB−DB)+PNB from the NAE to the

base; then they diffuse along the base to the collector

(driven by the carrier concentration gradient within

the base); and finally are pulled by the reversed (positive) bias voltage 𝑉ce to NAC to form the output

current. We can evaluate the transport route of minority carriers of this transistor as that the minority

carriers pass perpendicularly through the large junction area of the emitter, diffuse parallel along the

base plane which is shorter than the diffusion length

of electron, then pass perpendicularly through the

large junction area of the collector, which is quite an

expedient transport route. This configuration is thus

advantageous for the bipolar oxide transistors.

The growth of integrated layers and the fabrication of bipolar transistors: The growth of such integrated layers is similar as that of metallic oxide p–i–n

junctions.[28] Here several important aspects must be

stressed. The lattice mismatch (0.8%) of LSMO and

SrTiO3 (STO) is smaller than that (2.5%) of LCCO

and STO, so the LSMO was taken to be the first

(bottom) layer to grow on the (100) STO substrate,

on top of which BST and LCCO layers were succes-

107402-5

CHIN. PHYS. LETT. Vol. 29, No. 10 (2012) 107402

sively grown. All the layers were deposited by pulsed

laser deposition method (equipment: Lambada Physik

Comper 205. Gas is XeCl, the laser wavelength is of

308 nm, and a pulse frequency is of 4 Hz). In order to

avoid the interface diffusion, the deposition temperature of the LSMO and BST layers was taken to be

higher, 820∘C, the deposition temperature of LCCO

was 790∘C. The thicknesses of the LSMO, BST and

LCCO layers were monitored by counting the number of pulses of the laser (the deposition rate was

calibrated to be 0.03 nm per pulse at a power density of 16 mJ/cm2 ) and controlled to be 100, 20–30,

and 100 nm, respectively. To maintain the intrinsic

transport features of each layer and the distinct interface effects of the integrated layers, the most important issue is the in situ annealing treatment. That is,

the first two layers, i.e. the LSMO and BST layers,

must be fully oxidized after deposition under a higher

oxygen partial pressure (40 Pa), so that they can attain a perfect structure with good intrinsic transport

properties. The as-deposited LCCO layer, however,

is an insulating T-phase, it must be to have a reduction treatment to become an n-type metallic T′ phase. The experiments show that the treatment under 10−4 Pa order vacuum and 650∘C for 15 min can

get good LCCO layer and without detrimental influence on BST/LSMO layers.

We took five stages for micro (nano) fabrication

of the bipolar transistor devices: First, a zone of size

30 µm × 300 µm was cut by ion-beam etching from the

integrated LCCO/BST/LSMO tri-layers. The second

ion beam etching stage was carried out on this zone to

separate out a zone of 30 µm × 200 µm for the emitter

and collector, and a zone of 30 µm × 100 µm for making the base electrode. For the latter, both LCCO

and BST layers were removed by ion beam etching

to expose the surface of the LSMO layer. In the third

stage, a 100-nm-thick layer of amorphous (Ba,Sr)TiO3

(AMBST) was deposited on the entire surface for protection and electric isolation. The fourth stage was to

construct the emitter, collector and base. A groove of

width 100–200 nm was etched by FIB etching in the

middle of the zone of 30 µm × 200 µm, from the surface of the AMBST to that of the LSMO, throughout

the whole width of this zone. The emitter, collector

(both are in the size of 30 µm × 100 µm) and the 100–

200 nm wide common base (LSMO layer) were thus

all created. That is, the bipolar n–p–n type transistor

was composed of back-to-back (LCCO/BST/LSMO)

p–i–n junctions. Here, the width of the base, 150–

200 nm, was designed to be smaller than the ∼210 nm

electron diffusion length within the LSMO layer, to

ensure the diffusion of minority carriers from emitter

to collector. In the fifth stage, the Pt electrodes and

leads of the emitter, collector and base were deposited

on the surfaces of the LCCO (n-area of emitter and narea of collector), and the LSMO (base), respectively.

All these were carried out using FIB etching to re-

Express Letter

move the AMBST layer and to deposit the platinum.

The leads were connected to the external PtIr alloy

electrode, where the external circuit was linked for all

measurements. In order to protect the structure of the

base during the FIB etching process, a small ion beam

current (30 nA) was employed. The scanning electron

microscope was used to check the etched morphology

(Fig. 2(c)).

All fabricated transistors, the resistances of the

emitter and collector circuit were 104 –106 Ω, all electrodes were in ohmic contact, and the contact resistance was on the order of ohms, so all the measurements are regarded to be reliable. In the present study,

the transistors were characterized at room temperature.

We thank Shun-chun Liu, Shu-heng Pan and Lingan Wu and Jun Miao for discussions, thank Chao-ying

Wang for SEM testing.

References

[1] Heyman P M and Heilmeier G H 1966 Proc. IEEE 54 842

[2] Mathews S, Ramesh R, Venkatesan T and Benedetto J 1997

Science 276 238

[3] Mannhart J, Schlom D G, Bednorz J G and Müller K A

1991 Phys. Rev. Lett. 67 2099

[4] Grekhov I, Delimcva L, Liniichuk I, Mashovets D and

Veselovsky I 2003 Physica E 17 640

[5] Yajima T, Hikita Y and Hwang H Y 2011 Nat. Mater. 10

198

[6] Mannhart J, Kleinsasser A, Ströbel J and Baratoff A 1993

Physica C 216 401

[7] Blom P W M, Wolf R M, Cillessen J F M and Krijn M P

C M 1994 Phys. Rev. Lett. 73 2107

[8] Watanabe Y 1998 Phys. Rev. B 57 R5563

[9] Sugiura M, Uragou K, Tachiki M and Kobayashi T 2001 J.

Appl. Phys. 90 187

[10] Mitra C, Raychaudhuri P, Köbernik G, Dörr K, Müller K

H, Schultz L and Pinto R 2001 Appl. Phys. Lett. 79 2408

[11] Ohtomo A and Hwang H H 2004 Nature 427 423

[12] Cen C, Thiel S, Hammerl G, Schneider C W, Andersen K

E, Hellberg C S, Mannhart J and Levy J 2008 Nat. Mater.

7 298

[13] Park J W, Bogorin D F, Cen C, Felker D A, Zhang Y, Nelson C T, Bark C W, Folkman C M, Pan X Q, Rzchowski

M S, Levy J and Eom C B 2010 Nat. Commun. 1 94

[14] Schlom D G and Mannhart J 2011 Nat. Mater. 10 168

[15] Ahn C H, Triscone J M and Mannhart J 2003 Nature 424

1015

[16] Evgeny Y T and Hermann K 2006 Science 313 181

[17] Levine U N 1963 Principle of Solid-State Microelectronics

(Holt, Rinehart and Wiinston, Inc.)

[18] Tokura Y, Takagi H and Uchida S 1989 Nature 337 345

[19] Salamon M B and Jaime M 2001 Rev. Mod. Phys. 73 583

[20] Hwang C S, Park S O, Cho H J, Kang C S, K H K, Lee S

I and Lee M Y 1995 Appl. Phys. Lett. 67 2819

[21] Grundmann M 2006 The Physics of Semiconductors

(Berlin: Springer-Verlag) P191

[22] Hwang C S 2002 J. Appl. Phys. 92 432

[23] Junquera J and Ghosez P 2003 Nature 422 506

[24] Sze S M 1998 Physics of Semiconductor Devices 2nd edn

(New York: Wiley) p 28

[25] Mott N F 1938 Proc. Combridge Philos. Soc. 34 568

[26] Schottky W 1940 Phys. Z. 41 570

[27] Norde H A 1979 J. Appl. Phys. 50 5052

[28] Yuan J, Wu H, Cao L X, Zhao L, Jin K, Zhu B Y, Zhu S

J, Zhong J P, Miao J, Xu B, Qi X Y, Qiu X G, Duan X F

and Zhao B R 2007 Appl. Phys. Lett. 90 102113

107402-6