Emitter-coupled Logic

advertisement

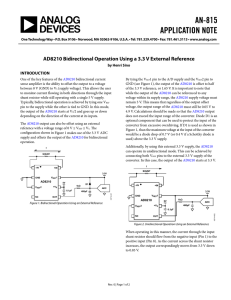

Emitter-coupled Logic INEL4207 Digital Electronics - M. Toledo - ECE Dept. - UPRM 1. Current switch ECL gates are based on the following circuit, which works as a current switch, so we will study it first. R vC1 vIN Q1 Q2 VREF IEE -VEE Let vE be the emitter voltage of both Q1 and Q2 . The base-emitter voltage difference for Q1 is vIN − vE , and for Q2 it is VREF − vE . Thus the collector currents will be iCQ1 = IS e and vIN −vE VT iCQ2 = IS e ; VREF −vE VT vIN −vE vIN −VREF ∆V iCQ1 e VT VT = VREF −vE = e = e VT iCQ2 e VT where ∆V ≡ vIN − VREF , i.e. it is the difference between the base voltages. If vIN > VREF , iCQ1 > iCQ2 , else if vIN < VREF , iCQ1 < iCQ2 . Because the current ratio is proportional to the exponential of ∆V /VT and, at room temperature, VT is only about 0.025V , a small voltage difference gives place to large current difference. For example, if ∆V = 0.3V , iCQ1 is over five orders of magnitude larger than iCQ2 , which means that practically the whole IEE current would flow through Q1 . Similarly if Q1 ’s base voltage is 0.3V below the reference voltage, almost no current would flow through Q1 . If the output is taken at Q1 ’s collector, the circuit works as a basic inverter. Assuming that | ∆V | is much larger than VT , subtracting the voltage drop across R from ground we get 0 if ∆V < 0 vC1 = −IEE R if ∆V > 0 Thus, a low input (vIN below VREF ) produces a high output (0V ) and high input (vIN above VREF ) produces a low output (−IEE R). By properly selecting R and VREF , the output high and low voltage levels could be made compatible with the input levels. For example, we could select VREF = −0.3, VH = 0V and VL = −0.6V . Then setting IEE = 0.3mA and R = 2kΩ would produce the same voltage levels at the output. It is, however, difficult to produce a thermally-compensated reference source of 0.3V . Also, loads (i.e. other inverters or gates of the same type) connected directly to the collector of Q1 would sink additional current current and produce an undesirable voltage reduction. Thus, practical ECL circuits use a lower reference voltage and add an output buffer, as shown next. 1 2. Emitter-coupled logic inverter A basic ECL inverter is sketched in the following diagram. R vC1 vIN Q3 Q1 Q2 VREF vO IE3 IEE -VEE The circuit adds a follower stage to the current switch, and also makes the output voltage levels to be compatible with the input levels. When a low level is applied to the input, no current flows through Q1 , vC1 = 0V and the output assumes the high level, VH = −0.7V VREF must be selected so that, when the input voltage is set to vIN = VH = −0.7V , almost all of IEE flows through Q1 , so that the output reach the low level, VL = −RIEE − 0.7V The value of VREF would usually be the average of VH and VL , 1 (VH + VL ) 2 1 (−RIEE − 0.7V − 0.7V ) = 2 1 = − RIEE − 0.7V 2 VREF = (1) (2) (3) If we want to make VL = −1.5V so that VH − VL = −0.7V − (−1.5V ) = 0.8V and ∆V = 0.4V , we can select VREF = −1.1V and R × IEE = 0.8V ; thus we could set IEE = 100µA and R = 8kΩ. Another set of values that would work are VL = −1.3V , ∆V = 0.3V , VREF = −1V , IEE = 300µA and R = 2kΩ. Current source implementation The constant current sources shown in the previous circuit can be implemented using transistors, as shown in the following diagram. Look at 3. R vC1 vIN Q3 Q1 Q2 RCS VREF vO IEE Q4 A4 Q5 Q6 A5 A6 -VEE 2 A4,5,6 represent the emitter areas of Q4,5,6 . For transistors with the same base-emitter voltages (such as Q4 , Q5 and Q6 ), a larger/smaller emitter means the emitter current increase/decreased by the ratio of the areas. The circuit works by selecting RCS to obtain currents iC4 ≈ 0V − 0.7V − (−VEE ) VEE − 0.7V = RCS RCS and A5 A6 iC4 ; iC6 = iC4 A4 A4 For example, an IEE = 300µA constant-current source based on a −5.2V supply could be implemented −0.7V = 15kΩ and using equal areas for Q4 and Q5 . If we want Q6 ’s collector current by selecting RCS = 5.2V.3mA to be 100µA, we simply have to set A6 = A4 ÷ 3. iC5 = ECL with resistors The alternative circuit shown next avoids the use of current sources by replacing them with resistors. R vC1 vIN Q3 Q2 Q1 VREF IE3 REE IREE vO R3 -VEE2 -VEE To make the discussion concrete, let’s say that we want to use VEE = VEE2 = −5.2V , VH = −0.7V , VL = −1.3V , VREF = −1V , IEE = 300µA and IEE2 = 100µA. The design process could consists on selecting REE so that a 300µA flows through the resistor when vIN = VL = −1.3V ; −1V − 0.7V − (−5.2V ) REE = = 11.7kΩ 0.3mA Then select R to have an output voltage vO = VL = −1.3V when vIN = VH = −0.7V . However, we most take into account that for this input voltage, −0.7V − 0.7V − (−5.2V ) = 326µA 11.7kΩ IREE = so that R= 0.6V = 1840Ω 326µA instead of the 2kΩ used previously. Alternatively, we could select R = 2kΩ and make IREE = 300µA when vIN = −0.7V , so that REE = −0.7V − 0.7V − (−5.2V ) = 12.7kΩ 0.3mA Then, when vIN = VL = −1.3V , −1V − 0.7V − (−5.2V ) = 276µA 12.7kΩ Question: How do you do the design if the average current through REE must be 300µA? IREE = Finally, to select R3 we must assume that the desired value IEE2 = 100µA is an average. Assuming that the output remains equal times at high and low, the average output voltage is just VREF and R3 = −1V − (−5.2V ) = 42kΩ 0.1mA 3 RC1 vC1 Q4 A+B B A Q1B RE RC2 vC2 Q3 Q2 VREF A+B Q1A RE IEE -VEE2 -VEE2 -VEE Figura 1: ECL gate implementing NOR and OR logic functions. Power dissipation The power dissipated by the above circuits can be found from the product of the supply voltages and supply currents. Thus the power dissipation of the previous example is Pave = 5.2V × 300µA + 5.2V × 100µA = 2.08mW Practice problem: find the power dissipated if VEE2 = −2V . If all resistor values are kept the same, find the minimum voltage in Q3 ’s base that will keep the transistor operating in the active region. 3. Additional example Problem statement: Use the circuit shown below to design a circuit with VH = −1.7V and VL = −2.3V . The average power dissipation should be less that 2mW and the supply voltage is −5.2V . Neglect the base currents. R4 R vC1 vIN Q3 Q1 Q2 vO IE3 REE IREE VREF R3 -VEE Solution: The reference voltage must be the average between VH and VL , VREF = 1 (−1.7V − 2.3V ) = −2V 2 The average power is Pave = VEE × (IREE ,ave + IE3,ave ) where IREE ,ave and IE3,ave represent average currents. Since the average output voltage is VREF = −2V , IE3,ave = 5.2V − 2V = 3.2V /R3 R3 4 The average emitter voltages for Q1 and Q2 is IREE ,ave = 1 2 ((−2V − 0.7V ) + (−1.7V − 0.7V )) = −2.55V , so 5.2V − 2.55V = 2.65V /REE REE To assign values to the average currents, observe that IREE ,ave + IE3,ave ≤ Pave,max ÷ VEE = 385µA If we let IREE ,ave = IE3,ave = 192.5µA, then REE = 14kΩ R3 = 17kΩ Notice that the resistor values where round up, so that the currents (and thus the power disspation) are below the target values. We also need to assign values to R and to R4 . Since we are neglecting the base currents, the current through R4 is equal to the current in REE . When vIN = VL , IREE = −2V − 0.7V − (−5.2V ) = 178.5µA 14kΩ For this input, the output voltage must be VH = −1.7V , so R4 = 1V 178.5µA = 5.6kΩ Regarding R, we should use the current flowing through REE when vIN = VH = −1.7V , which is IREE = −1.7V − 0.7V − (−5.2V ) = 200µA 14kΩ When this current flows through Q1 , the output voltage becomes vO = −0.2mA × (R + 5.6kΩ) − 0.7V Since this voltage must equal VL , R= 4. −2.3V +0.7V −0.2mA − 5.6kΩ = 2.4kΩ ECL OR-NOR gate Figure 1 shows how a two-input NOR-OR gate is implemented using ECL. If either one of the inputs A or B is high, current flows through the left leg of the current switch, causing a voltage drop to appear across RC1 and making the left-hand side output to go low. Thus the NOR logic function is accomplished. The circuit’s right-hand and left-hand sides work in similar ways, but Q3 ’s and Q4 ’s emitter voltages will be the complement of each other. The OR function of the inputs is obtained on the right output, as shown in the figure. 5