2.5V Low EMI, Low Dyn Pwr TFT-LCD Timing Cntrlr w/Reduce

advertisement

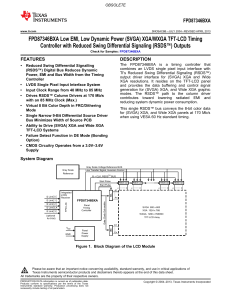

OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 FPD87208AXA +2.5V Low EMI, Low Dynamic Power XGA/WXGA TFT-LCD Timing Controller with Reduced Swing Differential Signaling RSDS™ Outputs Check for Samples: FPD87208 FEATURES DESCRIPTION • The FPD87208AXA is a timing controller that combines an LVDS single pixel input interface with TI Reduced Swing Differential Signaling (RSDS™) output driver interface for XGA and Wide XGA resolutions. It resides on the TFT-LCD panel and provides the data buffering and control signal generation for XGA, and Wide XGA graphic modes. The RSDS path to the column driver contributes toward lowering radiated EMI and reducing system dynamic power consumption. 1 23 • • • • • • Reduced Swing Differential Signaling (RSDS) Digital Bus Reduces Dynamic Power, EMI and Bus-Width from the Timing Controller LVDS Single Pixel Input Interface System Input Clock Range from 25 MHz to 85 MHz Drives RSDS Column Drivers at 170 Mb/s with an 85 MHz Clock (Max) BIST Function CMOS Circuitry Operates from a 2.25V–2.75V; 0°C–70°C 64 TQFP Package with Body Size 10 mm x 10 mm x 1.0 mm This single RSDS bus conveys the 6-bit color data for XGA, and three different WXGA resolutions. System Diagram Gray Scale Voltage Reference BUS Gray scale Reference Line Transfer Signal, Inversion Control . - n . RSDS CD 1 . - n . . RSDS CD 1 . n 1 . n 1 -- A1 XGA/WXGA Panel Timing Controller An XGA 1024 X 768 WXGA 1280 X 768/800/854 TFT-LCD Array E1 VDD - RE Panel Power Supply . GND - RA FPD87208AXA Gate Clock Out enable /2 LinkCLK FPD-Link /2 Link[2] - . /2 Link[1] RSDS CD . /2 Link[0] - . Integrated LVDS Receiver . RSDS CD Start Pulse . Start Pulse . /9 + CLK, RSDSa BUS En Figure 1. Block Diagram of the LCD Module These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates. 1 2 3 Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. RSDS is a trademark of Texas Instruments. All other trademarks are the property of their respective owners. PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. Copyright © 2004–2013, Texas Instruments Incorporated OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 Absolute Maximum Ratings www.ti.com (1) (2) −0.3V to +3.0V Supply Voltage (VDD) DC TTL Input Voltage (VIN) −0.3V to (VDD + 0.3V) DC LVDS Input Voltage (VIN) −0.3V to (VDD + 0.3V) DC Output Voltage (VOUT) −0.3V to (VDD + 0.3V) Junction Temperature +150°C −65°C to +150°C Storage Temperature Range (TSTG) Lead Temperature (TL) (Soldering 10 sec.) HBM: RZAP = 1.5 kΩ, CZAP = 100 pF ESD Rating (1) 260°C 2 kV MM: RZAP = 0Ω, CZAP = 200 pF 200V Absolute Maximum Ratings are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the devices should be operated at these limits. The table of Electrical Characteristics specifies conditions of device operation. If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications. (2) Operating Conditions Supply Voltage (VDD) Operating Temp. Range (TA) Min Max Units 2.25 2.75 V 0 Supply Noise Voltage 70 °C 200 mVPP DC Electrical Characteristics TTL DC Electrical Characteristics VDD = 2.5V ±0.25V, TA = 0°C to 70°C, IPI = 100 µA (Unless otherwise specified) Symbol Parameter Conditions Min Typ Max 2.5 2.75 Units VDD Supply Voltage 2.25 VIH Minimum Input High Voltage 1.8 VIL Maximum Input Low Voltage VOH Output High Voltage IOH = −8 mA VOL Output Low Voltage IOL = 8 mA 0.4 VIN = VDD 10 µA VIN = GND 10 µA 120 IP = 100 µA VDD = 2.75V mA IIN Input Current IDD Average Supply Current 2 V 0.7 CLK = 85 MHz, RPI = 12.3k CL(TTL) = 50 pF, RL(RSDS) = 100Ω and CL(RSDS) = 5 pF (jig & test fixture capacitance), See Figure 3 for input conditions Submit Documentation Feedback V 0.8 x VDD 80 IP = 100 µA VDD = 2.5V Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 DC Electrical Characteristics FPD-Link (LVDS) Receiver Input (RxCLKP/N; RxIN[y]P/N, y = 0,1,2) Symbol Parameter Conditions Min Typ Max Units LVDS RECEIVER DC SPECIFICATIONS Note: LVDS Receiver DC parameters are measured under Static and Steady state conditions which may not be reflective of its performance in the end application. This device is compatible with TIA644 SPEC. V0 and V2.4. VTHLVDS VTLLVDS Differential Input High Threshold Voltage +100 VCM = 1.2V −100 Differential Input Low Threshold Voltage IIN mV VIN = VDD –0.4V, VDD = 2.75V INput Current VIN = 0V, VDD = 2.75V VIN INput Voltage Range |VID| Differential Input Voltage VCM ±10 µA ±10 µA VDD –0.4 V 0.100 0.600 V 0 + |VID|/2 (VDD –0.4) − |VID|/2 V 0 Common Mode Voltage Offset mV LVDS VID and VCM Allowable Operating Range VDD - 0.4V VCM VDD - 0.4V |VID| = 100 mV = (VDD - 0.4V) - |VID|/2 VDD - 0.50V |VID| = 600 mV VCM = (VDD - 0.4V) - |VID|/2 1.425V VDD - 1.0V |VID| = 350 mV 1.075V VCM = 1.25V 600 mV VCM = 300 mV |VID| = 600 mV 100 mV |VID| = 100 mV 0V VCM = 50 mV GND 0V VCM = (1.25V); |VID| = 350 mV |VID| = 100 mV |VID| = 600 mV Typical Application VCM range with Minimum |VID| VCM range with Maximum |VID| Figure 2. |VID| and VCM Definitions FPD-Link Receiver Input Pattern Used to Measure IDD RxCLKIN VDIFF = 0V VDIFF = 0V Previous cycle Next cycle 1 cycle T/7 T/7 T/7 T/7 T/7 T/7 T/7 1 0 0 1 ENAB ... RxIN[2] 0 1 1 ENAB RxIN[1] 0 1 1 0 0 1 1 0 0 1 1 0 0 ... RxIN[0] 0 1 1 0 0 1 1 0 0 1 1 0 0 ... VSYNC HSYNC VSYNC HSYNC Figure 3. FPD-Link Receiver IDD Pattern Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 3 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com DC Electrical Characteristics RSDS Output (CLKP/N, xyP/N; x = R, G, B; y = 0, 1, 2), VDD = 2.25V to 2.75V (Unless otherwise specified) Symbol Parameter Conditions |VODRSDS| Differential Output Voltage Typ. VOSRSDS Offset Voltage Min RL = 100Ω IPI = 100 µA Typ Max Units 200 (Figure 4) mV 1.2 V VOUTN Single Ended V ODRSDS -200 mV +200 mV V VOUTP | OSRSDS GND Differential +200 mV GND (VOUTP)-(VOUTN) -200 mV Figure 4. RSDS Output Waveforms: Single Ended vs Differential 1000 VOD vs. RPI 900 VOD (mV) 800 700 VDD = 2.75V 600 500 VDD = 2.5V 400 300 VDD = 2.25V 200 4 6 8 10 12 14 16 18 RPI (k:) Figure 5. Typical RSDS VOD vs RPI Response Curve 4 Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 DC Electrical Characteristics Schmitt Trigger Symbol Parameter VH Hysteresis Voltage VT− VT+ IINHYS Conditions Min Typ VT+ – VT− Max Units 0.4 V Hysteresis Low Threshold Voltage 1.2 V Hysteresis High Threshold Voltage 1.6 V VIN = VDD Input Current 20 −20 VIN = VSS VDD µA 0 µA VO VT+ VI VH VT- VSS VDD VH = VT+ - VT- VH VO VI VSS VT- VT+ Figure 6. Hysteresis Definition AC Electrical Characteristics LVDS Data Input RT = 100Ω, IPI = 100 µA, f = 85 MHz (Unless otherwise specified) TA = 0°C to 70°C, VDD = 2.5V ±0.25V, IPI = 100 µA (Unless otherwise specified) Symbol Parameter Conditions FRXCLK RxCLK Frequency (LVDS) RPLLS FPD-Link Receiver Phase Lock Loop Wake-Up Time RMS RxIN Strobe Margin (1) and (Figure 7) (1) F = 85 MHz Min Max Units 25 85 MHz 10 ms 400 ps Receiver Strobe Margin is defined as the valid data sampling region at the receiver inputs. RSM (leftside) RSM (rightside) RxIN[3:0] Vdiff = 0V SW RSPOSmin Ideal Tx Pulse Position RSPOSmax Ideal Rx Strobe Position Ideal Tx Pulse Position Acronyms: RSM Receiver Strobe Margin RSPOS Receiver Strobe Position SW Strobe Width Definitions: SW Setup and Hold Time (Internal data sampling window) Figure 7. FPD-Link Receiver Input Skew Margin Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 5 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com Table 1. Ring Oscillator Characteristics RT = 100Ω, IPI = 100 µA, f = 85 MHz (Unless otherwise specified) Symbol Parameter Ring Oscillator Clock Frequency Conditions Min Typ R = 14.5KΩ; VDD= 2.5V FPD87208AXA RESOSC 40 23 PI 22 RESOSC 21 RSDS2 Max Units MHz R = 14.5 k: Figure 8. Application diagram of Ring Oscillator Case A 0.9 VDD VDD RPLLS RxCLK SSCKO (SSCTR=H) Case B 0.9 VDD VDD RPLLS RxCLK INVALID SSCKO (SSCTR=H) Figure 9. FPD-Link Receiver Phase Lock Loop Wake-Up Time 6 Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 RCOP(T) RxCLKIN VDIFF = 0V VDIFF = 0V Previous cycle Next cycle 1 cycle T/7 T/7 T/7 RxIN[2] B[4] B[3] B[2] ENAB RxIN[1] G[3] G[2] G[1] B[1] B[0] RxIN[0] R[2] R[1] R[0] G[0] R[5] VSYNC HSYNC T/7 T/7 T/7 T/7 B[5] B[4] B[3] B[2] ENAB VSYNC G[5] G[4] G[3] G[2] G[1] B[1] B[0] R[4] R[3] R[2] R[1] R[0] G[0] R[5] Note: R/G/B[7]s are MSBs and R/G/B[0]s are LSBs Figure 10. FPD-Link Receiver Input Data Mapping Table 2. Output Timing RT = 100Ω, IPI = 100 µA, f = 85 MHz (Unless otherwise specified) Symbol Parameter Conditions RCHP RSDS Clock (RSCK) High Period CL(RSDS) = 5 pF RCLP RSDS Clock (RSCK) Low Period CL(RSDS) = 5 pF SPSTU STH Rising to RSCK Falling SPHLD STH Falling to RSCK Falling RSTU (1) RHLD (1) (1) Min CL(TTL) = 15 pF RSDS Setup to Falling or Rising Edge of RSCK RSDS Hold from Falling or Rising Edge of RSCK Typ Max Units 5.8 ns 5.8 ns 4.0 ns 4.0 ns CL(RSDS) = 5 pF RSDS[2:0]=[011] 3.3 ns 2.1 ns Refer to the table “RSDS Setup and Hold Time with Data Skew Control Values” for each skew control. Table 3. RSDS Setup and Hold Time with Data Skew Control Values—Reference Only (RxCLKP/N = 85 MHz, RT = 100Ω, IPI = 100 µA, VDD = 2.5V; Duty Clock = 50%/50%, ±2%; 25°C) (1) RSDS[2:0] (1) Setup Time (RSTU, nS) Min Typ Hold Time (RHLD, nS) Max Min Typ 000 1.83 3.61 001 2.33 3.09 010 2.83 2.61 011 3.31 2.10 100 3.85 1.55 101 4.34 1.03 110 4.81 0.53 111 5.33 0.01 Units Max ns Typical values on this table are measured under Static and Steady state conditions which may not be reflective of its performance in the end application. Table 4. RSDS and TTL Output Tr/Tf Symbol Parameter Conditions Min Typ Max Units RSTr/RSTf RSDS Output Rising/Falling Time (All RSDS Outputs) CL(RSDS) = 5 pF 1.5 ns TTL Tr/Tf TTL Output Rising and Falling Time CL = 15 pF (20%–80%) 2.0 ns Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 7 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com RSTr RSTf +120 mV RSDS Out -120 mV -120 mV Tr Tf 90% 90% TTL Out 10% 10% RCHP RSCKP/N RCLP 0V 0V 0V 0V (differential RSDS signal) SPSTU 2.0V SPHLD 2.0V STH (single ended TTL signal) RSTU RSR[2:0]P/N RSG[2:0]P/N RSB[2:0]P/N Invalid Data RHLD RSTU EVEN RHLD ODD 1st Pixel Data (Typically IRSDS = 20 x IPI) RSDS P(ositive) Output CL(RSDS) = 5 pF PI RT = 100: RSCKP/N RSR[2:0]P/N RSG[2:0]P/N RSB[2:0]P/N RSDS N(egative) Output TTLOUT TTL Outputs CL(TTL) IPI = 100 PA (Source Current) (Typically with RPI = 12.3 k:) Figure 11. RSDS and TTL Output Timing Diagram 8 Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 RSCKP/N 0V 0V SPSTU SPHLD 0V RSTU RSTU RHLD RHLD 2.0V STH 2.0V RSR[0]P/N R0 R1 R0 R1 R0 R1 RSR[1]P/N R2 R3 R2 R3 R2 R3 RSR[2]P/N R4 R5 R4 R5 R4 R5 RSG[0]P/N G 0 G 1 G 0 G 1 G 0 G 1 RSG[1]P/N G 2 G 3 G 2 G 3 G 2 G 3 RSG[2]P/N G 4 G 5 G 4 G 5 G 4 G 5 RSB[0]P/N B0 B1 B0 B1 B0 B1 RSB[1]P/N B2 B3 B2 B3 B2 B3 RSB[2]P/N B4 B5 B4 B5 B4 B5 1st Data 2nd Data 3rd Data Note: RSCKP/N, RSR[2:0]P/N, RSG[2:0]P/N and RSB[2:0]P/N are differential outputs, STH is a single ended TTL output. Figure 12. RSDS Output Data Mapping Table 5. Input Signal Timing—Reference Only Signal Item Symbol Clock Frequency 1/Tclk F Total Tv Vertical Timing Active Total Tvact Th Horizontal Timing Active Thact XGA (1024 x 768) WXGA1 (1280 x 768) WXGA2 (1280 x 800) WXGA3 (1280 x 854) Unit Typ 65 82 68 69 MHz Min 774 774 806 860 Typ 806 806 816 880 Max 1024 1024 1024 1024 Min - - - 854 Typ 768 768 800 Max - - - - Min 1078 1334 1334 1334 Typ 1344 1688 1408 1408 Max 2047 2047 2047 2047 Min 100 100 100 100 Typ 1024 1280 1280 1280 Max - - - - Th Tclk Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 9 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com Output Timing—TTL Table 6. Display Resolution Selection Control DTM1 DTM0 Display Mode Resolution 0 0 WXGA1 1280 x 768 0 1 WXGA2 1280 x 800 1 0 XGA 1024 x 768 1 1 WXGA3 1280 x 854 Table 7. TTL Timing Selection Control: RO[2:0] XGA (1) RO[2:0] 000 001 010 011 100 101 110 111 Unit T1 2 2 2 2 2 2 2 TCLK T2 1 1 1 1 1 1 1 TCLK T3 1030 1030 1030 1030 1030 1030 1030 TCLK T4 16 24 16 24 32 48 42 TCLK T5 912 960 960 912 842 912 802 TCLK T5′ 782 830 830 782 712 782 672 TCLK T6 200 160 160 130 220 220 260 T6′ 130 130 130 130 130 130 130 T7 1038 1056 1056 976 874 976 834 T8 650 650 650 650 680 680 725 TCLK TEST MODE TCLK TCLK TCLK T9 348 348 348 348 348 348 348 TCLK T10 1 1 1 1 1 1 1 HLINE T11 348 348 348 348 348 348 348 TCLK HLINE T12 1 1 1 1 1 1 1 T13 (1) 567 567 567 567 567 567 567 TCLK T14 (1) 2 2 2 2 2 2 2 HLINE Timing based on first occurrence of STH. WXGA RO[2:0] 000 001 010 011 100 101 110 T1 2 2 2 2 2 2 2 111 TCLK Unit T2 1 1 1 1 1 1 1 TCLK T3 1286 1286 1286 1286 1286 1286 1286 TCLK T4 16 24 16 24 32 48 42 TCLK T5 1168 1216 1216 1168 1098 1168 1058 TCLK T5′ 1038 1086 1086 1038 968 1038 928 TCLK T6 200 160 160 130 220 220 260 TCLK T6′ 130 130 130 130 130 130 130 T7 1294 1312 1312 1232 1130 1232 1090 T8 650 650 650 650 680 680 725 TCLK T9 348 348 348 348 348 348 348 TCLK HLINE TEST MODE TCLK TCLK T10 1 1 1 1 1 1 1 T11 348 348 348 348 348 348 348 TCLK T12 1 1 1 1 1 1 1 HLINE T13 (1) 567 567 567 567 567 567 567 TCLK T14 (1) 2 2 2 2 2 2 2 HLINE (1) Timing based on first occurrence of STH. 10 Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 N: 768 (XGA) 768/800/854 (WXGA) 1 2 3 4 5 6 Y. 595 N | DE N(H Line) | 595 (RSDS) RGBP/N | (RSDS) | | CLKP/N | (embedded in LVDS RxIN) || REV (1HRVS) || | STH | REV (2HRVS) | | | | TP | CPV | | | STV OE1 OE2 Figure 13. TTL Output Timing Diagram Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 11 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com DE (Embedded in LVDS RxIN) CLKP/N t1 RGBP/N (RSDS) t2 STH t3 TP t4 t5 OE1 t6 t5' OE2 t6' t7 | t8 CPV t9 t10 | STV* | t11 REV (1HRVS) t12 t13 REV* (2HRVS) t14 * Timing based on first occurrence of STH signal to the left of the measured output. Figure 14. TTL Output Timing Diagram (Continued) 12 Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 Output Timing—Power-Up Sequence (reference only) Max. 10 ms LVDS Rx PLL Wake-up Time VDD LVDS IN Control Signals RESET 1st 2nd 5th 6th Frame STV OE1 OE Signal Normal Out- OE2 OE Signal Normal Out- Invalid RGB Out Data Signal Normal Out- Figure 15. Power-Up Sequence RSG[2]N RSG[1]P RSG[1]N RSG[0]P RSG[0]N RSCLKP RSCLKN VSSIO 39 38 37 36 35 34 33 RSB[0]P 43 40 RSB[1]N 44 RSB[0]N RSB[1]P 45 RSG[2]P RSB[2]N 46 41 RSB[2]P 47 42 VDDIO 48 Connection Diagram VSSIO 49 32 VDDIO STH 50 31 RSR[2]P TP 51 30 RSR[2]N 64 PIN TQFP FPD87208AXA REV 52 29 RSR[1]P STV 53 28 RSR[1]N RSR[0]P CPV 54 27 OE1 55 26 RSR[0]N OE2 56 25 VSSIO POLSET 57 24 VDDIO DTM0 58 23 PI DTM1 59 22 RESOSC RO0 60 21 RSDS2 RO1 61 20 RSDS1 RSDS0 9 10 11 12 13 14 15 16 IDREV BIST VDDA VSSA VSSP VDDIO 8 RXIN[2]P RXCLKP 7 RXCLKN 6 RXIN[1]P RXIN[2]N 5 RXIN[1]N 3 VSSIO 4 17 RXIN[0]P 64 RXIN[0]N RSTZ VSS 1 18 2 19 63 VSSD 62 VDDD RO2 VDD Figure 16. Pinout Assignment Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 13 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com Pin Descriptions Table 8. LVDS Rx Inputs Pin Count Type RxIN[0]N/P 2 LVDSI LVDS Rx Data Differential Input Pairs RxIN[1]N/P 2 LVDSI LVDS Rx Data Differential Input Pairs RxIN[2]N/P 2 LVDSI LVDS Rx Data Differential Input Pairs RxCLKN/P 2 LVDSI LVDS Rx Clock Differential Input Pairs Sub-Total Pin Count 8 Symbol Function Table 9. RSDS Tx Outputs Pin Count Type R [2:0]P/N 6 RSO Red Reduced Swing Differential Outputs to Column Drivers G [2:0]P/N 6 RSO Green Reduced Swing Differential Outputs to Column Drivers B [2:0]P/N 6 RSO Blue Reduced Swing Differential Outputs to Column Drivers CLKP/N 2 RSO Clock Reduced Swing Differential Outputs to Column Drivers Sub-Total Pin Count 20 Symbol Function Table 10. RSDS Tx Bias Reference Input Symbol Pin Count PI 1 Sub-Total Pin Count 1 Type Function Current Reference for RSDS Tx Output (1.23V) Table 11. CMOS Input (2.75V Maximum) Pin Count Type RSDS[2:0] 3 I RSDS Skew/Timing Control RO[2:0] 3 I Display Timing Selection POLSET 1 I 0: Two Line Inversion; 1: One Line Inversion DTM[1:0] 2 I Display Mode Selection (XGA, WXGA1, WXGA2, WXGA3) RESOSC 1 AI 1 PU BIST 1 I RESETZ 1 Schmitt I Sub-Total Pin Count 13 Symbol IDREV 14 Function RC oscillator reference for BIST function. 14.5 kΩ = ∼40 MHz IDREV = HIGH (default, pull high): Output data is 3F during vertical blanking. IDREV = LOW: Output data is 00 during vertical blanking. BIST Control Function (Active High), tied to ground for norm mode TCON Reset (Active Low) Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 OBSOLETE FPD87208 www.ti.com SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 Table 12. CMOS Outputs (2.75V Maximum) Pin Count Type STV 1 TO Row Driver Start Pulse CPV 1 TO Row Driver Shift Clock TP 1 TO Line Latch Signal Output to Column Drivers STH 1 TO Horizontal Start Signal Output to Column Drivers REV 1 TO Alternative Signal Output for each 1 or 2 Horizontal Line to Column Drivers OE1 1 TO Control TFT Gate Pulse Width to Row Drivers OE2 1 TO Control TFT Gate Pulse Width to Row Drivers Sub-Total Pin Count 7 Symbol Function Table 13. Power Supply Symbol Pin Count Type Function VDD 1 P Digital Power for Logic Core VSS 1 G Digital Ground for Logic Core VDDIO 4 P Digital I/O and RSDS Power VSSIO 4 G Digital I/O and RSDS Ground VDDA 1 P FPD Receiver—Power for Analog VDDD 1 P FPD Receiver—Power for Digital VSSD 1 G FPD Receiver—Ground for Digital VSSP 1 G FPD Receiver—Ground for PLL VSSA 1 G FPD Receiver—Ground for Analog Sub-Total Pin Count 15 Total Pin Count 64 System Interface = 8 RSDS Tx Out = 20 RSDS Tx Bias Reference Input = 1 CMOS Input (control) = 13 CMOS Output = 7 Power Supply = 15 Pin Types AI -Analog Input I -Input (LVTTL) TO -TTL Output (LVTTL) LVDSI -Low Voltage Differential Signal Input RSO -Reduced Swing Differential Output P -Power G -Ground PD -Pull Down PU -Pull Up Schmitt I -Schmitt Triggered Input Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 15 OBSOLETE FPD87208 SNOSAC5C – APRIL 2004 – REVISED APRIL 2013 www.ti.com REVISION HISTORY Changes from Revision B (April 2013) to Revision C • 16 Page Changed layout of National Data Sheet to TI format .......................................................................................................... 15 Submit Documentation Feedback Copyright © 2004–2013, Texas Instruments Incorporated Product Folder Links: FPD87208 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as “components”) are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed. TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguards. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI. Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions. Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications. In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms. No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use. Only those TI components which TI has specifically designated as military grade or “enhanced plastic” are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949. Products Applications Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Amplifiers amplifier.ti.com Communications and Telecom www.ti.com/communications Data Converters dataconverter.ti.com Computers and Peripherals www.ti.com/computers DLP® Products www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com Energy and Lighting www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video RFID www.ti-rfid.com OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com Wireless Connectivity www.ti.com/wirelessconnectivity Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated

![6.012 Microelectronic Devices and Circuits [ ]](http://s2.studylib.net/store/data/013591838_1-336ca0e62c7ed423de1069d825a1e4e1-300x300.png)