Smart Rectification Benefits Half

advertisement

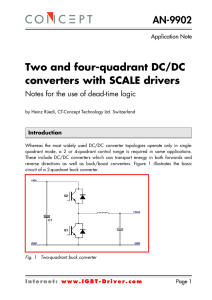

Smart Rectification Benefits Half-Bridge Converters By Jess Brown, Power IC Market Development Manager, Vishay Siliconix, Bracknell, Berks, United Kingdom MOSFET gate-drive signals derived from predictable effects or real-time feedback can enhance the synchronous rectification of half-bridge converters in power-supply applications. T result, the half-bridge converter is emerging as the topology of choice for eighth and sixteenth bricks. Along with a reduction in physical size and an increase in power density, there is also an increasing number of features being added to the dc-to-dc converters that are required from a system level. These features include prebias startup, tracking, controlled startup and controlled shutdown capabilities. The half-bridge format also has inherent difficulties from an applications point of view that need to be addressed to meet the efficiency and power-density requirements for these converters. For example, there are intrinsic problems when driving synchronous MOSFETs in half-bridge converters due to the difficulty of producing the correct drive signals during dwell time and also predicting when the primary MOSFETs turn on and off. he half-bridge converter has been in existence for several years, but these days, it is enjoying renewed interest due to the development of eighth-brick and sixteenth-brick dc-dc converters. In the past, the half-bridge topology was considered for half and quarter bricks, especially at relatively low power levels. As increasing power density in these half and quarter bricks leads to higher power levels (Table 1), it becomes more and more difficult to implement the half-bridge topology efficiently in these converters (Table 2). However, the emergence of eighth and sixteenth bricks has resulted in a new demand for the half-bridge converter, since the power levels in these packages are more in tune with those at which the half-bridge topology excels. As a Brick Size Power Level (W) Full < 700 Half < 350 Quarter < 200 Eighth < 100 Half-Bridge DC-DC Converter The half-bridge dc-to-dc converter configuration consists of two large, equal capacitors connected in series across the dc input, providing a constant potential of one-half VIN at their junction (Fig. 1).[1] The MOSFET switches SW1 and SW2 are turned on alternately and are subjected to a voltage stress equal to that of the input voltage, rather than twice the input voltage that is usually the case in push-pull and forward converters. Also, due to the capacitors providing a mid-voltage point, the transformer sees a positive and negative voltage during switching. This results in twice the desired peak flux value of the core, because the transformer core is operated in the first and third quadrant of the B-H loop and experiences twice the flux excursion of a similar forward converter core. This is an advantage of the half-bridge topology over that of double-ended forward topologies, in that the halfbridge primary transformer winding has half the turns for the same input voltage and power. This is because the Sixteenth < 50 Table 1. Typical values of power levels for different brick sizes. Topology Common Characteristics Power Level (W) Maximum Duty Cycle 5 to 50 < 0.5 10 to 250 < 0.5 Flyback Forward Resonant Reset Forward Active 10 to 250 < 0.5 Clamp Reset Push-Pull 15 to 150 < 1.0 Half-Bridge 50 to 200 < 1.0 Full-Bridge 200 to 2000 < 1.0 Table 2. Typical values of power levels for various topologies. Power Electronics Technology March 2006 24 www.powerelectronics.com HALF-BRIDGE CONVERTER Isolation VIN Error amplifier 2ND SW1 SW1 C ½ VIN Si9122 SW2 C 2ND SW2 GND Isolation Synchronous drivers Interface Fig. 1. The half-bridge dc-dc converter topology allows for a smaller transformer than double-ended forward topologies require, but the secondary MOSFET switching must be carefully managed. POWER MODULES forward converter transformer must sustain the full supply voltage, compared to half that voltage for the half-bridge transformer. Another benefit of half-bridge converters is the lower winding costs and proximity effect losses. Proximity effect losses occur when eddy currents are induced in one winding layer by currents in adjacent layers. These losses increase significantly with the number of layers. Because the half-bridge converter has fewer turns than the forward topology, it probably will have fewer layers and, thus, lower proximity effect losses. Another significant advantage of the half-bridge over the double-ended forward converter is that the half-bridge secondary produces a full-wave output rather than a half-wave output. Thus, the square-wave frequency in the half-bridge converter is twice that of the forward converter, and the associated output inductor and capacitor can be smaller. With half-bridge converters, the synchronous MOSFETs are normally on, and are only turned off when one of the primary MOSFETs is turned on. However, there is no inherent way of providing the drive signals for the designer to control the secondary synchronous MOSFETs during dwell time. There is no information readily available that predicts when the primary MOSFETs are about to turn on and enable the secondary-side MOSFETs to be turned off, thus ensuring neither are on at the same time to prevent shoot-through. And, since the secondary-side MOSFETs are normally on, application circuits must be able to handle startup and shutdown. If not managed correctly during startup and www.powerelectronics.com for High Performance Applications Courtesy: AIRBUS Standard and Custom Power Modules from APT offer the best solution for size reduction and enchanced performance. USA Phone: (541) 382-8028 www.advancedpower.com 25 Europe Phone: +33 55792 1515 Power Electronics Technology March 2006 HALF-BRIDGE CONVERTER shutdown, the nature of synchronous MOSFETs Enables internal circuitry being inherently on can CUVLO + IBIAS VIN cause undesirable conVIN Preregulator 3.55 V ditions such as ringing, Output A negative voltage levels 2.5 V ISD and disturbances on the V Hold off UVLO + BG 4.45 V output. 1.225 V Shutdown Prebias is defined as a Driver startup PGND and powerVIN voltage that is present at VREF x1 En down control the output of the convertOutput B + Ref_rdy er before the converter is ISD Hold off switched on. This prebias 1.1 V can be present for several + Ref_Low Shutdown 2.5 V reasons. The converter OVP input may be hot-swapped or 245 mV + OVP 1.47 V there could be a forward Input A Error amp + Power-down path between this output inputs detection and another output. The Error amp converter could be used in Input B Ref_rdy output a redundant power-supply system (N+1), a parallel CPD RPD RDEL GND system or a battery backFig. 2. The SiP11203 intelligent driver integrates several functions needed to meet the requirements for imple- up system, to mention a few, where output voltages menting half-bridge converters. are already present. The issue with a prebias is that if any converter has synchronous rectification, it would be possible to discharge the output during startup. That is, the synchronous MOSFETs could be on during startup before the converter has started to supply power, thus providing a discharge path to ground through the output inductor. This results in negative current flow in the output inductor, oscillation problems and negative voltage spikes at the output. It is necessary for the output voltage to charge to its required regulation voltage and not to go through any discharge of the output if a prebias exists prior to startup. Soft-start is a feature to prevent component stresses during startup of the converter. In addition, it limits the inrush current at startup and allows a monotonic voltage startup. This is generally applied to the primary-side controller of the converter and inherently deals with the secondary-side MOSFETs. However, this article looks at how the secondaryside MOSFETs can also benefit from a soft-start mechanism in half-bridge converters. Soft-stop is a feature that prevents disturbances on the output and allows a monotonic shutdown of the voltage output. As with soft-start, this is an essential feature in half-bridge converters because leaving the secondary-side MOSFETs to turn off indeterminately can cause negative voltage transients and uncontrollable discharging of the output voltage. VL Secondary-Side MOSFET Drivers Achieving the requirements for prebias, overvoltage protection (OVP), soft-start and soft-stop of the secondary-side Power Electronics Technology March 2006 26 www.powerelectronics.com HALF-BRIDGE CONVERTER Input A Input B Input A (SRL) Pulse transformer VIN Input B (SRH) Fig. 3. The dc supply voltage for the intelligent driver can be derived from the synchronous MOSFET gate-drive signals from the half-bridge converter’s pulse transformer. MOSFETs generally requires a separate application circuit for each function. However, Vishay Siliconix has introduced a single chip that can be configured to address all the issues described previously, as well as incorporating the error amplifier and precision voltage reference required on the secondary side of the half-bridge topology. The block diagram of this integrated circuit (IC) is shown in Fig. 2. The signals required to drive the synchronous MOSFETs (Si7108DN) are obtained from the primary-side half-bridge controller (Si9122). By using the primary-side controller, this allows the drive signals to be present even during dwell time. In addition, because the primary controller knows when the primary MOSFETs (Si7810DN) will be turned on, it can provide a signal to turn off the secondary MOSFETs before the primary ones turn on. The VIN voltage can be derived from any of the usual methods, such as an extra winding on the power transformer or from the output inductor. However, since a pulse transformer is required to transmit the secondary MOSFET gate signals across the isolation barrier, it is possible to generate the VIN from these gate signals (Fig. 3). During startup of the converter and intelligent driver, the MOSFET drivers initially need to be disabled, since the gatedriver voltage could be at an indeterminable level, causing extra losses and even failures in the synchronous MOSFETs. Therefore, the SiP11203 MOSFET drivers are disabled until VL is at 90% of its final value. However, if the output drivers were left floating until the main drivers were enabled, the high dV/dT rate during the transition of the current from the body diodes of second SW1 and second SW2 (Fig. 1) could result in spurious turn-on of the MOSFET. Thus, before the main drivers are enabled (VL < 90%), the Input A and Input B drive paths are reversed and inverted (Fig. 4), and there is a device on each output to pull the relevant gate-driver outputs low at the appropriate time. Once VL is established, the small inverting driver is switched out of the path, and as a result, the driver circuit will effectively www.powerelectronics.com For superior solutions: Inductors � � � � High current-handling capability High temperature range up to 150 °C Very compact designs Wide range of standard products More information at www.epcos.com APEC Dallas, Texas, USA March 19 to 23, 2006 Stand 137, 138 Power Electronics Technology just everywhere … HALF-BRIDGE CONVERTER that brings the synchronous MOSFET into the VIN power path over several cycles. The soft-start method, as shown in Fig. time 6, prevents disturbances Output A Input A of the output voltage. The Holds Output B low soft-start period is set by Input B Input A an external resistor placed V on RPD. Closed during VIN The Si9122 allows startup the break-before-make (BBM) delay to be set Input B Output B with one resistor (BBM1 time = BBM2 = BBM3 = Holds Output A low Input A BBM4). However, this lacks some flexibility beInput B V cause gate delays can be VIN introduced across the isolation barrier. Therefore, the SiP11203 incorporates a feature that introduces time a rising edge delay, once the device has finished the Fig. 4. During converter startup, the synchronous MOSFET gate-driver outputs of the SiP11203 are reversed and soft-start. For definition inverted to prevent spurious MOSFET switching. of the BBM delays, please see the Si9122 data sheet. Rate of rise determined by V A separate pin (OVP input) is provided in the SiP11203 external VL capacitor to detect overvoltage conditions, which can occur according VL 5V to two separate modes. The first is an overvoltage during the (0.9)VL startup of the device. The second is an overvoltage during Rate of rise determined by normal operation. At startup, an overvoltage condition is rate of rise of VIN 3.5 V defined as the OVP input being 20% greater than the final Internal VREF1 2.5 V value of VREF , which is approximately 1.4 V. VREF If an overvoltage event occurs during startup, the driver 1.225 V outputs are disabled until the external VREF has reached 1.1 Rate of rise determined by external VREF capacitor V, which is 90% of its final value of 1.225 V. As VREF reaches time 1.1 V, the output drivers are released to respond to the input Internal pulses. However, if the overvoltage set point (VREF + 20%) is logic VREF released to rise circuits reached during normal operating conditions, or after VREF has enabled reached 90% of its final value, the OVP comparator is latched Fig. 5. Soft-start parameters of the SiP11203 are programmable with and the output drivers are forced to the on condition. The external components. external VREF is then discharged to 20% of its normal value. The output drivers will stay on for the SiP11203 (and off for hold the driver outputs low until the VL voltage level has SiP11204) until VREF is discharged to 245 mV and the voltage reached 90% of its final value. at the OVP input pin is below 1.1 V. After the fault condition Once VL has reached 90% of its final value, the external has cleared, the output drivers are released and the device VREF also is released and able to rise according to the value experiences a soft-start condition. of the VREF capacitor (Fig. 5). The rate of the rise of VL is To prevent the synchronous MOSFETs from staying on determined by the external VL capacitor, which is driven when the input pulses from Input A and Input B cease, the by a 20-mA current from the preregulator. This allows the SiP11203 has a function that discharges the gates of the designer to control the power-up period of the SiP11203. synchronous MOSFETs before the bias supply to the IC If the secondary-side MOSFETs are disabled, there will disappears. The inputs are monitored and, when there is no be a situation in which the body drain diodes are conducting activity on INA and INB after a certain time, the main drivers current rather than the MOSFET channels. By switching in are disconnected and the driver outputs are discharged under the MOSFET channel, the voltage across the device will be power-down control (Fig. 7). reduced considerably, resulting in a disturbance on the output The pull-down current will be a fixed ratio of the current of the converter. Hence, the SiP11203 has a soft-start feature V Power Electronics Technology March 2006 Ramp up of VIN during startup 28 www.powerelectronics.com HALF-BRIDGE CONVERTER Rising edge delay during normal operation. Period set by RDEL. (Note: Can be set to zero.) Rising edge delay reduces during soft-start. Soft-start period set by RDEL. Input A Input A Output A Output A Input B Input B Output B Output B time Soft-start finished Soft-start period Fig. 6. The SiP11203 gate-drive output signals are delayed during soft-start to prevent disturbing the output voltage. These can also compensate for break-before-make switching action discrepancies arising from propagation delays. Shutdown possible to configure the device to prevent the MOSFET drivers from being enabled under a prebias condition (VOUT >1.4 V) at startup. During startup, the OVPIN signal could be connected directly to the output, allowing the SiP11203 to detect a prebias voltage greater than 1.4 V as an overvoltage condition, turning off the MOSFET drivers and preventing any discharge of the output. Once the VREF on the SiP11203 is established, the OVPIN would then need to be connected to the output via an external resistive divider, to allow for overvoltage protection as per normal operation. PETech Restart VIN VL Input A/B 2.5 V CPD References 1. Brown, Jess; Davies, Richard; Williams, Dilwyn; and Bernacchi, Jerry. “High-Efficiency Half-Bridge DC-to-DC Converters with Secondary Synchronous Rectification,” PCIM 2001, Nuremberg, Germany. 2. Si9122 data sheet, www.vishay.com/docs/71815/71815. pdf. VREF Output A/B time Fig. 7. The shutdown sequence of the SiP11203 prevents the synchronous MOSFETs of a half-bridge converter from discharging a prebiased output when supplied power is removed. set by an external resistor such that the discharge time can be a fixed number of pulses at the normal operating frequency. Without this function, no activity on the inputs of INA and INB—due to the primary-side shutting down—would result in the synchronous MOSFETs staying on. Allowing the MOSFETs to remain on once the primary controller has been shut down can cause the output to be discharged, and negative spikes can occur when the synchronous MOSFETs finally turn off. Since the SiP11203 has a separate overvoltage pin, it is Power Electronics Technology March 2006 30 www.powerelectronics.com