Behavioural Modelling and Simulation for the design of mixed and

advertisement

Contents

• Introduction

Behavioural Modelling and Simulation

for the design of mixed and

• Electrical simulators

• CAD of mixed circuits

• Behavioural Modelling

multi-technological systems

• VHDL-AMS language

VHDL-AMS language

• Examples

• Conclusions

H.Lévi

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

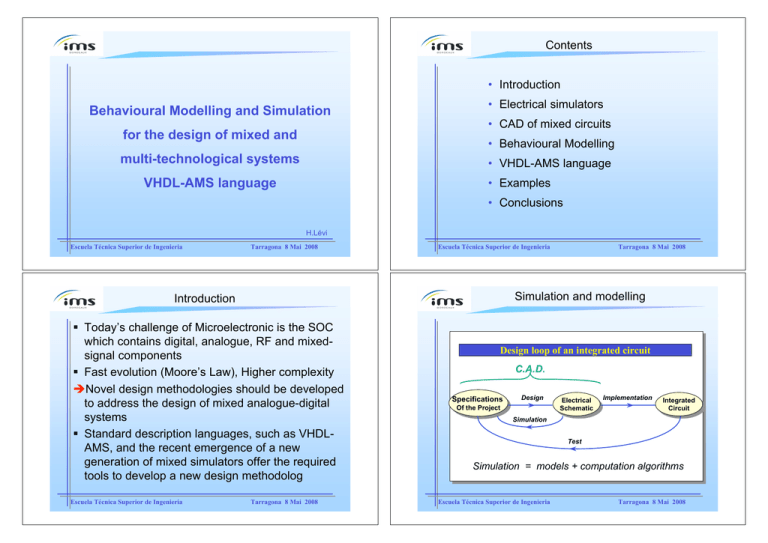

Simulation and modelling

Introduction

! Today’s challenge of Microelectronic is the SOC

which contains digital, analogue, RF and mixedsignal components

! Fast evolution (Moore’s Law), Higher complexity

"Novel design methodologies should be developed

to address the design of mixed analogue-digital

systems

! Standard description languages, such as VHDLAMS, and the recent emergence of a new

generation of mixed simulators offer the required

tools to develop a new design methodolog

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Tarragona 8 Mai 2008

Design loop of an integrated circuit

C.A.D.

Specifications

Specifications

Design

Of

Ofthe

theProject

Project

Electrical

Electrical

Schematic

Schematic

Implementation

Integrated

Integrated

Circuit

Circuit

Simulation

Test

Simulation = models + computation algorithms

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Models and simulators

Simulation and modelling

Real System

Systems

Calculator

Simplifying hypothesis

Modelling

µ-processor

Simulation

Model

Functional blocks

ALU,

memories, etc.

Logical gates

NAND, NOR,

etc.

Electrokinetic

transistors

Maxwell equations

current,

Electrical fields

Simulators

Growing number of components

Models hierarchy

Electrical simulators

Electrical

Behaviour

Physical simulators

Number density

Electrical fields

Process simulators

Diffusion

Implementation

Oxidation

Lithography

Solid physics

atom

Model = Mathematical representation of a physical reality

In a given context

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Electrical simulators

#Analogue Simulators

Tarragona 8 Mai 2008

Analogue / Digital Simulators

# Digital Simulators

#Analogue Simulators

#Digital Simulators

« Continuous-Time »

« Event-Driven »

v(t)

1

0

v1(t)

t

Events detection +

computation of affected signals

Signal affectation

= new event

variable !t

$ Kirchoff’s laws

$ Events’ driven

$ DC, AC, transient analysis

$ Models of components:

· dynamically auto-adjustable !t:

$ Transient analysis

- if dv/dt

then !t

$ Models of components :

- if dv/dt

then !t

" Accurate description of transient

periods

R

S

REG

RAM, ROM, PLA, ...

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

" Reduction of computation time in

nearly-permanent mode

Escuela Técnica Superior de Ingenieria

v2(t)

#

v1(t)

t

v2(t)

t

#

"Sleep of the simulator between

events

"very fast simulation

Tarragona 8 Mai 2008

Examples

# Analogue

# Digital

% SPICE, 1st generation

• SPICE 3F5 (UC Berkeley)

% 2nd

Challenges

generation

• SPECTRE (Cadence)

• VERILOG-XL

(Cadence)

• MODELSIM (Mentor

Graphics)

• Pentium 4 has 42 millions of transistors

– Development of mixed ASICs

• 25% in 2001 and 80% in 2008

– Integration of System on Chip (SoC)

• RF blocks, CAN, DSP, Microprocessor, etc.

• ELDO (Anacad / Mentor

Graphics)

Escuela Técnica Superior de Ingenieria

• Evolution of integrated circuits

– Miniaturization

• Design context of integrated systems

– Complexity/Density

– Difficulties of simulation (CPU time, convergence)

% Creation of hardware description languages (HDL)

Tarragona 8 Mai 2008

SoC Example

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

SoC-AMS Example

ST-Microelectronics

Satellite RF Tuner

CMOS 0,18 µm

RF front-end

Complex convertors

DSP and Memories

[ J.P. Morin, Mixed-Signal SoC Design Challenges & Emerging EDA Solutions,

FDL’01, Lyon, Sept. 2001 ]

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

To an unified design environment

Solutions

# « Behavioural » modelling

# Mixed simulators

– Appeared to be compatible with mixed languages like

VHDL-AMS

– Association of a core of analogue simulation and of a

core of digital simulation

Analogue simulator

synchronisation

– Description of inputs/outputs behaviours of a block

without studying its intern architecture

• 1st step towards complexity management

– High level model, than transistor level

• Introduction of hierarchical levels between transistor and

system levels

Digital simulator

– Reuse of the same model for a circuit family

• gain of time

Analogue part

# Modelling languages

Digital part

CAN

– VHDL-AMS : 1999 - IEEE 1076.1 Norm

VHDL + description of analogue and mixed circuits

– Verilog-AMS : Normalisation OVI currently

CNA

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Design methodology

Functional / Behavioural model

# Functional model

Usual analogue design

TRANSFER

e1

System specifications

Ideal

Function

e2

s

ve1

ve2

ie2

B

O

T

T

O

M

Simulation

# Behavioural model

ie1

Tarragona 8 Mai 2008

INPUT

TRANSFER

Input

Characteristic

Function

+

Limits

Escuela Técnica Superior de Ingenieria

OUTPUT

vt

Output

Characteristic

Tarragona 8 Mai 2008

is

vs

U

P

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

SOC-AMS design flow

Design methodology

Hierarchical design

System specifications

T

O

P

D

O

W

N

Functional

model

Functional

model

Behavioural

model

Behavioural

model

Functional

model

Behavioural

model

B

O

T

T

O

M

U

P

Escuela Técnica Superior de Ingenieria

Behavioural / Functional model

specifications

Tarragona 8 Mai 2008

Hierarchical Design Flow for mixed circuits

Architecture – Functional blocks description

system

Top-Down

Bottom-Up

Circuit – Transistor description

circuit

layout

Layout description

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Hardware description languages

IEEE 1076 norm : VHDL

G&H",<4&-0$)*5&(52&.*

("I2&("+"0.

Standard language of digital circuit description

E'1<:'F0*1#$4"

7"-&4."(*.($048"(*)"%")

/9:;<,"45(&1.&'06

!"#$%&'($)*+',")*$0$)'/&012.3'2.12.*,"45(&1.&'06

=0$)'-*4>0.#"4&4

/5&(52&.*45#"+$.&5*4&?&0-6

@>0.#"4&4

/,&-&.$)*A)'5B46

:&-&.$)

)&A($(>

C0."-($.&'0*&0.'*."5#0')'->

<,"1"0,"0.*

0".)&4.

# Result of the need of normalisation (portability and

development of libraries)

!'..'+

<21*1#$4"

!"#$%&'($)*+',")*,&-&.$)

/&012.3'2.12.*,"45(&1.&'06

# Modular language well-adapted for Top-down design

# Modelling and synthesis tool

=0$)')&A($(>

Automatic

Automatic

synthesis

synthesis

D)$5"*$0,*('2."

E$1"*'2.

Escuela Técnica Superior de Ingenieria

behavioural

behavioural

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Data

Dataflow

flow

structural

structural

Tarragona 8 Mai 2008

VHDL for Analogue and Mixed Signals

Need to extent VHDL to analogue part

# Extension of VHDL : description and simulation of analogue,

digital, and mixed-signal circuits and systems.

# Digital and analogue mixed systems

# Submicron technologies effects (interconnections)

# Behavioural description of continuous-time and

discrete-time systems

$Modelling by a system of differential and algebraic equations:

F(x, dx/dt, t) = 0

$ New object class for variables (ports and analogue signals)

$Instructions of conversion/synchronisation

digital <-> analogue

# Systems with several fields (mechanic, electronic,

fluidic, magnetic...)

#

Design with a global view improving

the communication between the

different engineering experts

Several modelling levels

$Physical models (SPICE)

$Functional models

$Behavioural models

Reduce the design time

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Model library development

VHDL-AMS language

Description

Description and

and modelling

modelling

–– mixed

systems

mixed systems (analogue/digital)

(analogue/digital)

–– Multi-technological

Multi-technological systems

systems(thermal,

(thermal,

mechanic,

hydraulic...)

mechanic, hydraulic...)

Advantages

Advantages ::

$

$ Huge

Hugedecrease

decreaseof

ofsimulation

simulationtime

time

$

Library

creation

(Re-use

concept)

$ Library creation (Re-use concept)

$

$ Parametric

Parametric models

models allowing

allowing design

design with

with an

an hierarchical

hierarchical

approach

approach

$

$ Possibilities

Possibilities of

of models

models with

with several

several complexity

complexity levels

levels

according

according to

toaccuracy

accuracyor

orsimulation

simulation time

timecriterion

criterion

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Tarragona 8 Mai 2008

! New challenges :

! Building of behavioral models

! Creation of model libraries available in the design flow

! Objective :

! Including the libraries in CAD environment to be easily and

naturally used by designers

! Nowadays and in the future, reuse methodologies are

and will be compulsory :

" IP (Intellectual Property) concept : reuse of already designed

blocks

" IP-AMS definition and IP-based design flow

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Structure of a VHDL-AMS model

Source file

ARCHITECTURE

ARCHITECTURE

declarations

declarations; ;

BEGIN

BEGIN

ENTITY

ENTITY

declarations

declarations

generic

genericparameters,

parameters,ports

ports; ;

END

ENDENTITY

ENTITY; ;

Behavioural

Behavioural

Description

Description

or

or

Structural

Structural

Description

Description

ENTITY

ENTITY

ENTITY circuit1

circuit1

generic

generic(( gain

gain ::real

real :=

:=10.0

10.0,,

delay

delay ::time

time :=

:=1ms

1ms));;

Digital

Mode

Port/Signal

port

port((

END

END; ;

Extern view of the model

Intern view of the model

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Generic

Parameters

Type

Default

Value

Type

signal

signal

s1

s1::in

inbit

bit,,

s2

s2::out

outreal

real;;

terminal

terminal

t1,

t1,t2,

t2,tout

tout::electrical

electrical));;

END

ENDENTITY

ENTITYcircuit1

circuit1;;

Analogue

Port

Nature

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

ARCHITECTURE

TERMINAL

ARCHITECTURE

ARCHITECTURE behav

behavOF

OFcircuit1

circuit1IS

IS

# Analogue connexion node

– Continuous time

– Has a NATURE which represents a physical field

(electric, thermal, hydraulic…)

– Associated to 2 types :

$ Analogue type ACROSS (potential)

$ Analogue type THROUGH (flow)

Declarations

constant

constant

constant

constant

kk

::real

real :=

:=10.0

10.0;;

g_dB

g_dB ::real

real :=

:=20.0*log(gain)

20.0*log(gain);;

signal

signal

sig_int

sig_int::bit

bit

quantity

quantity

quantity

quantity

quantity

quantity

vin

across

vin

across iin

iin through

through t1

t1 to

to t2

t2;;

vout

vout across

across iout

iout through

through tout

toutto

to electrical_ground

electrical_ground;;

vtemp

vtemp::real

real :=

:=0.0

0.0;;

:=

:=‘0’

‘0’;;

Initial Value

(t=0)

BEGIN

BEGIN

terminal

…

…

…

…

…

…

through

across

END

ENDARCHITECTURE

ARCHITECTUREbehav

behav;;

ref

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Instructions

Tarragona 8 Mai 2008

ARCHITECTURE content

QUANTITY

# New object : continuous-time signal

– 3 types

Declarations

ARCHITECTURE

ARCHITECTURE behav

behavOF

OFcircuit1

circuit1IS

IS

$ ACROSS / THROUGH : associated to a terminal

$ FREE : free signal

# Syntax :

quantity vin

across

iin

through

t1

to

t2 ;

quantity vout

across

iout

through

tout

to

electrical_ground ;

quantity vtemp

: real

:= 0.0 ;

BEGIN

BEGIN

Concurrent

ConcurrentInstructions

Instructions

Simultaneous

SimultaneousInstructions

Instructions

t1

tout

Component

ComponentInstantiations

Instantiations

iin

vin

…

…

…

…

…

…

iout

t2

vout

END

ENDARCHITECTURE

ARCHITECTUREbehav

behav;;

Instructions

electrical_ground

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Concurrent Instructions

# Instructions addressed to digital simulator

# Indifferent order

# Execution function of event sensibility

• Signal affectation into the architecture

S <= ‘1’ ;

S <= Vcc after 10ms ;

S1 <= S2 ;

• Process

– Sequential

instructions

– Cyclic,

synchronised

by WAIT

• Break

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Sequential instructions

# Only into a PROCESS or subroutines

$ Signal affectation: sig <= ‘0’ ;

$ Variable affectation: var := ‘0’ ;

$ WAIT Instruction

$ Conditional or selective execution

PROCESS

PROCESS

WAIT

WAITon

on ...

...WAIT

WAITuntil

until ...

...WAIT

WAITfor

for ...

...

sequential

sequentialinstructions

instructions

IF ... THEN ... ELSE ... END IF ;

CASE ... WHEN ... END CASE ;

$ Assert ... Report

END

ENDPROCESS

PROCESS;;

– Synchronize the analogue simulator with the digital simulator

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Simultaneous instructions (1)

# Addressed to the analogue simulator

# Indifferent order

# Evaluated at each time (each point of analogue

simulation)

# Can be implicit or explicit

$ Simple instruction:

Vout == K*Vin1*Vin2 ;

Vout**2 + Vout == K*Vin ;

Vout**2 + Vout - K*Vin == 0.0 ;

$ Conditional instruction:

IF (Vin < -5.0) USE Vout == -5.0 ;

ELSIF (Vin > 5.0) USE Vout == 5.0 ;

ELSE Vout == K*Vin ;

END USE ;

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Component instanciation

# For a structural description

# Use of already modelled components

# Definition of the connections

Component name

Current value of

the parameter

Name : ENTITY circuit1 (behav)

GENERIC MAP ( gain => 10.0e3 , retard => 0ms )

PORT MAP ( s1 => sig_in , s2 => sig_out ,

t1 => tin1, tout => tout ) ;

Simultaneous instructions (2)

# Predefined attributes for derivation and

integration

# Derivation :

– dq/dt $> q’DOT ; q is a quantity

t

– ! q du $> q’INTEG ;

0

# Examples :

i == q’DOT ;

u == L*(i’DOT) ;

vs + tau*(vs’DOT ) == 0.0 ;

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Example 1: the resistance

Resistance Model:

characteristic expression: i == v/r;

where v is an across quantity which represents the voltage

between two terminals and r the value of the resistance

entity resistor is

generic (r:real:=100.0);

port (terminal t1, t2: electrical);

end entity resistor;

architecture simple of resistor is

quantity v across i through t1 to t2;

begin

i == v/r;

end architecture simple;

Current name of

the connection

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Example 3: the diode

Example 2: the capacitance

Capacitance model:

characteristic expression: i == C.d/dt(v) ;

where C is the value of the capacitance

!

Modelling example of an electrical component

Large-signal model

Cd

entity capacitor is

generic (r:real:=1.0E-12);

port (terminal t1, t2: electrical);

end entity capacitor;

p

architecture simple of capacitor is

quantity v across i through t1 to t2;

begin

i == c * v’dot ;

end architecture simple;

m

p

ic

Rs

id

m

id = IS (exp((vd ! RS .id ) / N .VT ) ! 1)

ic =

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

VHDL-AMS model of the diode

Design libraries

Library IEEE, Disciplines;

use Disciplines.electrical_system.all; Importation of declarations

use IEEE.math_real.all;

Entity diode is

generic (ISS, N, VT, TT, CJ0, VJ, RS : real);

port (terminal p, m : electrical) ;

End entity diode

Declarations of quantities

Architecture level_1 of diode is

quantity vd across id, ic through p to m ;

quantity qc : real;

begin

Simultaneous instructions

id == ISS *(exp((vd-RS*id) / N*VT)) - 1.0);

qc == TT*id - 2.0*CJ0*sqrt(VJ**2 - VJ*vd);

ic == qc ’dot;

end architecture level_1;

Escuela Técnica Superior de Ingenieria

!

Tarragona 8 Mai 2008

d"

$ TT .id ! 2. CJ 0. VJ 2 ! VJ . vd %'

&

dt #

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Example 4 : transconductance amplifier

Library Disciplines;

use Disciplines.electrical_system.all;

Entity gmamp is -- transconductance amplifier with current limitation

generic (gm, ilim : real);

port (terminal inp, inm, outp, outm : electrical) ;

End entity gmamp

Architecture level_1 of gmamp is

constant vin1 : real := ilim/gm ; -- linear region for the gain

quantity vin across inp to inm

quantity iout through outp to outm ;

begin

if

vin > vin1 use iout == ilim ;

elseif vin < -vin1 use iout == -ilim ;

else iout == gm*v1 ;

end use;

end architecture level_1;

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Example 5 : CNA 1bit

Example 6 : mixed comparator

Library Disciplines;

use Disciplines.electrical_system.all;

Library Disciplines;

use Disciplines.electrical_system.all;

Entity dac_1 is -- digital-analogue converter 1 bit

generic (vcc : real := 5.0); -- supply voltage

port ( signal s : in bit ;

-- digital input

terminal a : electrical ); -- analogue output

End entity dac_1

Mixed interface

Entity comparator is -- mixed comparator

analogue-digital

generic (level : real := 2.5); -- threshold

port (terminal a : electrical ; -- analogue input

signal s : out bit) ;

-- digital output (bit)

End entity comparator

Architecture simple of dac_1 is

quantity vout across a ; -- across between a and ground

begin

if s = `0’ use vout = = 0.0 ;

Force computation of vout

else

vout = = vdd;

at each event of s

break on s ;

end architecture simple ;

Process is sensitive to a

Architecture simple of comparator is

Comparison

with a threshold

quantity vin across a ; -- across between

a and ground

begin

s <= `1' when vin'above(level) -- vin > level

else ‘0’ ;

-- vin < level

end architecture simple ;

break: SYNCHRONISATION of analogue part to the digital

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Heterogeneous Modelling – physical natures

!

Conservative systems written in VHDL-AMS allow the

modelling of different physical natures (thermal, hydraulic,

mechanic, ..)

Generalized quantities

nature

Electrical

Mechanical

(translation)

Mechanical

(rotation)

Thermal

Effort (across)

Voltage (V)

Position (m)

Flow (through)

Current (I)

Force (N)

Angular speed

(rd/s)

Temperature (°C)

Couple (N*m)

Magnetism

Magn eto driving

force (N*A)

Pressure (Pa)

Fluidic

Escuela Técnica Superior de Ingenieria

Thermal exchange

(W)

Flux (Weber)

Event at each time where vin voltage superior to level

threshold level : SYNCHRONISATION of digital part to analogue

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Example 7 : auto-thermal diode

package thermal_system is

subtype temperature is

real ; subtype power_th is

real;

nature thermal is temperature

across power_th

through ;

th_gnd reference ;

end package thermal_system

;

Cd

p

j

ic

Rs

power

id

Flow (l/s)

Tarragona 8 Mai 2008

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

m

Auto-thermal diode

Library IEEE, Disciplines;

use Disciplines.electrical_system.all; -- electrical nature

use Disciplines.thermal_system.all; -- thermal nature

use Disciplines.environment.all;

-- physical constants

use IEEE.math_real.all;

Entity diode_th is

generic (ISS, N, TT, CJ0, VJ, RS : real);

port (terminal p, m : electrical; terminal j : thermal ) ;

End entity diode_th

Architecture level_1 of diode_th is

quantity vd across id, ic through p to m ;

quantity temp across power through th_gnd to j ;

quantity qc : real;

quantity vt : voltage ;

begin

id == ISS *(exp((vd-RS*id) / N*vt)) - 1.0);

qc == TT*id - 2.0*CJ0*sqrt(VJ**2 - VJ*vd);

ic == qc ’dot;

vt == temp*boltzmann /elec_charge - - thermodynamic potential

power == vd * id :

end architecture level_1;

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Conclusion

# Nowadays, behavioural modelling is considered as a

very important step in the design field of

electronic products.

# The advent of high description languages like

VHDL-AMS, allows the development of new design

methodologies

$ Integrated Development Environment for analogue and mixed

circuits and in particular the System On Chip

$ This language allows the description and the modelling of

thermal, mechanical behaviours… besides the electrical

behaviour

$ Possibilities to simulate the validity of the global system in

its environment (thermal, radioactive…)

Escuela Técnica Superior de Ingenieria

Conclusion

Conclusion

# VHDL-AMS allows the development of new

software tools for the CAD of analogue and

mixed circuits

$ Modelling methodologies

$ Integration of the top-down design flow

$ Libraries creation of models of typical circuits or subcircuits associated to one or several architectures at

transistor level

$ Re-Use of already design blocks (!IP)

" Partial automation of the synthesis of

analogue systemsJ

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008

Tarragona 8 Mai 2008

# Demand is exploding for complete, integrated systems

that sense, process, manipulate, and control complex

entities (sound, images, motion, … and environmental

conditions).

# These systems, (hand-held devices, automotive subsystems, aerospace vehicles,…) employ electronics to

manage and adapt to a world that is predominantly,

neither digital nor electronic

" To respond to this design challenge, an unified design

language for modelling digital, analogue, mixed-signal,

and mixed-technology systems, VHDL-AMS, extends

VHDL to bring the successful HDL modeling methodology

of digital electronic systems design to these new design

disciplines.

Escuela Técnica Superior de Ingenieria

Tarragona 8 Mai 2008