1.4 The CMOS NOR Gate 1.5 The CMOS NAND Gate

advertisement

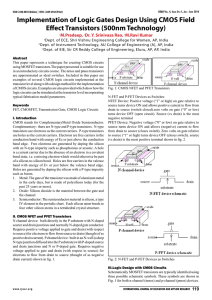

1.4 The CMOS NOR Gate The schematic diagram of a 2-input CMOS NOR gate is shown in Fig. 1.4. It can be seen that the transistors are driven in p-type cum ntype pairs by each input. Essentially, the n-type driving transistors are connected in parallel while the p-type load transistors are connected in series. Within each pair, either the n-type transistor will be ON while the p-type is OFF, or vice-versa, depending on the logic state of the associated input. A table of conduction states for all transistors can be drawn up to establish the logic function performed by the gate, as shown below. The state of the output can be established by treating the transistors which are ON as equivalent to closed switches and those that are OFF as equivalent to open switches. This is shown, for example, in Fig. 1.5 for the case where Input A is HI and Input B is LO. IN A IN B T1 T2 T3 T4 OUT LO LO OFF ON OFF ON HI LO HI OFF ON ON OFF LO HI LO ON OFF OFF ON LO HI HI ON OFF ON OFF LO 1.5 The CMOS NAND Gate The schematic diagram of a 2-input CMOS NAND gate is shown in Fig. 1.6. It can be seen that the structure is similar to the NOR gate, but in this case the n-type driving transistors are connected in series while the p-type load transistors are connected in parallel. Transistors are again driven in n-type cum p-type pairs with one transistor ON while the other is OFF. A table of the conducting states of the transistors for all logic combinations of the inputs is given below. The switch equivalent is shown for the case where Input A is HI and Input B is LO in Fig. 1.7 IN A IN B T1 T2 T3 T4 OUT LO LO OFF ON OFF ON HI LO HI OFF ON ON OFF HI HI LO ON OFF OFF ON HI HI HI ON OFF ON OFF LO 6 VDD T2 T4 OUT IN B T3 IN A Fig. 1.6 T1 Schematic Diagram of a 2-input CMOS NAND Gate VDD T4 T2 OUT IN B T3 T1 IN A Fig. 1.7 Equivalent Circuit of NAND Gate with IN A = HI and IN B = LO 8