Interface to 5V Circuits for the 3V MSP430 Families

advertisement

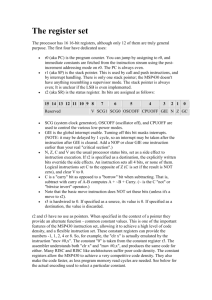

Application Report SLAA148 – October 2002 Interfacing the 3-V MSP430 to 5-V Circuits Lutz Bierl MSP430 ABSTRACT The interfacing of the 3-V MSP430x1xx and MSP430x4xx microcontroller families to circuits with a supply of 5 V or higher is shown. Input, output and I/O interfaces are given and explained. Worst-case design equations are provided, where necessary. Some simple power supplies generating both voltages are shown, too. Contents 1 Introduction .....................................................................................................................................2 2 Definitions........................................................................................................................................3 2.1 MSP430 Specification Values ...................................................................................................3 2.2 External System Definitions ......................................................................................................3 3 Input Interfaces ...............................................................................................................................4 3.1 Resistor-Divider Input Interfaces ...............................................................................................4 3.2 Transistor Input Interface ..........................................................................................................6 3.3 Op-Amp Input Interface .............................................................................................................7 3.4 ULN2003A Input Interface.........................................................................................................8 3.5 Integrated-Circuit Input Interface...............................................................................................9 3.6 Analog Input Interface ...............................................................................................................9 4 Output Interfaces ..........................................................................................................................10 4.1 Transistor Output Interface......................................................................................................10 4.2 Interface to CMOS-TTL Inputs ................................................................................................11 4.3 Interface to ULN2003 Inputs ...................................................................................................11 4.4 Op-Amp Output Interface ........................................................................................................12 4.5 Integrated-Circuit Output Interface ..........................................................................................13 5 Bidirectional Interfaces ................................................................................................................13 5.1 Simple, Bidirectional Op-Amp Interface ..................................................................................13 5.2 Integrated-Circuit I/O Interface ................................................................................................15 6 Power Supplies .............................................................................................................................16 7 Summary........................................................................................................................................18 References ...........................................................................................................................................18 Figure 1 Figure 2 Figure 3 Figure 4 Figure 5 Figure 6 Figure 7 Figure 8 Figure 9 Figure 10 Figures Interfaces Between the 3-V MSP430 and 5-V Systems ...................................................2 Resistor Input Interface From 5 V to the MSP430 ...........................................................4 Transistor Input Interface From a 5-V Environment........................................................6 Input Interfaces With Op Amps .........................................................................................8 Analog ADC12 Input Interface From 5 V to 3 V................................................................9 Transistor Output Interface to a 5-V Environment ........................................................10 Interfaces With High-Current Output Buffers ULN2003................................................12 Output Interfaces With Op Amps ....................................................................................13 Bidirectional Interface Between 3-V and 5-V Systems..................................................14 Integrated-Circuit I/O Interface........................................................................................16 LinCMOS is a trademark of Texas Instruments. Other trademarks are the property of their respective owners. 1 SLAA148 Figure 11 Figure 12 1 Capacitor Power Supply for Two Output Voltages .......................................................17 Power Supply for Two Output Voltages .........................................................................18 Introduction The modern MSP430s, such as the members of the MSP430x1xx family and the MSP430x4xx family, are available for the supply voltage range from 1.8 V to 3.6 V only. This is due to the manufacturing process used, and has the advantage of drawing even less current than with the 5-V supply used by the MSP430C3xx family. If an interface to a 5-V system—or a system with an even higher voltage—is necessary, it can result in difficulties. This application report shows and explains 5-V interfaces for the MSP430 inputs, outputs and I/Os. Figure 1 shows examples of input, output, and I/O interfaces. The gray shaded boxes are the topic of this application report. Note: In the following, the term MSP430 stands for the members of the MSP430x1xx and the MSP430x4xx families. Note: The given formulas for the external supply voltage V(sys) also can be used for higher voltages than 5 V. They are useful for any external voltage, e.g., V(sys) = 12 V. 3V DVCC AVCC COM SEL 5V 5V 3V 5-V Peripheral Output Interface 5 V to 3 V 0V 0V Tare 3V Input I/O Port 5V 5V I/O Interface 3 V to 5 V 5-V Peripheral 0V 0V MSP430x4xx 5V TTL-CMOS Peripheral 5V 3V Output Output DVSS AVSS 0V Output Interface 3 V to 5 V 5-V Peripheral 0V 0V 0V Figure 1. 2 Interfaces Between the 3-V MSP430 and 5-V Systems Interfacing the 3-V MSP430 to 5-V Circuits 5V SLAA148 With the worst-case equations, the following simplifications are used for the calculation with small values of ax (like for the tolerance p): 1 ≈ (1 − a x ) 1 + ax 1 ≈ (1 + a x ) 1 − ax 1 + ax ≈ (1 + 2a x ) 1 − ax 1 − ax ≈ (1 − 2a x ) 1 + ax The resulting errors can be neglected if |ax | < 0.1. 2 Definitions 2.1 MSP430 Specification Values The numeric values for the worst-case design equations are taken from [4]. The indicated values are for DVCC = 3 V: DVCC(min) Minimum digital supply voltage of the MSP430x4xx 1.8 V DVCC(max) Maximum digital supply voltage of the MSP430x4xx 3.6 V VIT(max) Maximum high input threshold voltage of an MSP430 port 1.9 V VIT(min) Minimum low input threshold voltage of an MSP430 port 0.9 V VOH(min) Minimum high port output voltage @ IO = –1.5 mA DVCC – 0.25 V VOL(max) Maximum low port output voltage @ IO = 1.5 mA DVSS + 0.25 V Ilkg Leakage current of an MSP430 input ±50 nA Absolute maximum current through the protection diodes of any MSP430 terminal (VI < – 0.3 V or VI > VCC+ 0.3 V) ±2 mA Note: The output impedance rDS(on) of an MSP430x4xx output is not taken into account, due to the choice of high resistor values with the design equations. The output impedance rDS(on) (max. 167 Ω) is very small compared to the resistors used. 2.2 External System Definitions V(sys) Supply voltage of the external system [V] V(sysH) High output voltage from the external system [V] V(sysL) Low output voltage from the external system [V] V(sys+) High input voltage of the external system [V] p Tolerance of the interface resistors [%] DVCC(min) Minimum supply voltage for the MSP430 with a DVCC = 3.0 V ±10% (3.0 V × 0.9 = 2.7 V) [V] Interfacing the 3-V MSP430 to 5-V Circuits 3 SLAA148 3 Input Interfaces The input interfaces shown are primarily intended for the interfacing between 5-V and 3-V systems. However, they also can be used for external voltages higher than 5 V, e.g., the interfacing of a 12-V signal to the MSP430 input. 3.1 Resistor-Divider Input Interfaces An external, digital input voltage VI(sys) is connected to the MSP430. The worst case equations for the two resistors R1 and R2 shown in Figure 2 are: R1 V( sysH) min − VIT(max) < R2 VIT(max) × (1 + 2p ) R1 and > V( sysL ) max − VIT (min) VIT (min) × (1 − 2p ) R2 and R1 || R2 << DVCC | Ilkg | The first two equations ensure that the input voltage VI(430) at the MSP430 input is above (when VI(sys) is high) or below (when VI(sys) is low) the worst case input threshold voltages. The third equation ensures that the leakage current Ilkg of the input does not influence the voltage VI(430). To avoid current into the input protection diodes of the MSP430 it is necessary that: V( sysH) max × R2 max < DVCC(min) + 0.3 R1 min + R2 max and V( sysL ) min × R2 min > − 0 .3 R1 max + R2 min 3V VI(sys) DVCC AVCC R1 MSP430x4xx Input R2 VI(430) DVSS AVSS 0V Figure 2. Resistor Input Interface From 5 V to the MSP430 EXAMPLE: the two input voltages from the system are V(sysH) = 5.0 V ±10% and V(sysL) = 0.5 V ±0.5 V. The resistor tolerance is p = ±5%. The minimum supply voltage of the MSP430 in this example is DVCC(min) = 2.7 V (3.0 V – 10%). With the above specifications for the threshold voltages VIT(max) and VIT(min) this leads to the condition for the input voltage V(sysH)min: 4 Interfacing the 3-V MSP430 to 5-V Circuits SLAA148 V( sysH) min − VIT(max) 4 . 5 V − 1. 9 V R1 = < R2 VIT(max) × (1 + 2p ) 1.9 V × (1 + 0.1) R1 < 1.244 R2 → The condition for the low input voltage V(sysL)max is: 1 .0 V − 0 .9 V R1 V( sysL ) max − VIT(min) > > R2 VIT(min) × (1 − 2p ) 0.9 V × (1 − 0.1) → R1 > 0.1234 R2 To ensure negligible influence of the leakage current Ilkg: R1 || R2 << DVCC Ilkg = 3V ± 50 nA → R1 || R2 << 60 MΩ The three design equations above allow a wide range for R1 and R2. If R1/R2 is chosen to be 1.0 and R1||R2 to be 600 kΩ, then R1 = 1.2 MΩ and R2 = 1.2 MΩ. To avoid current into the input protection diodes of the MSP430 it is necessary: V( sysH) max × R2 max < DVCC(min) + 0.3 R1 min + R2 max 5.5 V × 1.26 MΩ < 2 .7 V + 0 .3 1.14 MΩ + 1.26 MΩ 0.0 V × 1.14 MΩ > − 0 .3 V 1.26 MΩ + 1.14 MΩ → → V( sysL ) min × and 2.8875 V < 3.0 V + 0.0 V > − 0.3 V R2 min > − 0.3 R1max + R2 min the condition is true. the condition is also true. The last two equations are not important if the current into the MSP430 input is far below ±2 mA (the absolute maximum rating value for an input current). This is the case for the example given: R1||R2 = 600 kΩ. The above mentioned design equations are valid for the following MSP430 terminals, if switched to the input direction: • All I/O ports (ports P1 to P6) • Crystal inputs XIN and XT2IN: VIL(X)max = 0.2 × DVCC, VIH(X)min = 0.8 × DVCC • RST/NMI input: VILmax = DVSS +0.6 V, VIHmin = 0.8× DVCC • Comparator_A inputs CA0 and CA1 • UART/SPI inputs URXDx, SOMIx, SIMOx, UCLK • Timer_A inputs TACLK, TA0 to TA2 Interfacing the 3-V MSP430 to 5-V Circuits 5 SLAA148 3.2 • Timer_B inputs TBCLK, TB0 to TB6 • ADC12 inputs: the sample time t(sample) must be adapted to the impedance R1||R2 of the resistor divider. For more information, see the ADC12 chapter of [2] or [3]. Transistor Input Interface The transistor-input interface is a very simple interface that can adapt many external systems to the MSP430 family. Figure 3 shows an example for an inverting input buffer. The resistor RC can be switched off by an output to save current during low-power mode 3. 3V 3V Output RC VI(sys) DVCC AVCC MSP430x4xx Input RB1 DVSS AVSS RB2 0V Figure 3. Transistor Input Interface From a 5-V Environment The design equations for the resistors RC, RB1 and RB2 are: RC < DVCC(min) − VIT(max) (1 + p) × (Ilkg + Ilkg( Tr ) ) ensures high potential at the MSP430 with leakage currents ⎞ R B1 ⎛⎜ V( sysL ) max > − 1⎟ × (1 + 2p ) ⎟ ⎜ R B2 ⎝ VBE( off ) ⎠ ensures turnoff of the transistor for input voltage V(sysL)max The third equation ensures the turnon of the transistor for the input voltage V(sysH)min: R B1 ⎛ ⎞ R V( sysH) min − VBE( on ) × ⎜⎜1 + B1 × (1 + 2p )⎟⎟ R B2 ⎝ ⎠ < × β min × R C min DVCC(max) Where 6 VBE(off) Transistor base-emitter voltage for secure turnoff [V] VBE(on) Transistor base-emitter voltage for secure turnon [V] β Current amplification of the transistor Ilkg(Tr) Leakage current of the transistor Interfacing the 3-V MSP430 to 5-V Circuits [A] SLAA148 Example: Input voltage VI(sys) is connected to an MSP430 input with Ilkg = ±50 nA. The minimum high-input level V(sysH)min = 4.5 V, the maximum low-input level V(sysL)max = 0.7 V. The resistor tolerance of all resistors is p = ±5%. The supply voltage is DVCC = 3 V ±10%. The transistor properties are VBE(on) = 0.75 V, VBE(off) = 0.2 V, βmin = 100, Ilkg(Tr) = 10 nA. The maximum nominal value for RC is: RC < DVCC(min) − VIT(max) = 2.7 V − 1.9 V (1 + p) × (Ilkg + Ilkg( Tr ) ) (1 + 0.05 ) × (50 nA + 10 nA ) = 12.7 MΩ chosen RC = 2 MΩ The minimum ratio for the nominal values of RB1 and RB2 is: ⎞ ⎞ R B1 ⎛⎜ V( sysL ) max ⎛ 0 .7 V > − 1⎟ × (1 + 2p ) = ⎜⎜ − 1⎟⎟ × (1 + 0.1) = 2.75 ⎜ ⎟ R B2 ⎝ VBE( off ) ⎠ ⎝ 0 .2 V ⎠ The maximum nominal value for RB1 is: ⎛ ⎞ R V( sysH) min − VBE( on ) × ⎜⎜1 + B1 × (1 + 2p )⎟⎟ R B2 ⎝ ⎠ RB1 < × β min × R C min DVCC(max) R B1 < 4.5 V − 0.75 V × [1 + 2.75 × (1 + 0.1)] × 100 × 2 MΩ × (1 − 0.05 ) = 85.3 MΩ DVCC(max) chosen RB1 = 39 MΩ With the value 39 MΩ for RB1 the resistor RB2 gets: RB 2 < 3.3 RB1 39 MΩ = = 14.18 MΩ 2.75 2.75 chosen RB2 = 10 MΩ Op-Amp Input Interface Op amps for the input interface are the best choice, if they are needed anyway for the system (as an integrator, comparator, amplifier, DAC, etc.). For the TLC27L4 it is necessary to limit the input voltages to a maximum of VDD + 0.3 V. The minimum supply voltage of the TLC27L4 VCC(min) = 3 V. Interfacing the 3-V MSP430 to 5-V Circuits 7 SLAA148 3.3 V 3.3 V 3.3 V TLC27L4 RB1 VDD DVCC AVCC + From External Circuits + Input - Vref ≈ 1.6 V 0V-5V + Input R1 VI(sys) 0 V - 12 V + Input - DVSS AVSS GND R2 Figure 4. RB2 Input Interfaces With Op Amps The worst case equations for the two resistors R1 and R2 shown in Figure 4 is: R1 V( sysH) min − Vref (max) < R2 Vref (max) × (1 + 2p ) where R1 V( sysL ) max − Vref (min) > R2 Vref (min) × (1 − 2p ) and Vref (max) = DVCC(max) × R B2 max R B1 min+ R B2 max and R1 || R2 << and Vref (min) = DVCC(min) × DVCC Ilkg R B 2 min R B1 max + R B2 min A calculation example is given in Resistor Divider Input Interface, Section 3.1. 3.4 ULN2003A Input Interface On the left side of Figure 7, three ULN2003A buffers are used for the input interfacing to 5-V and 12-V systems. The series resistor RV (p = ±5%) for the 12-V input signal (V(sysH)min = 11 V) is: RV < V( sysH) min − VI( on ) min (1 + p) × II(on) max = 11 V − 2.4 V 1.05 × 1.35 mA → R V max < 6.06 kΩ chosen RV = 6.0 kΩ The pullup resistor Rp at the MSP430 input is: Rp < VCC − VIT(max) (1 + p) × ICE max = 3 V − 1. 9 V 1.05 × 50 μA → Rp max < 20.9 kΩ chosen Rp = 20 kΩ To avoid current consumption, the resistors Rp are switched to DVCC only when necessary. 8 Interfacing the 3-V MSP430 to 5-V Circuits SLAA148 3.5 Integrated-Circuit Input Interface For a 5-V to 3.3-V input interface, any CMOS-circuit can be used which fulfills the following two conditions: • It is built for a supply voltage of 3.3 V or lower. • It is explicitly allowed to use input voltages higher than 3.3 V. The AHC and LVC families fulfill both conditions. They share the 3.3-V supply of the MSP430. Note: A check is necessary to determine if an input voltage VI higher than the 3.3-V supply is really allowed. This means, in the data sheet under absolute maximum ratings the following entry appears: Input voltage range VBI……………………….0.5 V to 7 V And not as usual with other CMOS circuits: Input voltage range VI……………………….0.5 V to VCC+0.5 V or Input clamp current IIK (VI < 0 or VI > VCC) …±20 mA 3.6 Analog Input Interface The same resistor divider solution as shown for the digital interfaces above is possible for the analog ADC12 inputs. Figure 5 shows the connection of a 5-V Hall-sensor current interface to the ADC12 input Ax. The worst case equations for the resistor divider can be seen in Resistor Divider Input Interfaces, Section 3.1. 5V 3V Hall-Sensor Transfer Characteristic VCC Current DVCC AVCC Hall-Sensor Current I/F Ax AC Out R2 GND 0V Figure 5. 4.0 V MSP430x4xx R1 Output AC In Output V (adc) 3.0 V 2.0 V DVSS AVSS 1.0 V 0V -15 A 0A 15 A Current Analog ADC12 Input Interface From 5 V to 3 V Interfacing the 3-V MSP430 to 5-V Circuits 9 SLAA148 If the external peripheral cannot deliver the current for the resistor divider, a unity-gain op amp can be placed between the peripheral output and resistor R1. The ADC12 sample time t(sample) must be adapted to the impedance R1||R2 of the resistor divider. For more information, see the ADC12 chapter of [2] or [3]. 4 Output Interfaces No interface is needed for LCDs and for passive sensors. They are directly connected to the MSP430 in the usual way. See [2]. 4.1 Transistor Output Interface A simple interface to systems with higher supplies than 3 V is shown in Figure 6. The transistor load RL can be nearly anything: resistors, fans, heating coils, relays, etc. The base resistor RB can be calculated with the equation: B RB < ( R L min × β min × VOH(min) − VBE( on ) (1 + p) × V( sys) max Where ) RLmin Minimum load resistor [Ω] βmin Minimum current amplification of the transistor V(sys)max Maximum supply voltage of the external system [V] VBE(on) Transistor base-emitter voltage for turnon [V] Due to the low output voltage of the MSP430 port, no resistor from the transistor base to 0 V is necessary. +3V Vsys DVcc AVcc RL IL MSP430x4xx To external System Port RB Vout DVss AVss VCEsat to Vsys 0V Figure 6. Transistor Output Interface to a 5-V Environment Example: a load RL = 100 Ω ±3% is connected to V(sys) = 5 V ±10%. The resistor tolerance of RB is p = ±10%. The minimum supply voltage in this example is DVCC(min) = 2.7 V (3.0 V – 10%). The transistor properties are VBE(on) = 0.7 V and βmin = 100. B RB < 10 100 Ω × (1 − 0.03 ) × 100 × (2.7 V − 0.25 V − 0.7 V ) (1 + 0.1) × 5V × (1 + 0.1) Interfacing the 3-V MSP430 to 5-V Circuits → R B < 2805.8 Ω chosen RB = 2.7 kΩ B SLAA148 4.2 Interface to CMOS-TTL Inputs All integrated circuits with TTL-CMOS inputs can be used as output circuits for the MSP430x1xx and MSP430x4xx. The input voltages of these ICs are: VIHmin Minimum high-level input voltage 2.0 V VILmax Maximum low-level input voltage 0.8 V Both voltages are within the output voltage range of an MSP430 output: DVCC – 0.25 V and DVSS + 0.25 V for DVCC = 2.7 V to 3.6 V. No interface circuit is necessary; the TTL-CMOS ICs contain the 3-V/5-V interface on-chip. 4.3 Interface to ULN2003 Inputs For high output currents or to drive up to seven 5-V output ports, the ULN2003A output buffer can be used. The properties of the ULN2003A are: ILmax Maximum output current 500 mA VLmax Maximum output voltage 50 V VI(on)max Maximum input voltage (IL = 200 mA) 2.4 V II(on)max Maximum input current (VI = 3.85 V) 1.35 mA ICEmax Maximum output leakage current (VCE = 50 V) 50 μA On the right side of Figure 7, the ULN2003A is used for the output buffering to 5-V and 12-V peripherals. The common free-wheeling diodes of the ULN2003A used for the 12-V peripherals do not influence the 5-V signals. Interfacing the 3-V MSP430 to 5-V Circuits 11 SLAA148 Common Free-Wheeling Diodes 3V 12 V 4/7 ULN2003A 5 V 3 × Rp 3/7 ULN2003A CFWD DVCC AVCC Buffered ACLK ACLK Inputs 20 kHz Motor 1 (Fan) Input 0V-5V TB1 M 12 V Relays Signal Load TRIAC Input 0V-5V 5V Port 20 kHz VI(sys) 0 V - 12 V Motor 2 (Pump) RV Input TB2 DVSS AVSS GND M 12 V GND 0V Figure 7. Interfaces With High-Current Output Buffers ULN2003 The input interface on the left side of Figure 7 is described in ULN2003A Input Interface, Section 3.4. 4.4 Op-Amp Output Interface With the quad op amp TLC27L4, an interface to system voltages V(sys) of up to 16 V can be realized. The resistor divider at the inverting inputs of the TLC27L4 generates a voltage of approximately 1.5 V. The values for RB1 and RB2 must fulfill the equation: R B1 || R B2 << 12 DVCC ∑I lkg( Op ) = 3V = 1.07 GΩ 4 × 0.7 nA Interfacing the 3-V MSP430 to 5-V Circuits This allows resistors with 10 MΩ resistance. SLAA148 3V 3V V(sys) TLC27L4 RB1 DVCC AVCC VDD + ≈ 1.5 V 0-V(sys) - Output + 0-V(sys) Output + 0-V(sys) Output + 0-V(sys) DVSS AVSS Figure 8. 4.5 RB2 Outputs GND Output Interfaces With Op Amps Integrated-Circuit Output Interface Nearly all TTL-compatible ICs, such as the HCT and AHCT families, can be used for 3-V to 5-V output interfaces. The same is true for all bipolar circuits. If the 5-V supply is switched off during the time when the 3-V supply is still on (e.g., during a power down of the 5-V supply as shown in Figure 11), then only circuits that do not have built-in ESD protection diodes can be used for the input to the VCC connection. Otherwise, a current flows from the 3-V supply to ground via this protection diode. This means that only AHCT and bipolar circuits can be used in this case. 5 Bidirectional Interfaces 5.1 Simple, Bidirectional Op-Amp Interface If true I/O performance is needed between the MSP430 and a 5-V system, then the interface circuit shown in Figure 9 can be used. The op amp works as a flip-flop: the I/O pin currently working as an output controls the state of this flip-flop. The other I/O pin must be an input. Interfacing the 3-V MSP430 to 5-V Circuits 13 SLAA148 Vsys (+5V) +3V Bi-directional Interface MSP430x4xx 5V System Vcc DVcc AVcc ¼ TLC27L4 Vsys - RDSon Vref = DVcc/2 RDSon DVcc Ilkg DVss Ilkg(sys) I/O Pin + I/O Pin Vcc R3 0V Vss RDSon RDSon R4 R5 DVss AVss Vss 0V 0V Figure 9. Bidirectional Interface Between 3-V and 5-V Systems The worst-case design equations for the resistors R3, R4 and R5 are: ⎛ V( sysH) min ⎞ R4 < (1 − 2p ) × ⎜ − 1⎟ ⎜ ⎟ R5 ⎝ Vref (max) ⎠ ensures a high level at the MSP430 input ⎛ V( sysH) max ⎞ R4 > (1 + 2p ) × ⎜ − 1⎟ ⎜ ⎟ R5 ⎝ DVCC(min) ⎠ prevents voltages higher than DVCC at the MSP430 input The next equation ensures high level at the MSP430 input with the MSP430 and op amp leakage currents Ilkg and Ilkg(Op): R4 ⎛ ⎞ V( sysH) min − Vref (max) × ⎜1 + × (1 + 2p )⎟ R5 ⎝ ⎠ R4 < Ilkg + Ilkg( Op ) × (1 + p ) ( ) The last equation ensures a high level at the external system input with its leakage current Ilkg(sys): V ( sys) min − V( sys+ ) min R3 < ⎛ (1 + p) × ⎜⎜Ilkg( sys) ⎝ Where + V( sys+ ) min − Vref (min) ⎞ ⎟ ⎟ R4 × (1 + p ) ⎠ Vref Reference voltage for the input level decision [V] Ilkg Input leakage current of an MSP430 input [A] Ilkg(Op) Input leakage current of the opamp input [A] Ilkg(sys) Input leakage current of the system input [A] Example: bidirectional interface for the following data: V(sys) = 5 V ±10%, V(sysH)min = 4 V, V(sys+)max = 3.5 V, Ilkg(sys) = ±1 μA, Ilkg(Op) = ±700 pA, Ilkg = ±50 nA, Vref = 1.5 V ±5%. The resistor tolerance is p = ±5%. The minimum supply voltage of this example is DVCC(min) = 2.7 V (3.0 V – 10%). 14 Interfacing the 3-V MSP430 to 5-V Circuits SLAA148 ⎞ ⎛ V(sysH)min ⎛ 4V ⎞ R4 − 1⎟⎟ = 1.386 < (1 − 2p ) × ⎜ − 1⎟ = (1 − 2 × 0.05 ) × ⎜⎜ ⎟ ⎜ R5 ⎝ 1.575 V ⎠ ⎠ ⎝ Vref (max) ⎞ ⎛ V(sysH)max ⎛ 5 .5 V ⎞ R4 − 1⎟⎟ = 1.14 > (1 + 2p ) × ⎜ − 1⎟ = (1 + 2 × 0.05 ) × ⎜⎜ ⎟ ⎜ R5 ⎝ 2 .7 V ⎠ ⎠ ⎝ DVCC(min) The medium value of the two R4/R5 limits is taken: R4 1.38 + 1.14 = = 1.26 R5 2 R4 ⎛ ⎞ V( sysH) min − Vref (max) × ⎜1 + × (1 + 2p )⎟ R 5 ⎝ ⎠ 4.0 V − 1.575 V × (1 + 1.26 × (1 + 2 × 0.05 )) R4 < = = 4.55 MΩ (50 nA + 700 pA ) × (1 + 0.05 ) Ilkg + Ilkg( Op ) × (1 + p ) ( ) R4 is chosen to be 2 MΩ. Resistor R5 is calculated as: R5 = R3 < V(sys)min − V( sys+ ) max V max − Vref (min) ⎛ (1 + p) × ⎜⎜ Ilkg( sys) + (sys+ ) R4 × (1 + p ) ⎝ ⎞ ⎟ ⎟ ⎠ = 2 MΩ R4 = = 1.59 MΩ 1.26 1.26 4 . 5 V − 3. 5 V (1 + 0.05 ) × ⎛⎜⎜1μA + 3.5 V − 1.425 V ⎞⎟⎟ 2 MΩ × (1 + 0.05 ) ⎠ ⎝ = 479 kΩ The three chosen resistors are: R3 = 330 kΩ, R4 = 2 MΩ, R5 = 1.6 MΩ 5.2 Integrated-Circuit I/O Interface Dedicated level converters like the SN74LVCC4245A can be used for a bidirectional I/O interface. It is an 8-bit wide level converter, which can convert the I/O levels to 5 V for a complete MSP430 port. Figure 10 shows an application with this IC. The MSP430 determines the data direction of the interface with the DIR terminal. If needed, bus A can be isolated from bus B with the OE terminal. Interfacing the 3-V MSP430 to 5-V Circuits 15 SLAA148 3.3 V 3.3 V 5V DVCC AVCC VCCB VCCA 0V MSP430x4xx OE SN74LVCC4245A I/O Port Bus B Output DVSS AVSS A1 to A8 B1 to B8 Bus A 8 I/Os to 5-V Peripherals DIR GND 0V Figure 10. Integrated-Circuit I/O Interface 6 Power Supplies Note: the design equations for the power supplies below are given in the Power Supplies for MSP430 Systems chapter of [1]. This chapter also describes other kinds of power supplies, e.g., transformer driven supplies, with their design equations. Figure 11 shows a capacitor power supply for two output voltages, VCC1 = 3 V and VCC2 = 5 V. If the output current of the TLC27L4s is not sufficient, an NPN output buffer can be used as shown in Figure 12. 16 Interfacing the 3-V MSP430 to 5-V Circuits SLAA148 Mains 3R Cm VC PD V 5V CC2 Rm D VC To 5-V Peripherals 1.4 R To 3-V Peripherals V 3V CC1 DZ Cch AV CC DV CC 1.25 V 0V LMx85 R R ≈ 1 MΩ 1/2 TLC27L4 MSP430x4xx 0V DV SS AVSS To Peripherals Figure 11. Capacitor Power Supply for Two Output Voltages Using the power-down output, PD, the MSP430 can switch off the 5-V supply during low power periods (LPM3): • Active mode: the MSP430 PD output is switched to the high-impedance mode. • LPM3: the MSP430 output PD is switched to DVCC. The 5-V regulator outputs a voltage near 0 V. Figure 12 shows a power supply for two output voltages VCC1 = 3 V and VCC2 = 5 V. The 3-V supply is buffered with an NPN transistor to allow a higher current. Interfacing the 3-V MSP430 to 5-V Circuits 17 SLAA148 To 5-V Peripherals 8 V to 12 V 7805 5V 2R To 3-V Peripherals + AV CC DVCC - Cch 3V 3R MSP430x4xx 0V 1/4 TLC27L4 0V DVSS AV SS To Peripherals Figure 12. Power Supply for Two Output Voltages 7 Summary As this application report showed, it is possible to build cost-effective interfaces for the connection of the 3-V MSP430 families to a 5-V environment. In some cases, the external 5-V peripherals already contain the necessary interface. Thanks to Eilhard Haseloff for his very helpful hints. References 1. MSP430 Family Mixed-Signal Microcontroller Application Reports, Literature Number SLAA024 2. MSP430x4xx Family User’s Guide, Literature Number SLAU056 3. MSP430x1xx Family User’s Guide, Literature Number SLAU049 4. MSP430x43x, MSP430x44x Mixed Signal Microcontroller data sheet, Literature Number SLAS344 5. TLC27L4, TLC27L4A, TLC27L4B,TLC27L4Y, TLC27L9 LinCMOS™ Precision Quad Operational Amplifiers data sheet, Literature Number SLOS053 6. ULN2001A, ULN2002A, ULN2003A, ULN2004A,ULQ2003A, ULQ2004A High-Voltage HighCurrent Darlington Transistor Array data sheet, Literature Number SLRS027 7. SN74LVCC4245A Octal Dual-Supply Bus Transceiver With Configurable Output Voltage and 3-State Outputs data sheet, Literature Number SCAS584 8. Selecting the Right Level-Translation Solutions application report, Literature Number SCEA035 18 Interfacing the 3-V MSP430 to 5-V Circuits