Integrated Circuit Design of Sigma

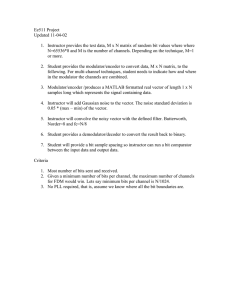

advertisement