LEC-22: Critical Paths and False Paths

advertisement

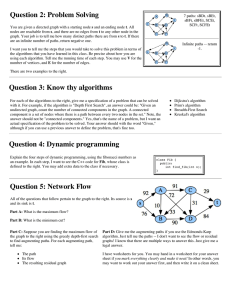

LEC-22 Preliminaries 1 LEC-22 Preliminaries 3 Announcements LEC-22: Critical Paths and False Paths Midterm marking Vol II of Course Notes available University of Waterloo Dept of Electrical and Computer Engineering E&CE 427 Digital Systems Engineering 2004t3–Fall LEC-22 Preliminaries 2 Schedule wk-01 – 02 wk-03 – 04 wk-05 – 06 wk-06 – 07 wk-08 – 09 VHDL RTL Design Techniques Functional Verification Performance Analysis and Optimization Timing Analysis lec-21 Timing analysis for storage lec-22 Critical paths lec-23 Elmore timing model wk-09 Power Analysis and Reduction wk-10 – 11 Faults and Testing wk-11 – 12 Reliability and Fault Tolerance wk-13 Review Today Find the path through the circuit that limits the clock speed. Distinguish between real critical paths and false critical paths. LEC-22: 5.4 5.4.1 Critical Paths (Page 243) Critical Paths and False Paths Definition critical path: The slowest path on the chip between flops or flops and pins. The critical path limits the maximum clock speed. 5.4.1 Critical Paths 4 LEC-22: 5.4.1 Critical Paths (Page 243) 5 LEC-22: 5.4.1 Example: Full Adder Karnaugh map showing a possible alternative excitation of critical path: a b a b ci ci 1 1 1 0 1 0 0 1 0 0 gate delay NOT 2 AND 4 OR 4 XOR 6 Test if alternative input exercises the critical path. ci a b s co LEC-22: 5.4.1 Critical Paths (Page 243) 7 Alternative Excitation Find the critical path through the full-adder circuit shown below. ci a b Critical Paths (Page 243) s co 6 Karnaugh Maps Test another set of input values along the same path. LEC-22: 5.4.1 Critical Paths (Page 243) 8 Outline of Algorithm to Find Critical Path 1. Start at source node and traverse through fanout to destination node, annotating intermediate nodes with maximum delay to the intermediate nodes. 2. The delay to the destination node is the delay of the critical path. The “427” way of writing Karnaugh maps and the “old-fashioned” way of writing Karnaugh maps: ab a b 10 11 01 00 ci 1 ci 0 Karnaugh map showing transition that exercised critical path: a b ci 0 1 a b ci 1 1 1 0 0 1 0 0 3. The critical path is found by starting at the destination path and working backwards, choosing node with maximum delay at each step. LEC-22: 5.5 5.5 False Paths (Page 243) 9 False Paths LEC-22: 5.5 False Paths (Page 243) 11 Revised Algorithm to Find Critical Path 1. Find candidate critical path using previous algorithm Sometimes the path that appears to be the critical path is actually a false path. 2. Test if candidate path is really the critical path a 3. If candidate is not critical, then update delay information and return to step 1. y 4. If candidate is critical, then done. b c a y b c a y b c LEC-22: 5.5 FALSE PATHS (Page 243) 10 False Path Trickery 5.5.1.1 5.5.1 Sometimes a path that appears to be a false path is actually the critical path. a y b a y b a y b Lec-22: 5.5.1.1 (pp 246) Preliminaries Testing a Critical Path Preliminaries Definitions delay data disclosure.... 12 Lec-22: 5.5.1.1 (pp 246) Preliminaries 13 Lec-22: 5.5.1.1 Controlling Value (pp 246) Preliminaries 15 Critical Input, Side Input The controlling value of a gate is the value such that if one of the inputs has this value, the output can be determined independent of the other inputs. For an AND gate, the controlling value is ’0’, because when one of the inputs is a ’0’, we know that the output will be ’0’ regardless of the values of the other inputs. For a gate on a path (either a candidate critical path, or a real critical path), the critical input is the input signal that is on the path. For a gate on a path (either a candidate critical path, or a real critical path), the side inputs are the input signals that are not on the path. The controlled output value of a gate is the value produced by the controlling input value. Gate Controlling Value Controlled Output AND OR NAND NOR XOR Lec-22: 5.5.1.1 (pp 246) Preliminaries 14 Reconvergent Fanout (pp 246) Preliminaries 16 To determine if a path through a circuit is a false path: 0 or 0 1 backwards 1. Start at the destination node of path, try to push a 1 along the candidate critical path. Hint, pick the edge whose final value is the controlled output of the gate. The wires that fanout from a gate reconverge at another gate. a y c 5.5.1.1 5.5.1.2 Algorithm to Determine if a Path is the Critical Path Most of the difficulties with critical paths and testing circuits are caused by reconvergent fanout. b Lec-22: z 2. Follow the critical path backwards through each gate. For the critical input, assign the value needed to produce the current value on the output (figure??). For the side inputs, assign non-controlling values or edges that end in noncontrolling values. 3. If different values are assigned to the same signal, then try to push another edge or glitch backwards through the circuit. 4. If have tried both rising and falling edges and both low and high glitches, and all four options have produced contradictory assignments, then the candidate path is a false path. Lec-22: 5.5.1.1 (pp 246) Preliminaries 17 Lec-22: 5.5.1.1 (pp 246) Preliminaries 19 Missing Rules? Ending Conditions for Algorithm To be precise: a candidate path is a false path iff, for every vector of input values to the circuit, there is a gate along the path such that a side input with a controlling value has a shorter path to the inputs. If don’t assign different values to same signal, then assignments calculated along path give values that will exercise critical path. Question: Why do the rules not have falling edges for AND gates or rising edge for OR gates? Push values on non-critical nodes to primary inputs to give assignment that will exercise the critical path. Lec-22: 5.5.1.1 (pp 246) Preliminaries 18 Lec-22: 5.5.1.1 1 0 0 Find the longest path in the circuit below and determine if the longest path is the critical path. a 1 1 0 b d e h z f b c 0 20 Real Example of False Paths Rules for Pushing Edges and Glitches 1 (pp 246) Preliminaries c g i y LEC-22: 5.5.2 Finding the Next Candidate Path (Page 251) 21 5.5.2 Finding the Next Candidate Path LEC-22: 5.5.3 More False Path Examples (Page 251) 23 5.5.3 More False Path Examples To find the next candidate critical path, recompute delay values along the false path. Leave all other delays the same as before. Ex: Need to Test Both Rising and Falling For each node along the false path, maintain two delay values. One delay is the value already calculated. The other delay value is the maximum delay to that node, ignoring the prefix of false path. The prefix of a false path is the set of nodes whose fanin comes only from false paths. Edges a As a shortcut, you do not need to maintain two delay values for nodes in the suffix of the false path. The suffix is the set of nodes who fanout only to the false path. The nodes in the suffix do not need to maintain their old delay value. They only need their new delay value. c d f e b a c d f e b LEC-22: a 5.5.2 2 Finding the Next Candidate Path (Page 251) 4 4 0 8 0 b c 8 8 2 2 2 22 10 5.5.3 More False Path Examples (Page 251) 24 Ex: Need to Test Glitches z e 2 12 12 LEC-22: 16 y a c f d b e a 2 4 0 8 8 0 b c 4 2 8 2 2 12 a 10 2 12 c f z d 16 y b e a c d b f LEC-22: 5.5.3 More False Path Examples (Page 251) 25 Ex: A Simple False Path LEC-22: 5.5.4 High-Level Analysis of False Paths (Page 254) 5.5.4 High-Level Analysis of False Paths 27 Sometimes the delay through a component is dependent upon the values on signals. This is because different paths in the circuit have different delays and some input values will prevent some paths from being exercised. Here are two simple examples: a In a ripple-carry adder, if a carry out of the MSB is generated from the least significant bit, then it will take longer for the output to stabilize than if no carries generated at all. In a state machine using a one-hot state encoding, false paths might exist when more than one state bit is a ’1’. a Because of these effects, static timing analysis might be overly conservative and predict a delay that is greater than you will experience in practice. The most accurate delay analysis requires looking at the actual data values that will occur in practice. Conversely, a timing simulation may not demonstrate the actual slowest behaviour of your circuit: if you don’t ever generate a carry from LSB to MSB, then you’ll never exercise the critical path in your adder. a LEC-22: 5.5.3 More False Path Examples (Page 251) 26 Ex: Xors in Example Question: Find the false critical path in the circuit below. a b c d e f i h g k j