Overview of Lecture Notes

Overview of Lecture Notes

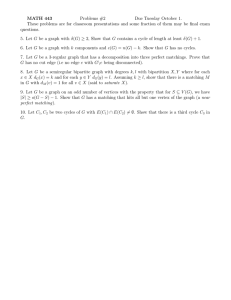

• Discussion of switch architectures, algorithms, proofs

• The crossbar switch architecture

• Speedup and delay control in CIOQ (crossbar) switches

• Stable Marriage Algorithms

EE384X Packet Switch Architectures I 1

The story so far

• We have seen

several architectures and algorithms for switches and packet buffers

why is OQ switch ideal?

what are ways of emulating its behavior?

the PPS, DSM architectures

building packet buffers

• The large lessons we learnt were that

there are trade-offs: quantifiable via the pigeon-hole principle

• In the next couple of lectures we’re going to

see the crossbar switch architecture

OQ, IQ and CIOQ switches and emulation of OQ switches

Stable Marriage Algorithms

EE384X Packet Switch Architectures I 2

A CIOQ switch

• Consists of

an (internally non-blocking, e.g. crossbar) fabric with speedup S > 1

input and output buffers

a scheduler to determine matchings

I n p u t s

M e m o r y

Fabric

M e m o r y

O u t p u t s

Scheduler

• For concreteness, suppose S = 2 . The operation of the switch consists of

transferring no more than 2 cells from (to) each input (output)

logically, we will think of each time slot as consisting of two phases

arrivals to (departures from) switch occur at most once per time slot

the transfer of cells from inputs to outputs can occur in each phase

EE384X Packet Switch Architectures I 3

Trade-offs

• We know that

o/q switches have excellent delay properties - the best they automatically give 100% throughput but, the memory bandwidth requirement is very high

i/q switches may or may not have good delay properties

(we’ll see later that) algorithms known to give 100% throughput are complex but, the memory bandwidth requirement is minimal

EE384X Packet Switch Architectures I 4

How to get good delay cheaply?

• Enter speedup...

the fabric speedup for an i/q switch equals 1 (mem. bwdth. = 2)

the fabric speedup for an o/q switch equals N (mem. bwdth. = N +1)

suppose we consider switches with fabric speedup of S , 1 < S N

such switches will require buffers both at the input and the output (why?)

→ call these combined input- and output-queued (CIOQ) switches

• Such switches could help if...

with very small values of S

now let us look at a bit of background research into speedup...

EE384X Packet Switch Architectures I 5

Some approaches for using speedup

• Probabilisitc Analyses: Assume traffic models

Bruzzi and Pattavina ’90, Chen and Stern ’91, Iliadis and Denzel ’93

Lin and Sylvester ’93, Chang, Paulraj and Kailath ’94, etc.

• Numerical Methods: Use simulated and actual traffic traces

Murata, Kubota, Miyahara ’89, Lee and Li ’91, Goli and Kumar ’92, Lee and Liu ’94,

Bianchini and Kim ’95, etc.

• Both approaches showed that switches which use a speedup of between 2 and 5 achieve the same mean delay and throughput as an output-queued switch (whose speedup is N )

EE384X Packet Switch Architectures I 6

Arbitrary inputs and emulation of OQ switch

• How much better can switches with a small speedup behave?

i.e. can we say something about delay given that it still depends on traffic statistics?

there is one way of doing this: competitive analysis

→ the idea is to compete with the performance of an o/q switch

Inputs

Speedup = N

?

Speedup << N

Outputs

• The setup

under arbitrary, but identical inputs (packet-by-packet)

is it possible to replace an o/q switch by a CIOQ switch and schedule the CIOQ switch so that the outputs are identical packet-by-packet?

if yes, what is the scheduling algorithm?

EE384X Packet Switch Architectures I 7

Consequences

• Suppose, for now, that a CIOQ is competitive wrt an o/q switch. Then

we get perfect emulation of an o/q switch

this means we inherit all its throughput and delay properties

but, at the cost of introducing a scheduling algorithm - needs to be studied

• Why might we expect that all this is possible?

no reason, it sounds crazy at first sight

but, some hope comes from prior work which heuristically concluded that: under a variety of input conditions and for different switch sizes, a small speedup (between 2 and 5) leads to performance close to an o/q switch

(we saw citations for this a few slides ago)

• In order to design algorithms for OQ switch emulation

using CIOQ switches running at a small speedup

and using algorithms that only use the RGA routine we need to understand Stable Marriage Algorithms

EE384X Packet Switch Architectures I 8

Digression: Stable Marriage Algorithms

• Stable Marriage Algorithms (SMs) and Switch Scheduling: It turns out that

most, if not all, switch scheduling algorithms using an RGA routine are a version of SMs

examples we have seen so far: PIM, iSLIP, iLQF

this is because of the following equivalence (will become clear later)

request = proposal

grant and accept = engagement

final matching = marriage

→ so it pays off hugely to understand the SMs

EE384X Packet Switch Architectures I 9

The Stable Marriage Problem (SMP)

• Some historical context

hospitals and residents

Gale and Shapley (1962): College admissions and the stability of marriage

Knuth (1976): Mariages Stables; et leurs relations avec d’autres problmes combinatoires

Gusfield and Irving (1989): The Stable Marriage Problem: Structure and Algorithms

• The SMP finds “stable” matchings in bipartite graphs

there are N women and N men

each woman (man) ranks each man (woman) in order of preference for marriage

Man # Preference list

1 1 2 3 4

2 2 1 4 3

3 3 2 4 1

4 3 4 2 1

Woman # Preference list

1

2

1

3

3

4

4

1

2

2

3

4

2 1 4 3

1 2 3 4

EE384X Packet Switch Architectures I 10

The Gale-Shapley Algorithm (GSA)

• What is a stable matching?

a matching is a pairing ( i, p ( i )) of i with their partner p ( i )

an unstable matching is one in which there are matched pairs ( i, p ( i ) ) and ( j, p ( j ) ) such that i prefers p ( j ) to p ( i ) , and p ( j ) prefers i to j

if this happens, i and p ( j ) are said to be a “blocking pair”

a stable matching has no blocking pairs

• High-level observations about GSA

it is iterative and proceeds in a series of proposals and (tentative) accepts

(works almost exactly as you’d think it ought to)

upon termination it returns matched pairs ( i, p ( i ) )

the matching is guaranteed to be “stable”

→ note that stable matchings exist for every set of ranking lists

EE384X Packet Switch Architectures I 11

GSA

• Terminology: During the execution of GSA, each person is free: if they are not engaged or matched to any other person engaged: if they are temporarily matched matched: if they are terminally matched (hooked, booked and cooked)

EE384X Packet Switch Architectures I 12

EE384X Packet Switch Architectures I

BEGIN

All are free

Is some man m free

?

Yes

No m proposes to w, who is the first woman he has not yet proposed to

END w engaged to m

Yes Is w free

?

No w currently engaged to m’ m continues to be free

No

Does w prefer m to m’

?

Yes match w and m set m’ free

13

An example

• Consider the example we have already seen

Man # Preference list

1 1 2 3 4

2 2 1 4 3

3 3 2 4 1

4 3 4 2 1

Woman # Preference list

1 1 3 4 2

2

3

4

3

2

1

4

1

2

1

4

3

2

3

4

• Executing GSA...

with men proposing we get the matching

(1,1), (2,4), (3,2), (4,3) - this takes 7 proposals (iterations)

with women proposing we get the matching

(1,1), (2,3), (3,2), (4,4) - this takes 7 proposals (iterations)

both matchings are stable (check)

the first is man-optimal - men get the best partners of any stable matching

likewise the second is woman-optimal

note: there are multiple stable matchings

EE384X Packet Switch Architectures I 14

GSA: Properties (assume men propose)

• Convergence

guaranteed, because women get better and bettter proposals

(men make worse and worse proposals)

due to this monotonicity and the finiteness of N we get convergence

(see lecture notes for more complete argument)

• GSA finds stable matchings

straightforward, see lecture notes

• Multiple stable matchings possible, as already seen

• Lattice ordering

John Conway made the cool observation that the set of all stable matchings is a “distributive lattice”

in particular, this means you can take any two stable matchings and find two other stable matchings

EE384X Packet Switch Architectures I 15

• An aside: A distributive lattice is a set S with a partial order, , such that

each pair of elements a and b has a meet , or greatest lower bound, l such that l a and l b ; the meet is denoted by l = a ∧ b

each pair of elements a and b has a join , or least lower bound, u such that a u and b u ; the join is denoted by u = a ∨ b

the distributive laws hold: (i) a ∨ ( b ∧ c ) = ( a ∨ b ) ∧ ( a ∨ c ) , and (ii) a ∧ ( b ∨ c ) = ( a ∧ b ) ∨ ( a ∧ c )

• A well-known example: S equal the set of all subsets of { 1 , 2 , . . . , K }

the partial order: set inclusion ( ⊂ )

the meet: for a, b ∈ S , let l = a ∧ b = a ∩ b

the join: for a, b ∈ S , let u = a ∨ b = a ∪ b

fun exercise: show S is a distributive lattice under the partial order: ⊂

EE384X Packet Switch Architectures I 16

• For stable matchings

the partial order: stable matching M dominates stable matching M

0 , or M

0 woman prefers M to M

0

M , if each

the meet: l = M ∧ M

0 is that matching obtained by giving each woman the worse of her partners in the two matchings

the join: u = M ∨ M 0 is that matching obtained by giving each woman the better of her partners in the two matchings

fun exercise: show that this is a distributive lattice

EE384X Packet Switch Architectures I 17