Lecture #22 MOSFET Terminals

advertisement

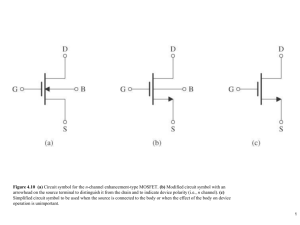

Lecture #22 ANNOUNCEMENTS • Contact Dave Nguyen (nguyendt@uclink) if you lost a calculator in the lab • The EECS40 Course Reader (containing supplemental reading from Schwarz & Oldham) is now available at Copy Central, 2483 Hearst Ave. • Try the educational applets available online! (Visit the class website.) OUTLINE – The MOSFET as a controlled resistor – Pinch-off and current saturation – Channel-length modulation – Velocity saturation in a short-channel MOSFET Reference Reading » Rabaey et al.: Chapter 3.3.2 » Schwarz & Oldham: Chapter 13.4 » Howe & Sodini: Chapter 4.3 EECS40, Fall 2003 Lecture 22, Slide 1 Prof. King MOSFET Terminals • The voltage applied to the GATE terminal determines whether current can flow between the SOURCE & DRAIN terminals. – For an n-channel MOSFET, the SOURCE is biased at a lower potential (often 0 V) than the DRAIN (Electrons flow from SOURCE to DRAIN when VG > VT) – For a p-channel MOSFET, the SOURCE is biased at a higher potential (often the supply voltage VDD) than the DRAIN (Holes flow from SOURCE to DRAIN when VG < VT ) • The BODY terminal is usually connected to a fixed potential. – For an n-channel MOSFET, the BODY is connected to 0 V – For a p-channel MOSFET, the BODY is connected to VDD EECS40, Fall 2003 Lecture 22, Slide 2 Prof. King 1 MOSFET Circuit Symbols G NMOS G n+ poly-Si n+ n+ S S p-type Si G PMOS G p+ poly-Si p+ p+ S S n-type Si EECS40, Fall 2003 Lecture 22, Slide 3 Prof. King The MOSFET as a Controlled Resistor • The MOSFET behaves as a resistor when VDS is low: – Drain current ID increases linearly with VDS – Resistance RDS between SOURCE & DRAIN depends on VGS • RDS is lowered as VGS increases above VT oxide thickness ≡ tox NMOSFET Example: ID VGS = 2 V VGS = 1 V > VT VDS IDS = 0 if VGS < VT EECS40, Fall 2003 Inversion charge density Qi(x) = -Cox[VGS-VT-V(x)] where Cox ≡ εox / tox Lecture 22, Slide 4 Prof. King 2 Sheet Resistance Revisited Consider a sample of n-type semiconductor: V I _ + W t homogeneously doped sample L Rs = ρ t = 1 1 1 = = σt qµn nt µnQn where Qn is the charge per unit area EECS40, Fall 2003 Lecture 22, Slide 5 Prof. King MOSFET as a Controlled Resistor (cont’d) ID = V DS R DS R DS = R s ( L / W ) = L /W L /W = µ n Qi µ C (V − V − V DS ) n ox GS T 2 V W I D = µnCox (VGS − VT − DS )VDS L 2 average value of V(x) We can make RDS low by • applying a large “gate drive” (VGS − VT) • making W large and/or L small EECS40, Fall 2003 Lecture 22, Slide 6 Prof. King 3 Charge in an N-Channel MOSFET VGS < VT: depletion region (no inversion layer at surface) VGS > VT : VDS ≈ 0 I D = WQinv v = WQ inv µ n E V = WQ inv µ n DS L VDS > 0 (small) Average electron velocity v is proportional to lateral electric field E EECS40, Fall 2003 Lecture 22, Slide 7 Prof. King What Happens at Larger VDS? VGS > VT : Inversion-layer is “pinched-off” at the drain end VDS = VGS–VT VDS > VGS–VT As VDS increases above VGS–VT ≡ VDSAT, the length of the “pinch-off” region ∆L increases: • “extra” voltage (VDS – VDsat) is dropped across the distance ∆L • the voltage dropped across the inversion-layer “resistor” remains VDsat ⇒ the drain current ID saturates Note: Electrons are swept into the drain by the E-field when they enter the pinch-off region. EECS40, Fall 2003 Lecture 22, Slide 8 Prof. King 4 Summary of ID vs. VDS • As VDS increases, the inversion-layer charge density at the drain end of the channel is reduced; therefore, ID does not increase linearly with VDS. • When VDS reaches VGS − VT, the channel is “pinched off” at the drain end, and ID saturates (i.e. it does not increase with further increases in VDS). + – VGS VDS > VGS - VT G I DSAT = µ nCox D S n+ - VGS - VT + W (VGS − VT )2 2L n+ pinch-off region EECS40, Fall 2003 Lecture 22, Slide 9 Prof. King ID vs. VDS Characteristics The MOSFET ID-VDS curve consists of two regions: 1) Resistive or “Triode” Region: 0 < VDS < VGS − VT V W VGS − VT − DS VDS L 2 where k n′ = µ n C ox I D = k n′ process transconductance parameter 2) Saturation Region: VDS > VGS − VT k n′ W (VGS − VT )2 2 L where k n′ = µ n C ox I DSAT = EECS40, Fall 2003 “CUTOFF” region: VG < VT Lecture 22, Slide 10 Prof. King 5 Channel-Length Modulation If L is small, the effect of ∆L to reduce the inversion-layer “resistor” length is significant → ID increases noticeably with ∆L (i.e. with VDS) ID ID = ID′(1 + λVDS) λ is the slope ID′ is the intercept VDS EECS40, Fall 2003 Lecture 22, Slide 11 Prof. King Current Saturation in Modern MOSFETs • In digital ICs, we typically use transistors with the shortest possible gate-length for high-speed operation. • In a very short-channel MOSFET, ID saturates because the carrier velocity is limited to ~107 cm/sec v is not proportional to E, due to velocity saturation EECS40, Fall 2003 Lecture 22, Slide 12 Prof. King 6 Consequences of Velocity Saturation 1. ID is lower than that predicted by the mobility model 2. ID increases linearly with VGS − VT rather than quadratically in the saturation region V I DSAT = WCox VGS − VT − DSAT vsat 2 L where VDSAT = vsat µn EECS40, Fall 2003 Lecture 22, Slide 13 Prof. King P-Channel MOSFET ID vs. VDS • As compared to an n-channel MOSFET, the signs of all the voltages and the currents are reversed: Short-channel PMOSFET I-V Note that the effects of velocity saturation are less pronounced than for an NMOSFET. Why is this the case? EECS40, Fall 2003 Lecture 22, Slide 14 Prof. King 7