7.BJT Amps. for Undistorted VoltageSwing-X.nb

advertisement

à

7. DESIGN OF AC-COUPLED BJT AMPLIFIERS FOR MAXIMUM

UNDISTORTED VOLTAGE SWING

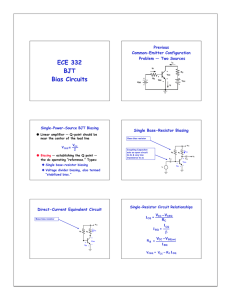

Figure 1. AC coupled common emitter amplifier circuit

ü The DC Load Line

VCC = RC ICQ + VCEQ + RE IEQ

IEQ = ICQ + IBQ

ICQ = bEFF .IBQ

HbEFF + 1L

IEQ = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ .ICQ > ICQ

bEFF

These equations lead to a linear relationship between ICQ and VCEQ which is imposed on the DC operating

point of the transistor by the circuit.

HbEFF + 1L y

i

VCC = jjRC + RE ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ zz.ICQ + VCEQ

k

bEFF

{

or,

1 y

i

ICQ = HVCC - VCEQ L ì ARC + RE jj1 + ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ zzE

k

bEFF {

the "DC Load Line Equation"

7.BJT Amps. for Undistorted VoltageSwing-X.

2

Slope of DC Load Line :

DICQ

1 y -1

i

ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ = - ARC + RE jj1 + ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ zzE > -@RC + RE D-1

DVCEQ

k

bEFF {

Figure 2. shows the DC load line of the circuit drawn on the collector characteristics of an NPN transistor.

Figure 2. Collector characteristics of an NPN transistor and the DC load line

ü AC Load Line

DiC = f HDvCE L

DvCE = DvOUT

Assumptions:

(1) The capacitors are all large enough to hold the voltage across their terminals constant during the signal's

period,

(2) Therefore, the operating point QHICQ , VCEQ ) remains constant independent of the amplitude of the signal

fluctuations in currents and voltages.

If that is the case, the capacitors in the circuit can be taken to behave like DC voltage sources as shown in

Figure 3.

7.BJT Amps. for Undistorted VoltageSwing-X.nb

Figure 3. Behavioral equivalent of the common emitter stage with very large capacitors

DvCE = DvC - DvE

and

DiC = DiRC + DiRL ,

DvE = 0 constant

DvC

i VCC - vC y

DiRC = D jj ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ zz = - ÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

k

RC

RC

{

DvOUT

DiRL = - ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

DvOUT = vC - VCQ = DvC

RL

But,

DvC = D HvCE + VEQ L = DvCE

\

DvC

î DiRL = - ÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

RL

DvCE

DvCE

DiC = - ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ - ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

RC

RL

1 y

i 1

DiC = - jj ÄÄÄÄÄÄÄÄÄÄ + ÄÄÄÄÄÄÄÄÄÄ zz DvCE

which defines the "AC load line"

k RC

RL {

1 y

1

i 1

Slope of AC Load Line ∫ jj ÄÄÄÄÄÄÄÄÄÄ + ÄÄÄÄÄÄÄÄÄÄ zz ∫ ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

RL { HRC ˛ RL L

k RC

or,

For smaller signals the resistance seen by the transistor at its collector can be found by employing the small sig

ac equivalent of the circuit (given in Figure 4) is the same, i.e. (RC êê RL ), which confirms the slope calcula

above.

7.BJT Amps. for Undistorted VoltageSwing-X.

4

Figure 4. Resistance seen by the collector during small signal operation

In Figure 2. both AC and DC load lines are shown as drawn on the collector characteristics of an NPN transi

Note that both of the lines have to pass through the operating point, Q. The AC load line defines the rang

collector the current and voltage swings that can take place around the operating point, the range limited on the

by the saturation region of the transistor characteristics and on the right by its cut-off point. If the swings ten

exceed these limits, the waveform is clipped, creating severe distortion in the amplified signal. The undisto

(unclipped) voltage swing is restricted to ∆vMAX+ and ∆vMAX+ around the operating point. (See Figure 5.)

1.

DvMAX+ = DvMAX-

2.

DvMAX+ = RAC .ICQ

AC load line resistance ∫ RAC = HRC ˛ RL L

DvMAX+ = VCEQ - vCESAT

7.BJT Amps. for Undistorted VoltageSwing-X.nb

Figure 5. AC load line and the maximum undistorted output swing

7.BJT Amps. for Undistorted VoltageSwing-X.

6

ü

7.1 DESIGN OF COMMON EMITTER BJT AMPLIFIERS FOR MAXIMUM UNDISTORTED

VOLTAGE SWING

Rewriting the maximum peak undistorted swing conditions from above and using the condition of equal

symmetric undistorted swings around the operating point an equation for maximum swing can be derived as

shown below.

1. DvMAX = DvMAX+ = DvMAX2. DvMAX = RAC .ICQ

Æ

DvMAX

ICQ = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

RAC

3. DvMAX = VCEQ - VCESAT

Æ

VCEQ = DvMAX + VCESAT

4. VCC = VEQ + VCEQ + RC ICQ

Equations H2L and H3L when substituted in Equation H4L

RC

VCC = VEQ + DvMAX + VCESAT + DvMAX. ÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

RAC

H5. aL

RC y

i

DvMAX jj1 + ÄÄÄÄÄÄÄÄÄÄÄÄÄÄ zz = VCC - VEQ - VCESAT

k

RAC {

or,

H5. bL

RC y

i

DvMAX jj2 + ÄÄÄÄÄÄÄÄÄÄ zz = VCC - VEQ - VCESAT

k

RL {

1

1

1

since ÄÄÄÄÄÄÄÄÄÄÄÄÄÄ = ÄÄÄÄÄÄÄÄÄÄ + ÄÄÄÄÄÄÄÄÄÄ

RAC

RC

RL

Equations 5.a and 5.b can be used as design guides to achieve a specified amount of symmetric undistorted

voltage swings at the output of a common-emitter amplifier.

Note that the maximum undistorted peak swing, ∆vMAX cannot be greater than %50 of VCC even under the most

favorable conditions of no load and no emitter drop, VEQ .