Zero-current switching

advertisement

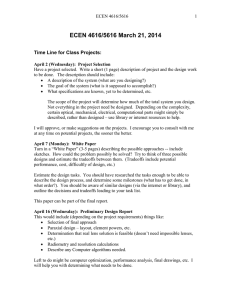

19.3 Soft switching in resonant converters Soft switching can mitigate some of the mechanisms of switching loss and possibly reduce the generation of EMI Losses due to high voltage and high current present in switch during transitions, e.g. due to diode reverse recovery Losses due to shorting device capacitances Semiconductor devices are switched on or off at the zero crossing of their voltage or current waveforms: Zero-current switching: transistor turn-off transition occurs at zero current. Zerocurrent switching eliminates the switching loss caused by IGBT current tailing and by stray inductances. It can also be used to commutate SCR’s. Zero-voltage switching: transistor turn-on transition occurs at zero voltage. Diodes may also operate with zero-voltage switching. Zero-voltage switching eliminates the switching loss induced by diode stored charge and device output capacitances. Zero-voltage switching is usually preferred in converters based on MOSFETs ECEN 5817 1 19.3.1 Operation of the full bridge below resonance: Zero-current switching Series resonant converter example + Q1 vds1(t) D1 Q3 L + iQ1(t) – Vg C D3 + – vs(t) Q2 D2 Q4 – is(t) D4 Current bi-directional switches ZCS vs. ZVS depends on tank current zero crossings with respect to transistor switching times = tank voltage zero crossings Operation below resonance: input tank current leads voltage Zero-current switching (ZCS) occurs 2 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Tank input impedance Operation below resonance: tank input impedance Zi is dominated by tank capacitor. ∠Zi is negative, and tank input current leads tank input voltage. || Zi || 1 ωC ωL f0 R0 Qe = R0 /Re Re Zero crossing of the tank input current waveform is(t) occurs before the zero crossing of the voltage vs(t) – before switch transitions ECEN 5817 3 Switch network waveforms, below resonance Zero-current switching + Q1 vds1(t) D1 Q3 L C D3 + iQ1(t) – vs(t) Q2 D2 Q4 – is(t) D4 Conduction sequence: Q1–D1–Q2–D2 Q1 is turned off during D1 conduction interval, without loss (same for Q4/D4) Q2 is turned off during D2 conduction interval, without loss (same for Q3/D3) 4 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Turn-on transitions: significant switching losses + Q1 vds1(t) D1 Q3 L C D3 + iQ1(t) – vs(t) Q2 D2 Q4 – is(t) D4 Q1 turns on while D2 is conducting. Stored charge of D2 and of semiconductor output capacitances must be removed. Transistor turn-on transition is identical to hardswitched PWM, and switching loss occurs. 5 ECEN 5817 More on Diode Stored Charge and Reverse Recovery Typical test circuit and parameter definitions in diode data sheets 6 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Diode stored charge during recovery 7 ECEN 5817 “Snappy” and “soft-recovery” diodes Also see textbook Section 4.3.2 and HW 1 problem 3 solution 8 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Example Diode in IRGP50B60 (IGBT+diode): ultra-fast, “soft recovery” Reverse recovery time trr, maximum reverse recovery current IRRM, and reverse recovery charge Qrr depend on diode forward current IF prior to turn off, rate of current decay dif/dt, and junction temperature TJ ECEN 5817 9 Review of HW1 problem 3 example iL = I D iLs L it + – M + _ + its vds g id Ls Ms gs Ds V ids C _ g t gs t Ts 10 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 19.3.2 Operation of the full bridge above resonance: zero-voltage switching Series resonant converter example + Q1 vds1(t) D1 Q3 L + iQ1(t) – Vg C D3 + – vs(t) Q2 D2 Q4 – is(t) D4 Operation above resonance: input tank current lags voltage Zero-voltage switching (ZVS) occurs ECEN 5817 11 Tank input impedance Operation above resonance: tank input impedance Zi is dominated by tank inductor. ∠Zi is positive, and tank input current lags tank input voltage. || Zi || 1 ωC ωL R0 Re f0 Qe = R0 /Re Zero crossing of the tank input current waveform is(t) occurs after the zero crossing of the voltage vs(t) – after switch transitions 12 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Switch network waveforms, above resonance Zero-voltage switching + Q1 D1 vds1(t) Q3 L C D3 + iQ1(t) – vs(t) Q2 Q4 D2 is(t) – D4 Conduction sequence: D1–Q1–D2–Q2 Q1 is turned on during D1 conduction interval, without loss ZVS turn-on transitions for all transistors Turn-off transitions are at non-zero current ECEN 5817 13 Turn-off transition at non-zero current: hard switching? + Q1 vds1(t) D1 Q3 L C D3 + iQ1(t) – vs(t) Q2 D2 Q4 – is(t) D4 When Q1 turns off, D2 must begin conducting. Voltage across Q1 must increase to Vg. Transistor turn-off transition is identical to hard-switched PWM. Switching loss may occur, but … 14 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Soft switching at the turn-off transition + Q1 D1 C leg Vg vds1(t) – Q3 Cleg D3 is(t) + – vs(t) Q2 D2 Cleg L + to remainder of converter Cleg D4 – Q4 vds1(t) Conducting devices: Turn off Q1, Q4 X D2 D3 • Introduce delay between turn-off of Q1 and turn-on of Q2. Tank current is(t) charges and discharges Cleg. Turn-off transition becomes lossless. During commutation interval, no devices conduct. Vg Q1 Q4 • Introduce small capacitors Cleg across each device (or use device output capacitances). So zero-voltage switching exhibits low switching loss: losses due to diode stored charge and device output capacitances are eliminated. t Commutation interval Note: with IGBTs, substantial Cleg may be required 15 ECEN 5817 Resonant Inverter Design Applications: Resonant inverters for lamp ballasts DC-AC side of resonant DC-DC converters Resonant inverter design objectives: 1. Operate with a specified load characteristic and range of operating points • With a nonlinear load, must properly match inverter output characteristic to load characteristic 2. Obtain zero-voltage switching or zero-current switching • Preferably, obtain these properties at all loads • Could allow ZVS property to be lost at light load, if necessary 3. Minimize transistor currents and conduction losses • To obtain good efficiency at light load, the transistor current should scale proportionally to load current (in resonant converters, it often doesn’t!) 16 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 19.4 Load-dependent properties of resonant converters 17 ECEN 5817 Inverter output characteristics 18 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Inverter output characteristics 19 ECEN 5817 Inverter output characteristics This result is valid provided that (i) the resonant network is purely reactive, and (ii) the load is purely resistive. 20 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Matching output characteristic to application requirements Electronic ballast Electrosurgical generator 21 ECEN 5817 Input impedance of the resonant tank network Appendix C: Section C.4.4 Expressing the tank input impedance as a function of the load resistance R: where 22 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 ZN and ZD ZD is equal to the tank output impedance under the condition that the tank input source vs1 is open-circuited. ZD = Zo∞ ZN is equal to the tank output impedance under the condition that the tank input source vs1 is short-circuited. ZN = Zo0 23 ECEN 5817 Reciprocity 24 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Relations 25 ECEN 5817 26 ECEN 5817 ECEN5817, ECEE Department, University of Colorado at Boulder Relating transistor current variations to load resistance R Theorem 1: If the tank network is purely reactive, then its input impedance || Zi || is a monotonic function of the load resistance R. So as the load resistance R varies from 0 to ∞, the resonant network input impedance || Zi || varies monotonically from the short-circuit value || Zi0 || to the open-circuit value || Zi∞ ||. The impedances || Zi∞ || and || Zi0 || are easy to construct. If you want to minimize the circulating tank currents at light load, maximize || Zi∞ ||. Note: for many inverters, || Zi∞ || < || Zi0 || ! The no-load transistor current is therefore greater than the short-circuit transistor current. 27 ECEN 5817 Derivation 28 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Example: || Zi || of LCC • for f < f m, || Zi || increases with increasing R . • for f > f m, || Zi || decreases with increasing R . • at a given frequency f, || Zi || is a monotonic function of R. • It’s not necessary to draw the entire plot: just construct || Zi0 || and || Zi∞ ||. 29 ECEN 5817 Discussion: LCC LCC example || Zi0 || and || Zi∞ || both represent series resonant impedances, whose Bode diagrams are easily constructed. || Zi0 || and || Zi∞ || intersect at frequency fm. For f < fm then || Zi0 || < || Zi∞ || ; hence transistor current decreases as load current decreases For f > fm then || Zi0 || > || Zi∞ || ; hence transistor current increases as load current decreases, and transistor current is greater than or equal to short-circuit current for all R 30 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Discussion —series and parallel • No-load transistor current = 0, both above and below resonance. • ZCS below resonance, ZVS above resonance • Above resonance: no-load transistor current is greater than short-circuit transistor current. ZVS. • Below resonance: no-load transistor current is less than short-circuit current (for f <fm), but determined by || Zi∞ ||. ZCS. 31 19.4 ECEN 5817 Load-dependent properties of resonant converters Resonant inverter design objectives: 1. Operate with a specified load characteristic and range of operating points • With a nonlinear load, must properly match inverter output characteristic to load characteristic 2. Obtain zero-voltage switching or zero-current switching • Preferably, obtain these properties at all loads • Could allow ZVS property to be lost at light load, if necessary 3. Minimize transistor currents and conduction losses • To obtain good efficiency at light load, the transistor current should scale proportionally to load current (in resonant converters, it often doesn’t!) 32 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Relation between ZVS/ZCS boundary and load R Theorem 2: If the tank network is purely reactive, then the boundary between zerocurrent switching and zero-voltage switching occurs when the load resistance R is equal to the critical value Rcrit, given by It is assumed that zero-current switching (ZCS) occurs when the tank input impedance is capacitive in nature, while zero-voltage switching (ZVS) occurs when the tank is inductive in nature. This assumption gives a necessary but not sufficient condition for ZVS when significant semiconductor output capacitance is present. 33 ECEN 5817 Derivation 34 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Discussion —Theorem 2 Again, Zi∞, Zi0, and Zo0 are pure imaginary quantities. If Zi∞ and Zi0 have the same phase (both inductive or both capacitive), then there is no real solution for Rcrit. Hence, if at a given frequency Zi∞ and Zi0 are both capacitive, then ZCS occurs for all loads. If Zi∞ and Zi0 are both inductive, then ZVS occurs for all loads. If Zi∞ and Zi0 have opposite phase (one is capacitive and the other is inductive), then there is a real solution for Rcrit. The boundary between ZVS and ZCS operation is then given by R = Rcrit. Note that R = || Zo0 || corresponds to operation at matched load with maximum output power. The boundary is expressed in terms of this matched load impedance, and the ratio Zi∞ / Zi0. 35 ECEN 5817 LCC example f > f∞: ZVS occurs for all R f < f0: ZCS occurs for all R f0 < f < f∞, ZVS occurs for R< Rcrit, and ZCS occurs for R> Rcrit. Note that R = || Zo0 || corresponds to operation at matched load with maximum output power. The boundary is expressed in terms of this matched load impedance, and the ratio Zi∞ / Zi0. 36 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 LCC example, continued Typical dependence of Rcrit and matched-load impedance || Zo0 || on frequency f, LCC example. Typical dependence of tank input impedance phase vs. load R and frequency, LCC example. 37 ECEN 5817 19.4.4 Design Example Select resonant tank elements to design a resonant inverter that meets the following requirements: • • • • Switching frequency fs = 100 kHz Input voltage Vg = 160 V Inverter is capable of producing a peak open circuit output voltage of 400 V Inverter can produce a nominal output of 150 Vrms at 25 W 38 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Solve for the output characteristic (ellipse) that meets requirements ECEN 5817 39 Numerical values The required short-circuit current can be found by solving the elliptical output characteristic for Isc: hence Use the requirements to evaluate the above: 40 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Open circuit magnitude response The requirements imply that the inverter tank circuit have an open-circuit magnitude response: Note that Voc need not have been given as a requirement, we can solve the elliptical relationship, and therefore find Voc given any two required operating points of ellipse. E.g. Isc could have been a requirement instead of Voc 41 ECEN 5817 Solve for matched load (output impedance magnitude) Matched load therefore occurs at the operating point Hence the tank should be designed such that its output impedance is 42 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Solving for the tank elements to give required ||Zo0|| and ||Hinf|| Design an LCC tank network for this example The impedances of the series and shunt branches can be represented by the reactances 43 ECEN 5817 Analysis in terms of Xs and Xp The transfer function is given by the voltage divider equation: The output impedance is given by the parallel combination: Solve for Xs and Xp: 44 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Discussion Choice of series branch elements The series branch is comprised of two elements L and Cs, but there is only one design parameter: Xs = 733 Ω. Hence, there is an additional degree of freedom, and one of the elements can be arbitrarily chosen. This occurs because the requirements are specified at only one operating frequency. Any choice of L and Cs, that satisfies Xs = 733 Ω will meet the requirements, but the behavior at switching frequencies other than 100 kHz will differ. Given a choice for Cs, L must be chosen according to: For example, Cs = 3Cp = 3.2 nF leads to L = 1.96 mH 45 ECEN 5817 Rcrit For the LCC tank network chosen, Rcrit is determined by the parameters of the output ellipse, i.e., by the specification of Vg, Voc, and Isc. Note that Zo∞ is equal to jXp. One can find the following expression for Rcrit: Since Zo0 and H ∞ are determined uniquely by the operating point requirements, then Rcrit is also. Other, more complex tank circuits may have more degrees of freedom that allow Rcrit to be independently chosen. Evaluation of the above equation leads to Rcrit = 1466 Ω. Hence ZVS for R < 1466 Ω, and the nominal operating point with R = 900 Ω has ZVS. 46 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Ellipse again with Rcrit, Rmatched, and Rnom showing ZVS and ZCS 47 ECEN 5817 Converter performance For this design, the salient tank frequencies are (note that fs is nearly equal to fm, so the transistor current should be nearly independent of load) The open-circuit tank input impedance is So when the load is open-circuited, the transistor current is Similar calculations for a short-circuited load lead to 48 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817 Extending ZVS range 49 ECEN5817, ECEE Department, University of Colorado at Boulder ECEN 5817