pn Junction under Reverse Bias

advertisement

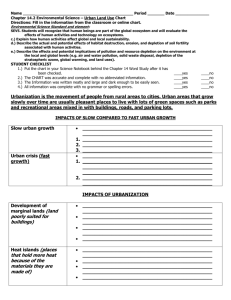

pn Junction under Reverse Bias ■ First, we must understand the complete structure of the pn junction-- starting in thermal equilibrium: ,,,, ,,,, − φpm + −Wp metal contact to p side p metal interconnection −xpo − φB + xno ,,,, ,,,, n Wn ■ − φmn + metal contact to n side How can VD = 0 and the built-in potential barrier be φB = 1 V (approx.)? Answer: look at the complete circuit ... including the potential barriers at the p-type silicon-to-metal (φpm) and the metal-to-n-type silicon (φmn) junctions. ■ KirchhoffÕs Voltage Law: 0 = φ pm + φ B + φ mn therefore, the built-in voltage is given by: φ B = Ð φ pm Ð φ mn EE 105 Spring 1997 Lecture 8 Potential Plot through pn Junction ■ The potential in the metal is the same on both ends of the pn junction in thermal equilibrium, with the metal-semiconductor contact potentials (ÒbatteriesÓ) cancelling out the built-in potential φo(x) φn −xpo −Wp − φpm + xno φB φp − + φmn Wn + x − (b) Note: we show potential changes at metal-silicon contacts as vertical, which is not correct. The details are left for an advanced device physics course. ■ Now we apply a battery VD ... with VD < 0 (reverse bias) −Wp ID ≈ 0 A VD (< 0 V) ,,,, ,,,, − φpm + ohmic contact to p side p + −xp − xn x Wn − φj + ,,,, ,,,, n − φmn + ohmic contact to n side EE 105 Spring 1997 Lecture 8 pn Junction under Reverse Bias (cont.) ■ Potential plot under reverse bias: contact potentials donÕt change ... they are ohmic contacts. Only place for change is at the pn junction (a) φ(x) −xp −Wp φn − + VD < 0 V − φpm + φj φp − + xn φmn Wn +x − (b) ■ The new potential barrier is called φj KVL: Ð V D Ð φ pm Ð φ j Ð φ mn = 0 φ j = ( Ð φ pm Ð φ mn ) Ð V D = φ B Ð V D ■ The potential barrier is increased over the built-in barrier by the reverse bias ... which widens the depletion region (xn > xno, xp > xpo) EE 105 Spring 1997 Lecture 8 −xp(−6.4) −xp(−2.4) ρ(x) −xp(0) +qNd n-side x p-side −qNa xn(0) xn(−2.4) x (−6.4) n (a) E(x) p-side −xp n-side xn x thermal equilibrium (VD = 0 V) VD = − 2.4 V VD = − 6.4 V qNd xn(VD) E(x = 0) = − εs (b) φ(x) thermal equilibrium (VD = 0 V, n-side φ = φ = 0.8 V) p-side B j x VD = − 2.4 V, φj = 3.2 V −2.4 V −2.5 V −6.4 V −5V VD = − 6.4 V, φj = 7.2 V − 7.5 V (c) EE 105 Spring 1997 Lecture 8 Quantitative Results ■ ■ Substitute φj for φB in the equilibrium depletion width and we Þnd the depletion width under reverse bias (the math is the same): x p(V D) = 2ε s ( φ B Ð V D ) N d ---------------------------------- -------------------- = x po 1 Ð ( V D ⁄ φ B ) qN a N d + N a x n(V D) = 2ε s ( φ B Ð V D ) N a ---------------------------------- -------------------- = x no 1 Ð ( V D ⁄ φ B ) qN d N d + N a X d(V D) = 2ε s ( φ B Ð V D ) 1 1 --------------------------------- ------- + ------- = X do 1 Ð ( V D ⁄ φ B ) N q N a d Note xpo, xno, and Xdo are the widths in thermal equilibrium EE 105 Spring 1997 Lecture 8 Capacitance ■ Basic circuits: C = Q / V ... linear capacitor ■ Semiconductor devices: C = dq / dv ... nonlinear charge-storage --> capacitance is deÞned as a small signal quantity vd + _ VD < 0 V + _ ,,,,, p qJ = QJ + qj − − − − −− − − − − − ++++++++++ ,,,,, n (a) +qj vd + _ Cj = Cj (VD) −qj (b) Symbols: * break up the total applied voltage (symbol: vD) into two parts: total voltage = DC voltage + small-signal voltage vD = VD + vd * break up the charge qJ on the p-side of the junction similarly: total charge in the depletion region = DC charge + small-signal charge qJ = QJ + qj EE 105 Spring 1997 Lecture 8 Depletion Capacitance ■ Find the function qJ = qJ(vD) from xp(vD): q J(v D) = Ð qN a x p(v D) = Ð qN a x po 1 Ð ( v D ⁄ φ B ) ■ Normalized plot: −14 −12 −10 −8 −6 −4 −2 qJ |qJo| vD / φB −1 −2 −3 −4 −5 ■ To Þnd the depletion capacitance Cj we simply take the derivative and evaluate it at the particular DC voltage dq J C j = C j(V D) = ---------dv D VD ■ Math --> no insight into the concept of capacitance! EE 105 Spring 1997 Lecture 8 Graphical Interpretation ■ Derivative is the slope of the plot of qJ(vD): −14 −12 −10 −8 −6 −4 −2 qJ |qJo| vD / φB −1 −2 −3 −4 −5 ■ The small-signal charge is related to the small-signal voltage by the slope at point (QJ, VJ): dq J q j = --------- dv D ⋅ v d = C j(V D) ⋅ v d VD EE 105 Spring 1997 Lecture 8 Physical Interpretation ■ Small-signal voltage changes the depletion width (vd > 0 --> reverse bias is reduced --> depletion width is slightly narrower) ρ(x) p-side (a) −xp +qNd n-side x xn vD = VD −qNa QJ = −qNaxp ρ(x) +qNd p-side −x −x p p (b) n-side x xn xn vD = VD + vd > VD--> xp < xp,| qJ | < | QJ | −qNa qJ = −qNaxp qj = qNa∆xp ∆ρ(x) = ρ(x) − ρ(x) + qNd Xd p-side (c) xn xn −xp −xp qj = qj − Qj > 0 = −qNaxp − (−qNaxp) = qNa (xp −xp) = qNa∆xp n-side x − qNa −qj = −qNd ∆xn EE 105 Spring 1997 Lecture 8 Depletion Capacitance Equation ■ Derivative can be evaluated (see Chapter 3), but the incremental charge is two sheets separated by a distance Xd(VD) --> use parallel plate capacitor formula: C jo εs qj εs C j = ----- = ------------------- = ------------------------------------------ = ------------------------------vd X d(V D) X do 1 Ð V D ⁄ φ B 1 Ð V D ⁄ φB ■ Plot of depletion capacitance (normalized to Cjo): Cj /Cjo 1 0.75 0.5 0.25 −14 −12 −10 −8 −6 −4 −2 0 VD /φB Typical numbers: Xdo = 0.4 µm --> Cjo = 2.6 x 10-8 F/cm2 = 0.26 fF/µm2 φB = 0.8 V --> VD = - 6.4 V = - 8 φB --> (1 - VD / φB)1/2 = 3 --> Cj = Cjo / 3 = 86 aF/µm2 EE 105 Spring 1997 Lecture 8