High Speed Buffer Amplifier

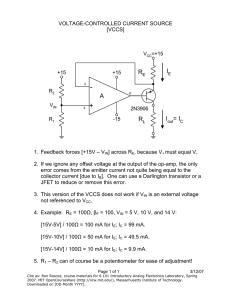

advertisement

OPA633 ® High Speed BUFFER AMPLIFIER FEATURES APPLICATIONS ● ● ● ● ● ● ● ● WIDE BANDWIDTH: 260MHz HIGH SLEW RATE: 2500V/µs HIGH OUTPUT CURRENT: 100mA LOW OFFSET VOLTAGE: 1.5mV OP AMP CURRENT BOOSTER VIDEO BUFFER LINE DRIVER A/D CONVERTER INPUT BUFFER ● REPLACES HA-5033 ● IMPROVED PERFORMANCE/PRICE: LH0033, LTC1010, H0S200 DESCRIPTION +VS The OPA633 is a monolithic unity-gain buffer amplifier featuring very wide bandwidth and high slew rate. A dielectric isolation process incorporating both NPN and PNP high frequency transistors achieves performance unattainable with conventional integrated circuit technology. Laser trimming provides low input offset voltage. High output current capability allows the OPA633 to drive 50Ω and 75Ω lines, making it ideal for RF, IF and video applications. Low phase shift allows the OPA633 to be used inside amplifier feedback loops. OPA633 is available in a low cost plastic DIP package specified for 0°C to +75°C operation. 1 VIN VOUT 4 8 –VS 5 SBOS150 International Airport Industrial Park • Mailing Address: PO Box 11400 Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132 © PDS-699B 1987 Burr-Brown Corporation Printed in U.S.A. October, 1993 SPECIFICATIONS ELECTRICAL At +25°C, VS = ±12V, RS = 50Ω, RL = 100Ω, and CL = 10pF, unless otherwise specified. OPA633KP PARAMETER CONDITIONS FREQUENCY RESPONSE Small Signal Bandwidth Full Power Bandwidth Slew Rate Rise Time, 10% to 90% Propagation Delay Overshoot Settling Time, 0.1% Differential Phase Error (1) Differential Gain Error (1) Total Harmonic Distortion MIN VO = 1Vrms, RL = 1kΩ VO = 10V, VS = ±15V, RL = 1kΩ VO = 500mV TA = TMIN to TMAX RL = 1kΩ, VS = ±15V Current Resistance TRANSFER CHARACTERISTICS Gain RL = 1kΩ TA = TMIN to TMAX INPUT Offset Voltage ±8 ±11 ±80 ±10 ±13 ±100 5 V V mA Ω 0.93 0.95 0.99 0.95 V/V V/V V/V 1000 0.92 TA = TMIN to TMAX TA = +25°C TA = TMIN to TMAX 10Hz to 1MHz Noise Voltage Resistance Capacitance POWER SUPPLY Rated Supply Voltage Operating Supply Voltage Current, Quiescent 54 Specified Performance Derated Performance IO = 0 IO = 0, TA = TMIN to TMAX ±5 ±5 ±6 ±33 72 ±15 ±20 20 1.5 1.6 ±12 21 21 TEMPERATURE RANGE Specification, Ambient Operating, Ambient θ Junction, Ambient UNITS MHz MHz V/µs ns ns % ns Degrees % % % TA = +25°C TA = TMIN to TMAX vs Temperature vs Supply Bias Current MAX 260 40 2500 2.5 1 10 50 0.1 0.1 0.005 0.02 VO = 1Vrms, RL = 1kΩ, f = 100kHz VO = 1Vrms, RL = 100Ω, f = 100kHz OUTPUT CHARACTERISTICS Voltage TYP 0 –25 ±15 ±25 mV mV µV/°C dB µA µA µVp-p MΩ pF ±35 ±50 V V mA mA ±16 25 30 °C °C °C/W +75 +85 90 NOTE: (1) Differential phase error in video transmission systems is the change in phase of a color subcarrier resulting from a change in picture signal from blanked to white. Differential gain error is the change in amplitude at the color subcarrier frequency resulting from a change in picture signal from blanked to white. PIN CONFIGURATION ABSOLUTE MAXIMUM RATINGS Power Supply, ±VS ............................................................................ ±20V Input Voltage VIN ...................................................... +VS + 2V to –VS – 2V Output Current (peak) ................................................................... ±200mA Internal Power Dissipation (25°C) .................................................... 1.95W Junction Temperature ...................................................................... 200°C Storage Temperature Range ............................................ –40°C to +85°C Lead Temperature (soldering, 10s) .................................................. 300°C Top View +VS 1 8 Out NC 2 7 NC NC 3 6 Substrate (ground) In 4 5 –VS PACKAGE INFORMATION(1) MODEL OPA633KP OPA633KP PACKAGE TEMPERATURE RANGE 8-Pin Plastic DIP 0°C to +75°C ® OPA633 PACKAGE DRAWING NUMBER 8-Pin Plastic DIP 006 NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book. ORDERING INFORMATION MODEL PACKAGE 2 TYPICAL PERFORMANCE CURVES At +25°C, VS = ±12V, RS = 50Ω, RL = 100Ω, and CL = 10pF, unless otherwise specified. SMALL SIGNAL BANDWIDTH vs TEMPERATURE GAIN/PHASE vs FREQUENCY 300 6 4 290 VS = ±15V Gain (dB) θ –2 –20 θ –4 –40 –60 –6 –8 RS = 300Ω –10 RS = 50Ω Phase (degrees) 0 0 Bandwidth (MHz) 2 –80 270 VS = ±5V 260 VO = 0.25Vrms RL = 100Ω 250 –100 240 –120 –12 10 280 100 –50 1000 –25 0 RS = 1kΩ 5 2.0 4 Sine Wave Square Wave RL = 100Ω 3 2.5 3 2 2 (See Text) 1 Power Dissipation (W) Output Voltage (Vp-p) RL = 100Ω 6 Output Voltage (Vrms) 6 4 50 75 100 125 100 125 MAXIMUM POWER DISSIPATION vs AMBIENT TEMPERATURE SAFE INPUT VOLTAGE vs FREQUENCY 5 25 Temperature (°C) Frequency (MHz) 1.5 1.0 0.5 1 0 0 0 1 10 –50 100 –25 0 25 50 75 Ambient Temperature (°C) Frequency (MHz) SLEW RATE vs LOAD CAPACITANCE SLEW RATE vs LOAD CAPACITANCE 3500 3000 Rising Edge 2500 2500 Falling Edge Slew Rate (V/µs) Slew Rate (V/µs) 3000 2000 VO = ±10V RL = 1kΩ 1500 1000 2000 1500 VO = ±10V RL = 100Ω 1000 500 500 0 0 1 10 100 1000 1 Load Capacitance (pF) 10 100 1000 10,000 Load Capacitance (pF) ® 3 OPA633 TYPICAL PERFORMANCE CURVES (CONT) At +25°C, VS = ±12V, RS = 50Ω, RL = 100Ω, and CL = 10pF, unless otherwise specified. POWER SUPPLY REJECTION vs FREQUENCY SLEW RATE vs TEMPERATURE 80 2500 Falling Edge RL = 1kΩ 70 60 Rising Edge PSRR (dB) Slew Rate (V/µs) 2000 1500 Falling Edge 1000 RL = 100Ω Rising Edge 50 40 30 20 500 10 0 0 –50 –25 0 25 50 75 100 1k 125 10k Temperature (°C) 1M INPUT BIAS CURRENT vs TEMPERATURE QUIESCENT CURRENT vs TEMPERATURE 25 30 VS = ±15V 25 20 VS = ±12V VS = ±5V 20 IB (µA) Quiescent Current (mA) 100k Frequency (Hz) 15 VS = ±5V 15 10 10 5 VS = ±15V 0 5 –50 –25 0 25 50 75 100 –50 125 –25 0 OUTPUT VOLTAGE SWING vs LOAD RESISTANCE 30 25 50 75 100 125 Temperature (°C) Temperature (°C) VIN – VOUT vs OUTPUT CURRENT 1.0 VS = ±15V VS = ±12V 20 VS = ±10V 0.8 VIN – VOUT (V) VOUT (Vp-p) 0.9 25 15 10 VS = ±5V 0.5 0.4 0 0.1 0 300 400 500 600 700 800 900 1k Current Sinking VO = 0 Current Sourcing 0 Load Resistance (Ω) 10 20 30 40 50 60 Output Current (mA) ® OPA633 VO = 0 0.3 0.2 100 200 VO = +10 0.6 5 0 VO = –10 0.7 4 70 80 90 100 TYPICAL PERFORMANCE CURVES (CONT) At +25°C, VS = ±12V, RS = 50Ω, RL = 100Ω, and CL = 10pF, unless otherwise specified. VOLTAGE GAIN vs LOAD RESISTANCE GAIN ERROR vs TEMPERATURE 100 1.00 VO = 10Vp-p VO – VIN (mV) Voltage Gain (V/V) 80 VO = 1Vp-p 0.95 0.90 f = 1kHz VO = ±10V RL = 1kΩ 60 40 0.85 20 0 0.80 10 100 1k –50 10k –25 0 OUTPUT ERROR vs INPUT VOLTAGE 100 0 –20 RL = 10kΩ VOS (mV) 20 RL = 1kΩ 0 2 0 –0.4 –40 –0.6 –60 –2 –0.8 –1.0 –80 –100 –4 –10 –8 –6 –4 –2 0 125 4 VIN – VOUT (mV) VIN – VOUT (V) 40 0.2 –0.2 100 6 60 RL = 50Ω 0.4 75 80 RL = 100Ω 0.6 50 OFFSET VOLTAGE vs TEMPERATURE 1.0 0.8 25 Temperature (°C) Load Resistance (Ω) 2 4 6 8 10 –50 Input Voltage (V) –25 0 25 50 75 100 125 Temperature (°C) TOTAL HARMONIC DISTORTION vs FREQUENCY TOTAL HARMONIC DISTORTION vs OUTPUT VOLTAGE 0.06 1.0 0.05 VO = 1Vrms RL = 100Ω 0.04 THD (%) THD (%) 0.1 f = 1kHz RL = 100Ω 0.03 0.02 0.01 0.01 0 0.001 0 0.5 1.0 1.5 2.0 2.5 100 3.0 Output Voltage (Vrms) 1k 10k 100k Frequency (Hz) ® 5 OPA633 APPLICATIONS INFORMATION input voltage versus frequency curves. When used to buffer an op amp’s output, the input to the OPA633 is limited, in most cases, by the op amp. When high frequency inputs can exceed safe levels, the device must be protected by limiting the power supply current. As with any high frequency circuitry, good circuit layout technique must be used to achieve optimum performance. Power supply connections must be bypassed with high frequency capacitors. Many applications benefit from the use of two capacitors on each power supply—a ceramic capacitor for good high frequency decoupling and a tantalum type for lower frequencies. They should be located as close as possible to the buffer’s power supply pins. A large ground plane is used to minimize high frequency ground drops and stray coupling. PROTECTION CIRCUITS The OPA633 can be protected from damage due to excessive currents by the simple addition of resistors in series with the power supply pins (Figure 5a). While this limits output current, it also limits voltage swing with low impedance loads. This reduction in voltage swing is minimal for AC or high crest factor signals since only the average current from the power supply causes a voltage drop across the series resistor. Short duration load-current peaks are supplied by the bypass capacitors. Pin 6 connects to the substrate of the integrated circuit and should be connected to ground. In principle it could also be connected to +VS or –VS, but ground is preferable. The additional lead length and capacitance associated with sockets may cause problems in applications requiring the highest fidelity of high speed pulses. The circuit of Figure 5b overcomes the limitations of the previous circuit with DC loads. It allows nearly full output voltage swing up to its current limit of approximately 140mA. Both circuits require good high frequency capacitors (e.g., tantalum) to bypass the buffer’s power supply connections. Depending on the nature of the input source impedance, a series input resistor may be required for best stability. This behavior is influenced somewhat by the load impedance (including any reactive effects). A value of 50Ω to 200Ω is typical. This resistor should be located close to the OPA633’s input pin to avoid stray capacitance at the input which could reduce bandwidth (see Gain and Phase versus Frequency curve). CAPACITIVE LOADS The OPA633 is designed to safely drive capacitive loads up to 0.01µF. It must be understood, however, that rapidly changing voltages demand large output load currents: OVERLOAD CONDITIONS The input and output circuitry of the OPA633 are not protected from overload. When the input signal and load characteristics are within the devices’s capabilities, no protection circuitry is required. Exceeding device limits can result in permanent damage. ILOAD = CLOAD Thus, a signal slew rate of 1000V/µs and load capacitance of 0.01µF demands a load current of 10A. Clearly maximum slew rates cannot be combined with large capacitive loads. Load current should be kept less than 100mA continuous (200mA peak) by limiting the rate of change of the input signal or reducing the load capacitance. The OPA633’s small package and high output current capability can lead to overheating. The internal junction temperature should not be allowed to exceed 150°C. Although failure is unlikely to occur until junction temperature exceeds 200°C, reliability of the part will be degraded significantly at such high temperatures. Since significant heat transfer takes place through the package leads, wide printed circuit traces to all leads will improve heat sinking. Sockets reduce heat transfer significantly and are not recommended. USE INSIDE A FEEDBACK LOOP The OPA633 may be used inside the feedback path of an op amp such as the OPA602. Higher output current is achieved without degradation in accuracy. This approach may actually improve performance in precision applications by removing load-dependent dissipation from a precision op amp. All vestiges of load-dependent offset voltage and temperature drift can be eliminated with this technique. Since the buffer is placed within the feedback loop of the op amp, its DC errors will have a negligible effect on overall accuracy. Any DC errors contributed by the buffer are divided by the loop gain of the op amp. Junction temperature rise is proportional to internal power dissipation. This can be reduced by using the minimum supply voltage necessary to produce the required output voltage swing. For instance, 1V video signals can be easily handled with ±5V power supplies thus minimizing the internal power dissipation. The low phase shift of the OPA633 allows its use inside the feedback loop of a wide variety of op amps. To assure stability, the buffer must not add significant phase shift to the loop at the gain crossing frequency of the circuit—the frequency at which the open loop gain of the op amp is equal to the closed loop gain of the application. The OPA633 has a typical phase shift of less than 10° up to 70MHz, thus making it useful even with wideband op amps. Output overloads or short circuits can result in permanent damage by causing excessive output current. The 50Ω or 75Ω series output resistor used to match line impedance will, in most cases, provide adequate protection. When this resistor is not used, the device can be protected by limiting the power supply current. See “Protection Circuits.” Excessive input levels at high frequency can cause increased internal dissipation and permanent damage. See the safe ® OPA633 dV dt 6 +12V +15V C1 0.1µF R2 50Ω R1 180Ω VIN RG-58 OPA633 C4 0.1µF VIN Coaxial Cable R10 50Ω Pulse Generator 50Ω C1 0.1µF VOUT OPA633 R5 50Ω Termination C4 0.1µF R10 RL –15V –12V POSITIVE PULSE RESPONSE LARGE SIGNAL RESPONSE 10V STEP — RL = 1kΩ 100mV VIN 0 10V 50mV VIN VOUT 0 0 10V VOUT 0 NEGATIVE PULSE RESPONSE 10ns/div 10V STEP — RL = 100kΩ 0 VIN –100mV 10V 0 VIN VOUT 0 –50mV 10V VOUT 0 FIGURE 1. Coaxial Cable Driver Circuit. 10ns/div SMALL SIGNAL RESPONSE 0.5V STEP — RL = 1kΩ 0.5V VIN 0 0.5V VOUT 0 FIGURE 2. Dynamic Response Test Circuit. ® 7 OPA633 R9 10kΩ R9 1kΩ C5 500pF R4 1kΩ R8 150Ω OPA602 C5 50pF R8 150Ω OPA602 OPA633 OPA633 G = –10 FIGURE 3. Precision High Current Buffer. FIGURE 4. Buffered Inverting Amplifier. +VS 4.7Ω +VS (a) (b) 100Ω 1µF 1µF 2.7kΩ + Input OPA633 Tantalum + Output OPA633 Input 1µF + Tantalum Output 1µF + Tantalum Tantalum 100Ω –VS 4.7Ω –VS FIGURE 5. Output Protection Circuits. The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems. ® OPA633 8 IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Customers are responsible for their applications using TI components. In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof. Copyright 2000, Texas Instruments Incorporated