Resonant switched capacitor converter with high efficiency

advertisement

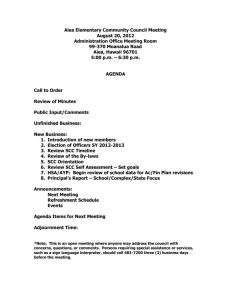

Aachen, Cemnny. 2w4 2004 35th Annual IEEE Power Electronics Specialists Conference Resonant Switched Capacitor Converter with High Efficiency Masahito Shoyama, Toshiyuki Naka, and Tamotsu Ninomiya Graduate School of Information Science and Electrical Engineering, Kyushu University, 6-10-1 Hakozaki, Higashi-ku, Fukuoka, 8 12-858 1 Japan. Email: shoyama@ees.kyushu-u.ac.jp Absfracf-ConventionaI switched capacitor converters have an inherent drawback that their efliciency is much decreased as the output current is increased. This inherent drawback is due to a periodical forced charging and discharging operation in the internal switched capacitors accompanied by a large capacitor current, so that their efliciency can not be increased by decreasing its internal resistance. As a result, conventional switched capacitor converters have been limited to be used with a very small output current. This paper presents some novel switched capacitor converter topologies that use a resonant operation instead ofthe forced charging and discharging operation. Their advantage over conventional switched capacitor converters is a high elliciency even in a high output current region. The operation analysis and steady-state characteristics are described in detail for a half buck type switched capacitor converter, and they are confirmed by experiments. (a) Conventional SCC. sz Sl v, 1. INTRODUCTION Switched capacitor converters (SCC's) have been used to realize small size and light weight DC-DC converters in many kinds of electronic devices. However, conventional switched capacitor converters have an inherent drawback that their efficiency is much decreased as the output current is increased. This inherent drawback is due to a periodical forced charging and discharging operation in the internal switched capacitors accompanied by a large capacitor current, so that their efficiency can not be increased by decreasing its internal resistance, e.g. conduction resistance of the switches. As a result, they are limited to be used with a very small output current. This paper presents some novel switched capacitor converter topologies that use a resonant operation instead of the forced charging and discharging operation. Their advantage over conventional switched capacitor converters is a high efficiency even in a high output current region. The operation analysis and steady-state characteristics are described in detail for a half buck type switched capacitor converter, and they are confirmed by experiments. For a double boost type and a voltage inverting type SCC's, circuit topologies, analytical and experimental results are briefly shown in the last part in this paper. 1I.CIRCUIT AND OPERATION ANALYSIS OF RESONANT SWITCHED CAPACITOR CONVERTER Figure 1 (a) shows a conventional circuit topology of a half 0-7803-8399-0/M/$20.00 02004 IEEE. (b) Resonant SCC with a resonant inductor Lr. Fig. I , Half buck type switched capacitor conveners (SCC's) f iCl Fig. 2. Comparison of waveforms ofthe capacitor current between conventional and resonant SCC's. buck type SCC, which is the first and main example to apply the idea of resonant SCC. In this figure, every time S, and Sz turns on alternately, a large pulse current flows through the capacitors C , and Cz by a forced charging and discharging operation as shown in Fig.2. This large pulse current brings 3780 2004 35rh A n n u l IEEE Power Elecrronics Specialists Conference about an inherent power loss at the internal resistance, e.g. conduction resistance of the switches. This power loss is inevitable and can not be decreased even when the internal resistance is reduced. This is because the pulse current is much increased in that case. Figure I (b), on the other hand, shows a novel circuit topology of a resonant SCC with a small resonant inductor Lr inserted to remove a large pulse current as shown in Fig. 2. CI operates as a resonant capacitor and Cz is an output capacitor assumed to be very large, namely C1<<C2. Two active switches SI and S2 are driven alternately with 50% duty ratio as shown in Fig. 3. Two diodes S, (0,)and S4 (D2) are switched synchronously to SI and S2, respectively. These diodes may be replaced by synchronous rectifiers of MOS-FET's in a low output voltage application. Figure 4 (a) is an equivalent circuit for State I where SI and , State I . Svdtc I 1 , State I . State I[ Fig. 3. Switching sequence for resonant SCC (Duly ratio = 50%) Aarhen. Germany. 2004 diode S, ( D l )is on. Here, rsl and rs3 denote the conduction resistance of SI and S, (Dl), respectively. Figure 4 (b) is an is on. equivalent circuit for State I1 where Szand diode S4(D2) Here, rS2 and rs4 denote the conduction resistance o f & and S4 (D2),respectively. Because ofthe small resonant inductor Lr, the charging and discharging current of C, becomes sinusoidal. So, a low power loss and a high efficiency are obtained when the internal resistance is reduced. Under the assumption Cl<<C2 for simplifying the analysis, the switching frequencyfs is set to meet the relation: 1 =2 z m ( 1 ) As long as this relation holds, SI and S2 are switched when the inductor current icl = 0. As examples of operation, Fig. 5 shows simulated key waveforms of vcl, V, and icl for the conventional SCC, and Fig. 6 shows them for the proposed resonant SCC with Lr. Operation conditions and circuit parameters are shown in Table 1. In the conventional SCC, a very large pulse current flows through C, due to the periodical forced charging and discharging. On the other hand, in the proposed resonant SCC, vcl and icl change sinusoidally. By analyzing the circuit operation in detail, the efficiency 7 and the output voltage V, are obtained for each SCC as shown in Table 2. For the conventional SCC, it is interesting to note that these expressions do not include any internal resistances. This means that the power loss is inevitable and can not be decreased even when the internal resistance is reduced. For the proposed resonant SCC, on the other hand, it is found that the power loss can be decreased when the internal resistance is reduced. Figure 7 (a) shows characteristics of the efficiency 7 as a hnction of the output current 1. taking the internal resistance r ( = rsI= rsz = rs3= r s 4 )as a parameter. It is apparent that the proposed resonant SCC with Lr maintains a high efficiency Table. I. Common operation conditions and Circuit parameters. LI i s used only for the resonant SCC. (Halfbuck type) (a) State I Table. 2. Analytical result of output volta~eand efficiency. (Half buck type) ~~ Conventional SCC Fig. 4. Equivalent circuits of resonant SCC with Lr (Half buck type) 3781 Resonant SCC - Anchen, Germany, 2004 2004 3Slh Annual IEEE Power Electronics Specialisls Conference 33 2 3.0 2.5 3.5 3.0 - 2.0 2.0 1.0 9 2 5 1.0 0.5 0.5 =3 1.5 8 2.5 1.5 0 0 1.0 0.5 0 1.5 2.0 0 0.5 Time (ps) Stste I Stntr 11 e E 2.0 1.5 1 2.0 1.5 - 10 5 1.5 2.0 I5 - 1.0 Time (ps) I .o - 5 0.5 go o U -0.5 U -5 -1.0 -10 -15 -1.5 ' 0 .2.0 I 1.0 0.5 1.5 2.0 ' o 1 1 0.5 1.0 Time (ps) Time (ps) Fig. 6. Simulated key waveforms for Resonant SCC. Conditions: I, = IA, I ( SI = I S > = IS, = r~ ) = SOmQ. (Half buck type) Fig. 5. Simulated key waveforms for conventional SCC. Conditions: I, = IA I ( = ,SI = I S > = I S , = i s 4 ) = SOrnQ. (Halfbuck type) even when lo increases, while the efficiency of the conventional SCC without Lr is much decreased. Figure 7 (b) shows characteristics of the output voltage V. as a function of the output current L. It is noticed that the trend is very similar F k . 7 (a), and the output voltage vo is not much reduced even when loincreases in the resonant SCC with Lr. 111. EXPERIMENTAL VERIFICATION In order to verify the validity of the analysis, we made experimental SCC circuits as shown in Fig. 8 (a), (b). For each SCC, two MOS-FET's are used for S, and Sa as 2.5 -x --> 2 95 9 0 y 1 a 80 -g- g 75 6 .- 2.3 2.2 B Conventional SCC- 5 2.4 2.1 2.0 1.9 * a 70 65 1.8 1.7 "" 1.5 60 0 0.5 I.o I 5 20 U 0 Output Current I, (A) 0.5 1.o 1.5 Output Current I, (A) 2.0 (b) Output current characteristicsof output voltage (a) Output current characteristicsof efficiency Fig. 7. Simulated characteristicsof q and V,. (Half buck type) 3782 2004 35rh Annual IEEE Power Electronics Specialisrs Conference Aachen, Germany, 2004 indeed. F i g y e I 1 (a) shows experimental results ofthe efticiency '1 and Fig. 1 I(b) shows the output voltage V. as a function ofthe output current I,. These experimental results agree well with the simulation results shown in Fig. 7. According to the experimental results the equivalent internal resistance r is estimated to be about Soma. It is well confirmed by this figure that the proposed resonant SCC with Lr maintains a high efficiency even in a high output current region. 9 "T (a) Conventional SCC Iv. APPLICATION TO OTHER TYPES OF SCC The concept of resonant SCC can be applied to other types of SCC's. As typical examples, for a double boost type and a voltage inverting type SCC's, circuit topologies, analytical and experimental results are briefly shown in Fig's. 12-17 and Tables 3-6 in the following pages. V.CONCLUSION Some novel switched capacitor converter topologies that use a resonant operation have been presented. Their advantage over conventional switched capacitor converters is a high efficiency even in a high output current region. The operation analysis and steady-state characteristics have been described and confirmed by experiments. (b) Resonant SCC with a resonant inductor Lr. Fig. 8. Experimental circuits ofthe half buck type SCC's. synchronous rectifiers to reduce the internal resistance of the switches. Figure 9 shows experimental waveforms for the conventional SCC, and Fig. IO shows for the resonant S C C . In the conventional SCC, a small parasitic inductance is inserted in series with C,. In the resonant SCC, on the other hand, a predicted sinusoidal waveform of Y., is observed ACKNOWLEDGMENT This research was supported partly by the 21st Century COE Program "Reconstruction of Social Infrastructure Related to Information Science and Electrical Engineering." t f ,.J ..........., .... <;NI, (a) Capacitor voltage vel .:. .&... ..... :.. 2 . . . . . . . . ',",d,".j . .I ..... ........................ Ti."= 50" nl, 4." LIdl__. (a) Capacitor voltage v , ~ .... ... .... d. ON" (b) Output voltage V, (b) Output voltage V, Fig. 9. Experimental waveforms for conventional SCC. Conditions: I, = IA, I = 50mn (estimated). Fig. IO. Experimental waveforms fw Resonant SCC Conditions: I,,= IA, r = 50mn (estimated). 3783 Aachen, Germany, 2004 2004 35th Annual IEEE Power Electronics Specialisrs Conference . ., . 95 ' "i 65 Calculation 1.6 (I= 5(1mQ) I Calculation (r = 50 Inn) Y" 0 0.5 1.0 1.5 2.0 Output Current I, (A) (a) Output current characteristics o f efficiency (b) Output current characteristics o f output voltage Fig. 11. Experimental characteristics of 7 and V,. (Half buck type) v,. Fig. 12. Double b w s t type resonant SCC derived from conventional SCC by insening Lr in senes with C,. Switching sequence is the same as shown in Fig. 2,. Fig I3 Voltage invcningt)pc rcwnanl 5CC dsriscd from i ~ n v c n t i . m I SCC b) inrcrling 1.1 in scrics u i t h C , S ~ i r c h i n gsequence IS the iamc as shoun in Ctg 3 Table. 3. Analytical result ofoutput voltage and efficiency (Double b w s t type) I\I Conventional SCC I Table. 4. Analylical result ofoutput voltage and efficienc). (Voltage invening type) Resonant SCC Conventional SCC 3784 Resonant SCC 2004 35th Annual IEEE Power Electronics Specialists Conference V, ~r C, C, 2 . W IpF IOOpF lWnH fs '3, =rsi =rs, = rr4= r 2OmR 50mn Aachen, Germany, 2004 C, C, 5WWz 5V L fs rs, = r s 2 =rs, =rs4 = r IpF IOOpF IOOnH 20mR 5ookHz 50mR IO0 95 90 5 85 h aJ 400 2 75 ->" 2 70 U 5 350 E w 2 P 80 n 65 60 "entlonal SCC 375 ;;; 2 75 _I" 0 0.5 I.o 0.5 0 I.5 (a) Output current characteristics of efticiency (b) Output current characteristics of output voltage Fig. 14. Simulated characteristics of 0.5 I.o Output Current I<, (A) I.5 Output Current I,, (A) Output Current I, (A) 0 I.o and V. (Double boost type) 0 I.5 0.5 I .o 1.5 Output Current I, (A) (a) Output current characteristics of efficiency (b) Output current characteristics ofoutput voltage Fig. I 5. Experimental characteristics of q and V,. (Double boost type) 3785 Aachen, Germany, 2004 2004 35th Annual IEEE Power Elecrronics Specialisrs Conference 100 5.00 -' 4.75 95 90 4.50 6 $, 85 4.25 c 80 75 3 4.00 &. .g 70 5 3.50 $ 3.75 ;:;; a d 65 60 85 2.15 50 2.50 0 I .5 1.0 0.5 0.5 I .o Output Current I, (A) 0 Output Current fo (A) I .5 (b) Output current characteristics ofoutput voltage (a) Output current characteristics ofefficiency Fig. 16. Simulated characteristics of rj and V.. (Voltage invertingtype) 5.00 IO0 9s 4.75 p 90 4.50 h 7, 85 e f. 80 / ' Calculation ( r = 50mn)-" 55 50 0 0.8 .* 1.O Output Current I.5 0 1 (A) 0.5 I.o Output Current (a) Output current characteristicsof efficienq I I .5 (A) (b) Output current characteristics of output voltage Fig. 17. Experimentill characteristics of q and V,. (Voltage invertingtype) 3786