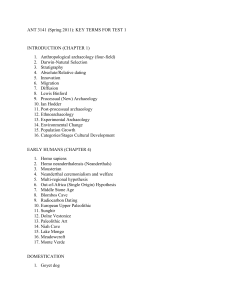

VLSI Design 綜科館 104 研討室 Please noted

advertisement

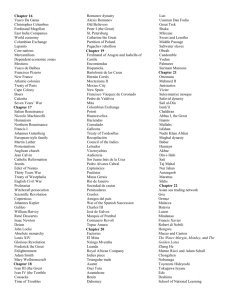

VLSI Design 綜科館 104 Please noted VLSI Design : Chapter 5-1 1 VLSI Design D i Textbook: Modern VLSI Design System-on-Chip System on Chip Design, Third edition, Prentice Hall, b W by: Wayne Wolf W lf 中文版 近代VLSI設計 System-on-Chip 設計 VLSI Design : Chapter 5-1 2 R f References Embedded Systems Design: A Unified Hardware / Software Introduction, g Vahid / Givargis Rabaey s Digital Rabaey’s Di it l Integrated I t t d Circuits, Ci it J. J Rabaey et al.] VLSI Design : Chapter 5-1 3 Instructor 高得畬 Kao, De-Yu E-mail: kao_deyu@yahoo.com Class Notes: http://www.cc.ntut.edu.tw/~dkao/ http://www cc ntut edu tw/~dkao/ Please download all class notes, sample examinations homework, examinations, homework and scores from above URL VLSI Design : Chapter 5-1 4 G di Policy Grading P li Two quizzes 30% (15% for each) Midterm 35% Final 35% VLSI Design : Chapter 5-1 5 Q i k Review Quick R i Introduction of the VLSI Design Chapter 1 VLSI Introduction Moore’s Law, Cost Chapter 2 Transistors and Layout Mask Processing Cross-section RC extraction Design Rules Package g Chapter 3 Logic Gates Noise Margin, Timing Chapter 4 Combination Logic Networks Timing Cross talk Testing VLSI Design : Chapter 5-1 6 S h d l (1) Schedule 01. 09/15/16 中秋節 02. 09/22/16 Chapter 5 (Memory types, Set-up & hold time) 03. 09/29/16 Chapter 5 (Memory devices: Latch, FF, & ROM) 04. 10/06/16 Chapter 5 (Memory devices: RAM , Clock skew) 05 10/13/16 Chapter 05. Ch t 5 (Memory timing and clock, Testing) 06. 10/20/16 (QZ1) Chapter 5 (Sequential machine, State graph) VLSI Design : Chapter 5-1 7 S h d l (2) Schedule 07. 10/27/16 Packaging 08. 11/03/16 Midterm Examination 09 11/10/16 Exam review , Chapter 6 (Adder) 09. (Add ) 10. 11/17/16 Chapter 6 (Multiplier) 11. 11/24/16 Chapter 7 (Placement) 12 12/01/16 Chapter 12. Ch t 7 (Routing, (R i Special S i l nets)) VLSI Design : Chapter 5-1 8 S h d l (3) Schedule 13. 12/08/16 Chapter 7 (Misc before TO) 14. 12/15/16 Chapter 8 (Architecture) 15 12/22/16 (QZ2) Chapter 8 (Architecture) 15. (A hit t ) 16. 12/29/16 Chapter 9 (Example) 17. 01/05/17 Final Examination 18 01/12/17 Exam 18. E review, i Wh t’ Next? What’s N t? VLSI Design : Chapter 5-1 9 Flow Fl Marketing survey Specification Design: Architecture, Logic, Circuit Backend, …. Manufacture: Masks, Die, Packaging Testing g VLSI Design : Chapter 5-1 Market 10 A Si Simplified lifi d Design D i Flow Fl C,mathlab,orjustwords RTL System Design RTL Design Synthesis Netlist Verify and Debug Gate Level Virtual Prototype yp Place and Route Timing SPICE Physical VLSI Design : Chapter 5-1 RC Extraction Transistor CKT GDSII 11 Ch Chapter 55: Sequential S i l Machines M hi Memories Introduction Memories Latch Flipp Flopp Shift Register ROM RAM, …… Clock and Timing Memory Test (BIST) Application Example State Assignment VLSI Design : Chapter 5-1 12 M Memory T Types Read-Write Memory Random Access SRAM DRAM Flip Flop Latch VLSI Design : Chapter 5-1 Non Random Non-Random Access FIFO Shift Register Non-Volatile Read-Write Read Write Memory Read-Only Memory EPROM Mask-Programmed E2PROM Programmable (PROM) FLASH LIFO SIPO PISO 13 Memory y Types yp Memory Volatile Memory DRAM SRAM VLSI Design : Chapter 5-1 Non-volatile Memory Mask ROM EPROM EEPROM Flash MTP ROM OTP NVRAM ROM 14 Memory Memory’s output is related to the previous state and the inputs S Stores a value l bby controlled ll d (clock) ( l k) signal. i l In CMOS, memory is created by: hardwire circuit capacitance (dynamic); feedback (static). VLSI Design : Chapter 5-1 15 M Memories i T Terms Clock, Data, Address Clock: edge, skew, duty cycle, phase, nonoverlapped Data: Single port, 2-port, dual-port Timing: Setup & Hold time Enables: R/W enable enable, chip enable VLSI Design : Chapter 5-1 16 M Memories i Dynamic: Need refresh, Static: Feedback loop Latch: Level trigger, transparent, race through Flip Flop: Edge trigger, Flip-Flop: trigger non-transparent non transparent (Used more often) Volatile; Non-volatile VLSI Design : Chapter 5-1 17 V l il Non-volatile Volatile; N l il Memories M i Volatile memory: data will lose after power off – SRAM (static random access memory): – – – – Low Power (or Low Voltage) SRAM / High Speed SRAM DRAM (dynamic RAM, RAM need refresh): Synchronous DRAM / Double Data Rate (DDR) SDRAM FCRAM (FJ, Fast Cycle RAM): DRAM cell with SRAM peripheral Non volatile memory: data still keep after power off – ROM (read only memory) / PROM (programmable ROM) – – EPROM (Erasable PROM) / EEPROM (Electrical EPROM) Flash VLSI Design : Chapter 5-1 18 B i Concepts Basic C m × n memory Stores large number of bits … » 32,768 bits » 12 address input signals » 8 input/output data signals Memory access r/w: selects read or write enable: bl readd or write it only l when h asserted t d multi-port: multiple accesses to different locations simultaneously m worrds m x n: m words of n bits each k = Log2(m) address input signals or m = 2^k words e g 4,096 e.g., 4 096 x 8 memory: … n bits per word memory external view r/w 2k × n read and write memory enable A0 … Ak-1 … Qn-1 VLSI Design : Chapter 5-1 Q0 19 M Memory Hi Hierarchy h On-Chip Components Control eDRAM D Instr Data ache Cache Ca C .1 1’s s 1’s 1 s 10 10’s s 100 100’s s Size (bytes): 100’s K’s 10K’s M’s F FF, L Latch Cost: VLSI Design : Chapter 5-1 ITLB DTLB Speed (ns): Datapath Reg gFile Second Level Cache (SRAM) g highest Main Memory (DRAM) Secondary Memory (Disk) 1 1,000 000’s s T’s lowest 20 Traditional ROM/RAM distinctions ROM » read only only, bits stored without power » read and write, lose stored bits without power RAM Traditional distinctions blurred Advanced ROMs can be written to » e.g., EEPROM Storage permanence M Memories i Life of product Tens of years Battery life (10 years) Advanced RAMs can hold bits without power » e.g., NVRAM Write ability Manner and speed a memory can be written Storage permanence ability of memory to hold stored bits after they are written Mask-programmed ROM Ideal memory OTP ROM Life time EPROM EEPROM FLASH NVRAM Nonvolatile Speed p In-system pprogrammable og ammable SRAM/DRAM Near zero Write ability During External fabrication programmer, only one time only External External External programmer, programmer programmer 1,000s OR in-system, OR in-system, 1,000s block-oriented of cycles writes, 1,000s of cycles of cycles In-system, fast i writes, unlimited cycles Write ability and storage permanence of memories, showing relative degrees along each axis (not to scale). VLSI Design : Chapter 5-1 21 V i i Variations in i memory elements l Form of required control (clock) signal. How behavior of data input around clock (control) affects the stored value. value When the stored value is presented to the output. Whether there is ever a combinational path from input to output. (Race) VLSI Design : Chapter 5-1 22 M Memory A Application li i LP-SRAM: mobile phone HS-SRAM: cache memory DRAM: will be phase out SDRAM / DDR: mother board / graphic card ROM / PROM / EPROM: game machine / BIOS EEPROM / Fl Flash: h smartt card d / voice i recorder d VLSI Design : Chapter 5-1 23 Shi i Peaks Shipping P k VLSI Design : Chapter 5-1 24 D Demands d are not stable bl VLSI Design : Chapter 5-1 25 DRAM Chip Chi C Capacity i VLSI Design : Chapter 5-1 26 R d i suppliers Reducing li VLSI Design : Chapter 5-1 27 VLSI Design : Chapter 5-1 28 Ri k Market Risky M k VLSI Design : Chapter 5-1 29 數據公佈時間 (一) 國際DRAM/NAND Flash現貨價格(Spot price): (一). 每日公佈三次現貨價格: AM11:00 PM 02:30 PM 06:00 (二). 國際DRAM/NAND Flash合約價格(Contract price): price) DRAM:一個月更新兩次,一般來說是在每月的6號及20號。 NAND Flash:一個月更新兩次,目前是擇期公佈並無明確時間 VLSI Design : Chapter 5-1 30 Different Memories and Circuits VLSI Design : Chapter 5-1 31 Cl k terminology Clock i l Clock edge: rising or falling transition. Duty cycle: fraction of clock period for which clock is active (e (e.g., g for active-low active low clock, clock fraction of time clock is 0). Clock Data Positive edge clock VLSI Design : Chapter 5-1 32 T Sequential Two S i l Logics L i Latch: transparent when internal memory is being set from input. (level) Flip-flop: not transparent—reading input and changing h i output are separate events. (edge) ( d ) VLSI Design : Chapter 5-1 33 S i / Dynamic Static D i Memories M i Static – SRAM data is stored as long as power is applied large cells (6 fets/cells) – so fewer bits/chip fast – so used where speed is important (e.g., caches) differential outputs (output BL and !BL) use sense amps for f performance f compatible with CMOS technology Dynamic – DRAM periodic i di refresh f h required i d small cells (1 to 3 fets/cells) – so more bits/chip slower – so used for main memories single i l ended d d output t t (output ( t t BL only) l ) need sense amps for correct operation not typically compatible with CMOS technology VLSI Design : Chapter 5-1 34 D Dynamic i llatchh Stores charge on inverter gate capacitance: VLSI Design : Chapter 5-1 35 L h characteristics Latch h i i Uses complementary transmission gate to ensure that storage node is always strongly driven. Latch is transparent when transmission gate is on. on Storage capacitance comes primarily from inverter gate capacitance. VLSI Design : Chapter 5-1 36 L h operation Latch i = 0: transmission gate is off, inverter output is determined by storage node. = 1: transmission gate is on, on inverter output follows D input. Setup and d hold h ld times i determined d i d by b transmission gate—must ensure that value stored on transmission gate is solid. VLSI Design : Chapter 5-1 37 S Stored d charge h lleakage k Most of the stored charge leaks due to reverse-bias leakage current. Stored value is good for about 1 ms. ms Value must be rewritten to be valid. If not loaded every cycle, must ensure that latch is loaded often enough to keep data valid. VLSI Design : Chapter 5-1 38 S i k diagram Stick di VDD D VSS Q’ ’ VLSI Design : Chapter 5-1 39 Layout VDD D Q’ VSS VLSI Design : Chapter 5-1 ’ 40 R i l i latch Re-circulating l h Static on one phase: VLSI Design : Chapter 5-1 41 N d Non-dynamic i latches l h Must use feedback to restore value. Some latches are static on one phase (pseudostatic)—load static) load on one phase phase, activate feedback on other phase. VLSI Design : Chapter 5-1 42 From now on, we will have our lecture in 綜科館 104 研討室 @ 18:40 Please noted VLSI Design : Chapter 5-1 43 S h d l (1) Schedule 01. 09/15/16 中秋節 02. 09/22/16 Chapter 5 (Memory types, Set-up & hold time) 03. 09/29/16 Chapter 5 (Memory devices: Latch, FF, & ROM) 04. 10/06/16 Chapter 5 (Memory devices: RAM , Clock skew) 05 10/13/16 Chapter 05. Ch t 5 (Memory timing and clock, Testing) 06. 10/20/16 (QZ1) Chapter 5 (Sequential machine, State graph) VLSI Design : Chapter 5-1 44 M Memories i Dynamic: Need refresh, Static: Feedback loop Latch: Level trigger, transparent, race through Flip Flop: Edge trigger, Flip-Flop: trigger non-transparent non transparent (Used more often) Volatile; Non-volatile VLSI Design : Chapter 5-1 45 D Dynamic i llatchh Stores charge on inverter gate capacitance: VLSI Design : Chapter 5-1 46 R i l i latch Re-circulating l h q1 s 1 s 2 s 2 2 VLSI Design : Chapter 5-1 47 SR L Latchh VLSI Design : Chapter 5-1 48 Cl k d SR Latch Clocked L h VLSI Design : Chapter 5-1 49 DL D-Latach h VLSI Design : Chapter 5-1 50 Ti Tri-states i inverter circuit symbol y VLSI Design : Chapter 5-1 51 Ti Tri-states i inverter operation i = 0: both clocked transistors are off, output is floating. = 1: both clocked inverters are on, on acts as an inverter to drive output. VLSI Design : Chapter 5-1 52 Ti Tri-states i inverter latch l h = 0: i1 is off, i2-i3 form feedback circuit. = 1: i2 is off, breaking feedback; i1 is on, driving i3 and output. output Latch is transparent when = 1. VLSI Design : Chapter 5-1 53 Fli fl Flip-flops Not transparent—use multiple storage elements to isolate output from input. Major varieties: master-slave; edge-triggered. d i d master D slave Q VLSI Design : Chapter 5-1 54 Si l in Signals i flip-flop fli fl system positive clock edge Setup VLSI Design : Chapter 5-1 Hold 55 M Memory element l parameters Setup time: time before clock during which data input must be stable. Hold time: time after clock event for which data input must remain stable. clock data setup t hold VLSI Design : Chapter 5-1 56 M Master-slave l operation i = 0: master latch is disabled; slave latch is enabled, but master latch output is stable, so p does not change. g output = 1: master latch is enabled, loading value from input; slave latch is disabled, disabled maintaining old output value. VLSI Design : Chapter 5-1 57 D Fli Flip-Flops Fl (1) Tx1 D CLK A B Tx3 Tx2 CLK C Q Tx4 Qn Master D CLK VLSI Design : Chapter 5-1 Slave Q Qn 58 Tx1 B A D CLK Tx2 C Q CLK Tx3 D Fli Flip-Flops Fl (2) Tx4 Qn TX1 TX2 TX3 TX4 CLK D A B C Q Qn Q on off on off ff on 1 VLSI Design : Chapter 5-1 101 1 0 0 off 0 1 0 0 0 off 1 0 1 1 0 0 0 1 on off on 1 0 off on off ff on off on ooff on off on 1 1 0 0 59 Tx1 B A D CLK Tx2 C Q CLK T 3 Tx3 D Fli Flip-Flops Fl (3) Tx4 Qn TX1 TX2 TX3 TX4 CLK D A B C Q Qn Q on off on off ff on 1 VLSI Design : Chapter 5-1 0 101 1 0 0 1 0 1 0 1 0 0 0 0 1 0 off 0 1 1 0 1 1 0 0 1 1 on off on off 1 off on off ff on off on ooff on off on 0 1 0 1 60 A D B C Q CLK CLK D Fli Flip-Flops Fl Neg(4) N (4) Qn Tx1 D A CLK B Tx3 Tx2 CLK C Q Tx4 Qn D CLK VLSI Design : Chapter 5-1 Q Qn 61 B A D C Q CLK CLK D Fli Flip-Flops Fl Neg N (5) Qn TX1 TX2 TX3 TX4 CLK D A B C Q Qn Q off on on on off ff off off on on on off ff off off on on off on off on off 1 0 1 VLSI Design : Chapter 5-1 0 1 1 0 0 1 1 1 0 0 1 0 1 0 1 0 0 0 1 0 1 62 Si l in Signals i flip-flop fli fl system positive clock edge Meta-stability Setup VLSI Design : Chapter 5-1 Hold 63 M Meta-stability bili When sampling a changing data signal with a clock… the order of the events determines y the outcome… when two events occur very close together, the decision process can take longer than the time allocated, allocated and a synchronization failure occurs. --- Dally and Poulton’s book VLSI Design : Chapter 5-1 64 S Some O Other h D Designs i VLSI Design : Chapter 5-1 65 Fli fl rules Flip-flop l Primary inputs change after clock () edge. Primary inputs must stabilize before next clock edge. edge Rules allow changes to propagate through combinational bi i l logic l i for f next cycle. l Flip-flop Flip flop outputs hold current current-state state values for next-state computation. VLSI Design : Chapter 5-1 66 Fli Fl Flip-Flops VLSI Design : Chapter 5-1 67 L h b d machines Latch-based hi Latches do not cut combinational logic when clock is active. Latch-based Latch based machines must use multiple ranks of latches. Multiple l i l ranks k require i multiple l i l phases h off clock. VLSI Design : Chapter 5-1 68 E Example: l shift hif register i Want to displace bit by n registers in n cycles. Each register requires two phases: VLSI Design : Chapter 5-1 69 Shif register Shift i layout l Forms a linear array: in out VSS c1(latch) 1 1’ VLSI Design : Chapter 5-1 c2(latch) 2 2’ c3(latch) 1 1’ c4(latch) 2 2’ 70 Shif register Shift i operation i 0 0 1 1 1 0 1 = 1, 2 = 0 0 VLSI Design : Chapter 5-1 1 1 = 0, 2 = 1 71 N Non-strict i disciplines di i li Some relaxation of the rules can be useful: reduce area; increase performance. Rules must be relaxed in a way that ensures th machine the hi will ill still till work. k VLSI Design : Chapter 5-1 72 High-density memory architecture hi Address is divided into row, column. l Row may contain full word or more than one word word. Selected row drives/senses bit lines in columns. A lifi /d i Amplifiers/drivers read/write bit lines. VLSI Design : Chapter 5-1 73 R d l memory (ROM) Read-only ROM core is organized as NOR gates— pulldown lld transistors t i t off NOR determine d t i programming. Erasable ROMs require special processing yp y available. that is not typically ROMs on digital ICs are generally maskprogrammed—placement programmed placement of pull pull-downs downs determine ROM contents. VLSI Design : Chapter 5-1 74 Terms Via ROM Diffusion ROM VLSI Design : Chapter 5-1 75 ROM core circuit i i row0 = 1 row1 = 1 VLSI Design : Chapter 5-1 bit’[1:0] 0 1 1 0 76 ROM core circuit i i row0 = 1 row1 = 1 VLSI Design : Chapter 5-1 bit’[1:0] 00 10 77 ROM core circuit i i row0 = 1 row1 = 1 VLSI Design : Chapter 5-1 bit’[1:0] 00 10 78 PROM ++ VLSI Design : Chapter 5-1 ++ + 79 eFuse Ca Silicided Polysilicon Vdd Cathode Anode electromigrate silicide towards anode VLSI Design : Chapter 5-1 80 A iF Anti-Fuse VLSI Design : Chapter 5-1 81 S i RAM (SRAM) Static Core cells use six-transistors circuit to store value. Value is stored symmetrically — complements are stored on cross-coupled transistors. transistors SRAM retains value as long as power is applied. VLSI Design : Chapter 5-1 82 Terms Single port RAM 2 port RAM 2-port Dual-port RAM VLSI Design : Chapter 5-1 83 SRAM core cell ll Q VLSI Design : Chapter 5-1 84 Layout select se ect VLSI Design : Chapter 5-1 select se ect 85 Layout VLSI Design : Chapter 5-1 86 M Memory C Core VLSI Design : Chapter 5-1 87 M Memory C Core VLSI Design : Chapter 5-1 88 S Sense AMP and dC Cells ll VLSI Design : Chapter 5-1 89 A hi Architecture VLSI Design : Chapter 5-1 90 H Home works k 1. 5-4 : Draw a circuit (in MOS level) for Dflip-flop VLSI Design : Chapter 5-1 91