Zero-Voltage-Switching PWM Full-Bridge Converter Employing

advertisement

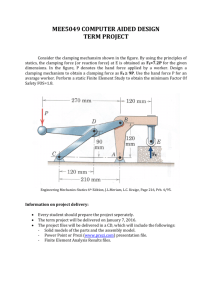

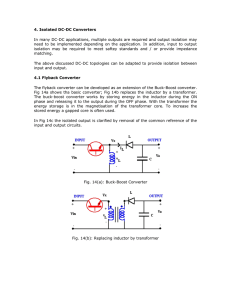

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 1149 Zero-Voltage-Switching PWM Full-Bridge Converter Employing Auxiliary Transformer to Reset the Clamping Diode Current Wu Chen, Student Member, IEEE, Xinbo Ruan, Senior Member, IEEE, Qianghong Chen, Member, IEEE, and Junji Ge Abstract—Introducing clamping diodes into the zero-voltageswitching (ZVS) pulsewidth-modulation (PWM) full-bridge (FB) converters can eliminate the voltage oscillation across the output rectifier diodes; however, the clamping diodes result in increase in conduction loss and suffer from serious reverse recovery at light load. In order to solve these problems, the clamping diode current should be reset rapidly. This paper proposes a scheme of resetting the clamping diode current over the full-load range by introducing an auxiliary transformer into the ZVS PWM FB converter. The operation principles of the proposed scheme under heavy-load and light-load conditions are analyzed in details. The design considerations of the introduced auxiliary transformer are also given. A performance comparison among the proposed scheme of resetting the clamping diode current and other ones are addressed. Experimental results verify the effectiveness of the analysis and prove that the proposed converter has improved reliability and reduced conduction loss compared with the classical one. Index Terms—Auxiliary transformer, clamping diodes, fullbridge (FB) converter, light load, zero-voltage-switching. I. INTRODUCTION ERO-voltage-switching (ZVS) pulsewidth modulation (PWM) full-bridge (FB) converters have been widely used in medium-to-high power applications because they feature the constant frequency operation and easy achievement of ZVS for power switches with the use of the leakage inductor of the transformer and the intrinsic capacitors of the power switches [1]–[11]. The major limitation of the ZVS PWM FB converters is that the lagging switches will lose ZVS under lightload condition, since the energy stored in the leakage inductor is insufficient to charge and discharge the switch intrinsic capacitors. An external resonant inductor is always added to be in series with the primary side of the transformer to extend the ZVS load range; however, the resonant inductor results in high voltage ringing across the output rectifier diodes. In or- Z Manuscript received August 6, 2009; revised October 26, 2009. Current version published May 7, 2010. This work was supported by the National Natural Science Foundation of China under Award 50837003. Recommended for publication by Associate Editor M. Alonso. W. Chen is with the Aero-Power Sci-Tech Center, College of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing, China (e-mail: chenwu@nuaa.edu.cn). X. Ruan is with the College of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan 430074, China (e-mail: ruanxb@mail.hust.edu.cn). Q. Chen and J. Ge are with the Aero-Power Sci-Tech Center, College of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China (e-mail: chenqh@nuaa.edu.cn; gejunji@nuaa.edu.cn). Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/TPEL.2009.2038698 der to overcome this problem, Redl et al. [8]–[10] introduced two clamping diodes into the primary side, clamping the voltage of the output rectifier diodes at the reflected input voltage and the voltage ringing is eliminated, thus the output rectifier diodes with lower voltage rating can be used, thus leading to a potentially higher efficiency. In [10], the difference between the two locations of the resonant inductor and the transformer was analyzed and an optimal scheme, in which the transformer is connected with the lagging leg, was first presented. Ruan and Liu [11] also analyzed this issue in details and discussed the effects of the blocking capacitor in different positions and pointed out that the blocking capacitor should be in series with the transformer, which is connected with the lagging leg. When the FB converter transits from zero state (vA B = 0) to active state (vA B = +Vin or − Vin ), the clamping diode conducts, and its initial current equals to the peak resonant current that results by the resonance of the resonant inductor and the parasitic capacitor of the output rectifier diode. The clamping diode current decays with the increase of the output filter inductor current. The output filter inductor is always designed to be very large to obtain a lower current ripple; therefore, the rise rate of its current is very small, leading to a longer conduction time of the clamping diodes, and thus relatively larger conduction loss occurs in the clamping diodes, resonant inductor, and leading switches. In order to accelerate the decline rate of the clamping diode current, a resistor or two back-to-back Zener diodes can be added in series with the clamping diodes [10], but there exists considerable loss in the resistor or Zener diodes. An auxiliary winding of the main transformer was added in series with the resonant inductor and it is lossless [12]. However, the duty cycle is very small at light load, thus leading to an insufficient time for the auxiliary winding voltage to fully reset the clamping diode current. The analyses about the operation of the clamping diodes in [8]–[12] are all under heavy-load condition. At light load, especially at no load, the operation of the two clamping diodes is very different from that under heavy-load condition; the two clamping diodes keep conducting alternately for almost half of the switching period, resulting in considerable conduction loss; in the meanwhile, the clamping diodes may be hard to be turned off with serious reverse recovery. Therefore, the clamping diodes are easily damaged under light-load condition, especially in high input voltage application [13]. In [14], a current transformer is introduced to be in series with the clamping diodes, thus making the clamping diode current to decay rapidly over the full-load range. 0885-8993/$26.00 © 2010 IEEE 1150 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 Fig. 1. Classical ZVS PWM FB converter with clamping diodes. Based on [14], this paper proposes an improved scheme of resetting the clamping diode current rapidly for the ZVS PWM FB converter by introducing an auxiliary transformer. The proposed scheme can shorten the clamping-diode conduction time and fully reset the clamping diode current over the full-load range, leading to reduced conduction loss, and the clamping diodes turn-OFF naturally. This paper is organized as follows. In Section II, the insight into the operation of the clamping diodes in ZVS PWM FB converter under light-load condition is presented. In Section III, the principle of resetting the clamping diode current is analyzed and several current resetting schemes are discussed and compared. In Section IV, an improved current resetting scheme is proposed by introducing an auxiliary transformer, which can reset the clamping diode current effectively over full-load range, and moreover, the excessive energy stored in the resonant inductor is also regenerated to the input voltage source. The operation principle of the ZVS PWM FB converter with the improved current resetting scheme is presented. The design considerations of the improved current resetting scheme are discussed in Section V. The experimental results are presented in Section VI to verify the validity of the improved current resetting scheme. Finally, Section VII concludes the paper. II. INSIGHT INTO THE OPERATION OF THE CLAMPING DIODES IN ZVS PWM FB CONVERTER UNDER LIGHT-LOAD CONDITION Fig. 1 shows the classical ZVS PWM FB converter with clamping diodes, and the popular phase-shifted control is adopted. Q1 and Q3 form the leading leg and Q2 and Q4 form the lagging leg. Lr is the additional resonant inductor, D5 and D6 are the clamping diodes, and DR 1 and DR 2 are the output rectifier diodes. Lf is the output filter inductor, Cf is the output filter capacitor, and RL d is the load. The concrete operation principle of the converter depends on the load condition. As stated earlier, under heavy-load condition, the decline rate of the clamping diode current is small due to the relative large output filter inductor; therefore, the clamping diodes conduct for a long time, thus leading to conduction loss in the clamping diodes, resonant inductor, and the leading switches. The operation principle of the converter under heavy load has been intensively discussed in [8]–[12]; therefore, we will here emphasize on the operation principle of the converter under light load. To simplify the analysis, the following assumptions are made, which are as follows: 1) all the switches and diodes are ideal, except for the output rectifier diode, which is equivalent to an ideal diode and a paralleled capacitor to simulate the reverse recovery, and CD R 1 = CD R 2 = CD R ; 2) all the capacitors, inductors, and transformer are ideal; 3) Lf Lr /K 2 , where K is the turns ratio of the primary and secondary windings of the main transformer. The key waveforms of the FB converter with clamping diodes under light-load condition are shown in Fig. 2 (there are two cases depending on the load), where the details of switching transitions are not shown explicitly because the intension is to describe the operation principle of the resonant inductor and the clamping diodes. From Fig. 2, it can be seen that except for the operation during [t1 , t3 ], the two cases almost have the same key waveforms. Referring to Fig. 2, prior to t0 , Q1 , Q4 , and D5 conduct (the reason why D5 conducts will be explained later), as shown in Fig. 3(a), and the primary winding voltage of the transformer vC B equals to Vin . DR 1 conducts and DR 2 is reversely biased, and vrect equals to Vin /K, and the output filter inductor current iL f and ip increase linearly. Lr is shorted by Q1 and D5 , and its current iL r remains almost unchanged. The difference of iL r and ip flows through D5 . At t0 , Q1 is turned off, and Q3 is turned on with hard switching due to light load. As D5 and Q4 still conduct, iL f and ip continue to increase linearly. vin is negatively applied on Lr , as shown in Fig. 3(b), forcing iL r to decline linearly. At t1 , iL r reduces to ip and D5 turns off. After t1 , Lr resonates with CD R 2 and iL r decreases. The equivalent circuit of this mode is shown in Fig. 3(c), and it and iL f are the is further simplified as Fig. 4(a), where CD R reflected CD R 2 and iL f to the primary side, respectively. According to Fig. 3(c), we have iD R 1 (t) + iC D R 2 (t) = iL f (t) (1) iD R 1 (t) − iC D R 2 (t) = Kip (t). (2) From (1) and (2), iD R 1 and iC D R 2 can be derived as 1 iL f (t) + Kip (t) 2 1 iL f (t) − Kip (t) . iC D R 2 (t) = 2 iD R 1 (t) = (3) (4) According to Fig. 4(a), ignoring the slight change of iL f , the primary current and the voltage across CD R 2 can be expressed as ip (t) = iL r (t) = 2Vin cos ω1 (t − t1 ) (6) K , and Z = 4CD R K 2 , ω1 = 1 Lr CD r1 = R vC D R 2 (t) = where CD R Lr CD R . IL f (t1 ) Vin − sin ω1 (t − t1 ) (5) K Zr 1 CHEN et al.: ZERO-VOLTAGE-SWITCHING PWM FULL-BRIDGE CONVERTER EMPLOYING AUXILIARY TRANSFORMER Fig. 2. 1151 Key waveforms of the classical ZVS PWM FB converter with clamping diodes under light-load condition. (a) Case I. (b) Case II. Substitution of (5) into (3) and (4), leads to iD R 1 (t) = IL f (t1 ) − iC D R 2 (t) = KVin sin ω1 (t − t1 ) 2Zr 1 KVin sin ω1 (t − t1 ). 2Zr 1 VC B (t1 ) = (7) (8) According to (5) and (6), we can know that if IL f (t1 )/K ≥ Vin /Zr 1 , iL r is still positive when vC D R 2 reduces to zero. After that, the converter will operate in freewheeling state. It can be seen that there is no current flowing through the clamping diodes, just like that under heavy-load condition, which is not discussed here. There are two possible cases that depends on the value of IL f (t1 ) when IL f (t1 )/K < Vin /Zr 1 . Case I: 0.5 Vin /Zr 1 ≤ IL f (t1 )/K < Vin /Zr 1 . Referring to (5)–(7), if 0.5 Vin /Zr 1 ≤ IL f (t1 )/K < Vin /Zr 1 , when vC D R 2 reduces to zero at t2 , iL r and ip are negative, and iD R 1 is still positive, so both the output rectifier diodes conduct, as shown in Fig. 3(d). iL r is IL r (t2 ) = IL f (t1 ) Vin − . K Zr 1 (9) After t2 , iL f decreases linearly and iL r and ip remain unchanged. At t2 , iL f decreases to −Kip and iD R 1 decreases to zero correspondingly. Then, CD R 1 tends to be charged, and the voltage of node C will be lower than zero, thus D6 conducts, clamping the voltage of node C at zero. After t2 , both ip and iL f decrease linearly, the difference of iL r and ip flows through D6 , as shown in Fig. 3(e). At t3 , iL f decreases to zero, then iL r freewheels through Q3 and D6 , Lf resonates with CD R 1 paralleling with CD R 2 , as shown in Fig. 3(f). Case II: IL f (t1 )/K < 0.5Vin /Zr 1 . Referring (5)–(7), if IL f (t1 )/K< 0.5 Vin /Zr 1 , when iD R 1 decreases to zero at t1 , CD R 2 is not fully discharged, and ip , iL r , and vC B are IL r (t1 ) = Ip (t1 ) = −IL f (t1 ) K (10) Vin2 − 2IL f (t1 )Zr 1 K 2 . (11) After t1 , DR 1 turns off and CD R 1 is charged, and CD R 2 is still discharged. Lr resonates with CD R 1 and CD R 2 , thus leading to the decrease of vrect and vC B . ip and iL r continue to increase in the negative direction, as shown in Fig. 3(g), which can be further , CD , and iL f are the simplified as Fig. 4(b), where CD R1 R2 reflected CD R 1 , CD R 2 , and iLf to the primary side, respectively, = CD = 4CD R K 2 . ip , iL r , and vC B are given by and CD R1 R2 √ VC B (t ) iL r (t) = ip (t) = − √ 1 sin( 2ω1 (t − t1 )) 2Zr 1 √ IL (t1 ) − f cos( 2ω1 (t − t1 )) K √ vC B (t) = VC B (t1 ) cos( 2ω1 (t − t1 )) (12) √ IL f (t1 ) √ 2Zr 1 sin( 2ω1 (t − t1 )). (13) K When vC D R 2 reduces to be equal to vC D R 1 at t1 , both the primary and secondary voltages of the transformer reduce to zero, thus the voltage of node C reduces to zero and D6 conducts, as shown in Fig. 3(h). CD R 1 and CD R 2 share iL f , leading to decrease in vrect and keeping ip at zero. At t1 , iL r reaches its peak value −IL r p and flows through Q3 and D6 . According to (12) and (13), −IL r p can be expressed as IL f (t1 ) 2 VC2 B (t1 ) −IL r p = IL r (t1 ) = − + . (14) 2Zr21 K − Substitution of (11) into (14), leads to IL f (t1 ) 2 Vin2 IL r p = − . 2Zr21 K (15) After t1 , CD R 1 and CD R 2 share iL f , leading to decrease in vrect and keeping ip at zero. The equivalent circuit of the mode is shown in Fig. 3(h). At t2 , vrect reduces to zero and DR 1 and DR 2 share iL f , as shown in Fig. 3(i). At t3 , iL f decreases to 1152 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 Fig. 3. Equivalent circuits of the classical FB converter under light-load condition. (a) Prior to t0 . (b) [t0 , t1 ]. (c) After t1 . (d) [t2 , t2 ] (case I). (e) [t2 , t3 ] (case I). (f) [t3 , t4 ] (g) [t1 , t1 ] (case II). (h) [t1 , t2 ] (case II). (i) [t2 , t3 ] (case II). (j) [t4 , t5 ]. Fig. 4. Further simplified equivalent circuits of Fig. 3(c), (g), and (j). CHEN et al.: ZERO-VOLTAGE-SWITCHING PWM FULL-BRIDGE CONVERTER EMPLOYING AUXILIARY TRANSFORMER Fig. 5. 1153 Possible clamping-diode current reset schemes. zero, then iL r freewheels through Q3 and D6 , Lf resonates with CD R 1 paralleling with CD R 2 , the equivalent circuit is the same as Fig. 3(f). It can be seen that no matter at case I or case II, the converter passes by the same mode, as shown in Fig. 3(f). According to (15), we know that the smaller IL f (t1 ) is, the larger IL r p is. Assuming that IL f (t1 ) = 0, which means noload condition, we can get IL r p m ax Vin =√ . 2Zr 1 der heavy-load condition, and the critical current is IL f (t1 ) = KVin /Zr 1 . Under light-load condition, the primary current will change its direction during zero state and the clamping diode will conduct for almost half of the switching period. Besides the unavoidable serious reverse recovery of the clamping diodes, the phenomenon also causes large conduction loss on the clamping diodes and leading-leg switches. Therefore, it is necessary to reset the clamping diode current to zero rapidly over the full-load range. (16) Based on the critical condition of case I and (9), we can get that the maximum value of |iL r | in case I is 0.5 Vin /Zr 1 . Based on the critical condition of case II and (15), we can get that the minimum and√maximum values of |iL r | in case II are 0.5Vin /Zr 1 and Vin /( 2Zr 1 ), respectively. From the aforementioned analysis, we can conclude that under light-load condition, the resonant inductor current will change its direction and freewheels during zero state (vA B = 0), and the smaller the load current is, the larger the resonant inductor current. For both case I and case II, prior to t4 , D6 conducts and iL r remains almost unchanged. At t4 , Q4 is turned off and Q2 is turned on with hard switching, then CD R 1 is charged, vrect increases accordingly, ip also increases rapidly, forcing the clamping diode current iD 6 to decline acutely. The equivalent circuit of the mode is shown in Fig. 3(j) and the further simplified equivalent circuit is show in Fig. 4(c). In other words, if ignore the leakage inductor of the transformer, all the input voltage Vin is applied on D6 at t4 , forcing D6 to be hardly turned off. Therefore, D6 suffers from serious reverse recovery and large losses and it may be even destroyed. At t5 , Vrect increases to Vin /K and the voltage of node C reduce to zero. Then, ip declines downward to the reflected filter inductor current and increases linearly almost from zero due to the very short time interval of [t4 , t5 ]. iL r remains almost unchanged and the difference of iL r and ip flows through D6 (this is the reason that why the clamping diode conducts during active state (vA B = +Vin or − Vin ) under light-load condition). It can be found that the longest conduction time for the clamping diode is nearly half of the switching period in this case. From aforementioned analysis, it can be seen that the operation principle of the FB converter with clamping diodes under light-load condition is remarkably different from that un- III. CLAMPING DIODE CURRENT RESETTING SCHEME IN FB CONVERTER As discussed in Section II, the decline rate of the clamping diode current depends on the rise rate of the output filter inductor current. The output filter inductor is always intentionally reduced to increase the decline rate of the clamping diode current, resulting in larger current ripple across the output filter inductor. In order to reset the clamping diode current rapidly, a reset voltage source can be brought into the current loop, and it can be connected in series with the resonant inductor or the clamping diodes. Fig. 5(a) shows that the reset voltage source vreset is connected in series with the resonant inductor. The polarity of vreset must comply with the direction of the resonant inductor current iL r , i.e., when iL r is positive, vreset should be positive; and when iL r is negative, vreset should be negative. Such vreset can be implemented by a transformer reset winding [12]. The voltage polarity of the reset winding complies with the primary winding voltage of the transformer, as well as the resonant inductor current, and it can effectively reset the clamping diode current. However, the reset winding voltage is directly linked to the primary duty cycle, and it will lose its function when the primary duty cycle is relatively small. Fig. 5(b) shows that two independent reset voltage sources are connected in series with the clamping diodes, respectively, where each reset voltage source is unipolar because the clamping diode current is unidirectional. Practically, the two reset voltage sources can be implemented by a resistor or a Zener diode. The voltage drop on the resistor or Zener diode plays the role of the reset voltage source when the clamping diode current flows through them. However, the excessive energy stored in the resonant inductor is dissipated in the resistor or Zener diode, leading to a reduced efficiency. 1154 Fig. 6. IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 ZVS PWM FB converter with auxiliary transformer. The two independent reset voltage sources, shown in Fig. 5(b), can be replaced by a single reset voltage source because they do not work at the same time, as shown in Fig. 5(c). Similar to Fig. 5(a), the polarity of the reset voltage source shown in Fig. 5(c) must also comply with the direction of the current flowing through it. Two concrete cases for Fig. 5(c) are presented in [10], where a resistor or two back-to-back Zener diodes are adopted as the reset voltage source. However, all the excessive energy stored in the resonant inductor will be dissipated in the resistor or Zener diodes. In our previous work [14], a current transformer is introduced to the FB converter as the reset voltage source. Based on [14], an improved scheme of resetting the clamping diode current to zero is proposed for the ZVS PWM FB converter with an auxiliary circuit consisting of only one auxiliary transformer and two diodes, which is simpler than the current transformer proposed in [14]. The improved scheme can shorten the clamping-diode conduction time over the full-load range, leading to natural turn-OFF of the clamping diodes, and meanwhile, the excessive energy stored in the resonant inductor is delivered to the input voltage source, thus a potentially high efficiency is expected. IV. OPERATION PRINCIPLE OF THE ZVS PWM FB CONVERTER WITH AUXILIARY TRANSFORMER The proposed ZVS PWM FB converter with auxiliary transformer is shown in Fig. 6. The primary winding of the auxiliary transformer Ta is inserted between nodes C and D, where node C is the connecting point of the primary winding of the main transformer and Lr , and node D is the connecting point of D5 and D6 . The secondary winding of the auxiliary transformer is inserted between nodes D and E, where node E is the connecting point of the introduced auxiliary diodes Da1 and Da2 . The turns ratio of the auxiliary transformer is kat = n1 /n2 . The location of Lr and Tr in Fig. 6 can also be exchanged; however, the scheme shown in Fig. 6, where Tr connecting with the lagging leg, is an optimal one, as discussed in [10] and [11]. A. Operation Principle Under Heavy-Load Condition Fig. 7 gives the key waveforms of the ZVS PWM FB converter with auxiliary transformer operating under heavy-load condition. The equivalent circuits of each switching modes in a half period are shown in Fig. 8. The second half period is similar to the first half period. Fig. 7. Key waveforms of the FB converter with auxiliary transformer under heavy-load condition. Mode 1 [t0 , t1 ] [see Fig. 8(a)]: Prior to t0 , the power is transferred from the input voltage source Vin to the load. At t0 , Q1 is turned off with zero voltage, due to C1 and C3 , which limit the rise rate of the voltage across Q1 . iL r charges C1 and discharges C3 , and the potential voltage of point A decays. In the meanwhile, the capacitor CD R 2 is discharged. As the potential voltage of point C is greater than zero, D6 is reverse biased. The voltage of C3 decreases to zero at t1 and D3 conducts naturally. Mode 2 [t1 , t2 ] [see Fig. 8(b)]: At t1 , Q3 can be turned on with zero voltage. CD R 2 continues to be discharged. iL r and ip continue decaying. This mode finishes when the voltage of point C reduce to zero. Mode 3 [t2 , t3 ] [see Fig. 8(c)]: During this mode, iL r is equal to ip , and the converter operates in freewheeling state. Mode 4 [t3 , t4 ] [see Fig. 8(d)]: At t3 , Q4 is turned off with zero voltage due to C2 and C4 , which limit the rise rate of the voltage across Q4 . C4 is charged and C2 is discharged in a resonant manner. Mode 5 [t4 , t6 ] [see Fig. 8(e)]: At t4 , C2 is fully discharged, and D2 conducts naturally, thus Q2 can be turned on with zero voltage. iL r is equal to ip , and both of them decay linearly with the rate of Vin /Lr . At t5 , iL r and ip cross zero and continue to increase linearly in the negative direction. The load current flows through both the output rectifier diodes. Mode 6 [t6 , t7 ] [see Fig. 8(f)]: At t6 , ip increases to the reflected current of iL f , and DR 1 turns off and DR 2 continues conducting. Lr resonates with CD R 1 after t6 , and CD R 1 is charged in a resonant manner, ip and iL r continue increasing, and vrect increases. The voltage of the primary winding vB C increases and the voltage of node C is reduced accordingly because the voltage of node B is Vin . The further simplified CHEN et al.: ZERO-VOLTAGE-SWITCHING PWM FULL-BRIDGE CONVERTER EMPLOYING AUXILIARY TRANSFORMER 1155 Fig. 8. Equivalent circuits of the FB converter with auxiliary transformer under heavy-load condition. (a) [t0 , t1 ]. (b) [t1 , t2 ]. (c) [t2 , t3 ]. (d) [t3 , t4 ]. (e) [t4 , t6 ]. (f) [t6 , t7 ]. (g) [t7 , t8 ]. (h) [t8 , t9 ]. Fig. 9. Further equivalent circuits under heavy-load condition. (a) [t6 , t7 ]. (b) [t7 , t8 ]. equivalent circuit of this mode is shown in Fig. 9(a), where CD R , iL f are the reflected CD R 1 and iL f to the primary side, respectively. vrect and ip are given by Vin vB C (t) = [1 − cos ω1 (t − t6 )] (17) K K IL (t6 ) Vin sin ω1 (t − t6 ) + f ip (t) = iL r (t) = − . Zr 1 K vrect (t) = (18) Here, iL f is considered to be unchanged because the interval of this mode is very short. At t7 , vrect rises to (Vin + kat Vin )/K, and the primary voltage of the transformer vB C is Vin + kat Vin , the potential voltage of node C reduces to −kat Vin , thus D6 conducts, clamping vB C at Vin + kat Vin , and vrect is clamped at (Vin + kat Vin )/K, accordingly, i.e., Vrect (t7 ) = Vin Vin + kat Vin [1 − cos ω1 (t7 − t6 )] = . K K (19) 1156 Fig. 10. IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 Key waveforms of the FB converter with auxiliary transformer under light-load condition. (a) Case I. (b) Case II. Combining (18) and (19), yields IL f (t6 ) Vin 2 1 − kat + IL r (t7 ) = − . Zr 1 K (20) Mode 7 [t7 , t8 ] [see Fig. 8(g)]: At t7 , as D6 conducts, ip declines downward to the reflected output filter inductor current and increases in the negative direction. The clamping diode current flows into the primary winding of the auxiliary transformer, and the reflected current flows through Da1 to Vin , and their current can be expressed as iD 6 (t) = (1 + kat ) [|IL r (t7 )| − |ip (t)|] iD a1 (t) = kat [|IL r (t7 )| − |ip (t)|] . (21) (22) The induced voltage vC D equals to −kat Vin , which is applied to Lr , forcing iL r to decrease quickly. |iL r | is greater than |ip | before t8 , and the difference of iL r and ip flows through D6 . The further simplified equivalent circuit of this stage is shown in Fig. 9(b). At t7 , iD 6 is Vin 2 . ID 6 (t7 ) = (1 + kat ) 1 − kat (23) Zr 1 And, the decline rate of the resonant inductor current is diL r kat Vin = . dt Lr (24) Assume that the output filter inductor is infinite, thus the decline rate of the resonant inductor current is the decline rate of iD 6 . From (23) and (24), the conduction time of D6 is t8 − t 7 = Lr ID 6 (t7 ) ID 6 (t7 ) = . diL r /dt kat Vin (25) Mode 8 [t8 , t9 ] [see Fig. 8(h)]: At t8 , iL r decays to ip and D6 and Da1 turn-OFF naturally. During this mode, Lr resonates with CD R 1 . The rectified voltage vrect is given by vrect (t) = kat Vin Vin + cos ω1 (t − t8 ). K K (26) Equation (26) illustrates that the maximum value of vrect will never exceed (Vin + kat Vin )/K, though slight oscillation exists. In practice, vrect will finally converge to the average value Vin /K, since the inherent parasitic resistor exists in the power stage, which will be presented in Section VI. B. Operation Principle Under Light-Load Condition The detailed operation principle of the proposed ZVS PWM FB converter under light-load condition is relatively complex compared with that under heavy-load condition, just like the classical FB converter presented in Section II. Because the ZVS PWM FB converter with auxiliary transformer has the same operation states as that of the classical FB converter when the clamping diodes are reversely biased, hence, only the states in which the clamping diodes conduct will be discussed. The key waveforms of the ZVS PWM FB converter with auxiliary transformer under light-load condition are shown in Fig. 10 (there are two cases depending on the load). Case I: 0.5 Vin /Zr 1 ≤ IL f (t1 )/K < Vin /Zr 1 . Referring to Fig. 10(a), prior to t2 , both the output rectifier diodes conduct, iL f decreases linearly and iL r and ip remain unchanged, the equivalent circuit is similar to Fig. 3(d). At t2 , iD R 1 decreases to zero and iL f only flows through DR 2 , and iL f decreases to the reflected ip . Then, CD R 1 is charged, and the voltage of node C is lower than zero. When the voltage of node C reduces to −kat Vin , D6 conducts. iD 6 flows out of the dot side of the primary winding of the auxiliary transformer. Thus, the reflected current on the secondary side of the auxiliary transformer flows into the dot side, forcing Da1 to conduct and Da2 to block. The induced voltage vC D equals to −kat Vin , and it forces iL r to decrease rapidly. The equivalent circuit is shown in Fig. 11(a). At t3 , both iL f and ip decrease to zero, then Lf resonates with CD R 1 paralleling with CD R 2 , D6 continues conducting, as shown in Fig. 11(b). The peak value of the clamping diode current is approximate IL r p because the interval [t2 , t3 ] is very short. D6 still conducts until t3 when iL r decreases to zero. CHEN et al.: ZERO-VOLTAGE-SWITCHING PWM FULL-BRIDGE CONVERTER EMPLOYING AUXILIARY TRANSFORMER 1157 Fig. 11. Equivalent circuits of the FB converter with auxiliary transformer under light-load condition. (a) [t2 , t3 ] (case I). (b) [t3 , t3 ] (case I). (c) [t4 , t5 ] (case I). (d) [t5 , t6 ] (case I). (e) [t2 , t3 ] (case II). At t4 , Q4 is turned off and Q2 is turned on with hard switching, then CD R 1 is charged, vrect increases accordingly, ip and iL r also increase rapidly. The equivalent circuit of the mode is shown in Fig. 11(c). Compared with the same mode of the classical FB converter shown in Fig. 3(j), it can be seen that D6 has been turned off before this mode; therefore, no serious reverse recovery occurs in the clamping diode in the FB converter with auxiliary transformer. At t5 , vrect rises to (Vin + kat Vin )/K, and the potential voltage of node C reduces to −kat Vin , thus D6 conducts. iL r will reduces to ip rapidly. The equivalent circuit of the mode is shown in Fig. 11(d). The other modes are similar to the classical FB converter. Case II: IL f (t1 )/K < 0.5 Vin /Zr 1 . Referring to Fig. 10(b), If IL f (t1 )/K < 0.5Vin /Zr 1 , iD R 1 will decrease to zero earlier than vC D R 2 at t1 , then Lr resonates with the CD R 1 and CD R 2 , leading to the decrease of vrect and vC B , as shown in Fig. 4(b). Then, the voltage of node C reduces to zero and iL r reaches its peak value −IL r p at a given time t2 , when the voltage of node C reduces to −kat Vin , D6 will conduct. The peak value of the clamping diode current is approximate IL r p because kat Vin is relatively smaller than Vin . iD 6 flows out of the dot side of the primary winding of the auxiliary transformer. Thus, the reflected current on the secondary side of the auxiliary transformer flows into the dot side, forcing Da1 to conduct and Da2 to block. The induced voltage vC D equals to −kat Vin , and it forces iL r to decrease rapidly. Since the primary winding voltage of Tr is clamped by the auxiliary transformer and D6 , CD R 1 and CD R 2 share the current of Lf , leading to the decrease in vrect and keeping ip at zero. The equivalent circuit of the mode is shown in Fig. 11(e). vrect is given by kat Vin kat Vin > (27) K K 2vC B (t) vC D R 2 (t) − vC D R 1 (t) = < 0. (28) K Therefore, vC D R 2 will be first discharged to zero. At t3 , vC D R 2 equals to zero, thus DR 2 conducts. Then, iL f decreases linearly. If iL f decreases to zero before t5 , Lf will resonate with CD R 1 paralleling with CD R 2 , as shown in Fig. 10(b). After t3 , DR 2 conducts and vrect remains at kat Vin /K. D6 still conducts, forcing iL r to decrease. ip equals to the reflected current of iL f , and the equivalent circuit is the same as Fig. 11(a). D6 still conducts until t4 , when iL r decreases to zero. After t4 , the modes are similar to that of case I. It can be seen that the clamping diode current is forced to decline rapidly under light-load condition in the proposed FB converter, reducing the conduction loss and avoiding the reverse recovery of the clamping diodes. In the aforementioned analysis, the magnetizing inductor of the main transformer is regarded as infinite and its effect on the operation principle of the ZVS FB converter is ignored. In [9], it is pointed out that the magnetizing inductor of the main transformer has a substantial effect on the light-load condition operation, and a relatively low magnitude of the magnetizing inductor helps maintaining ZVS for switches under light-load condition. The magnetizing inductor current flows through the lagging-leg switch and the corresponding clamping diode and vrect (t) = vC D R 2 (t) + 1158 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 remains unchanged at zero state (vA B = 0) under light-load condition in classical FB converter, for example, in Fig. 3(e) or (g), the magnetizing inductor current will flow through Q4 and D6 and under freewheeling state. When the classical FB converter transits from zero state (vA B = 0) to active state (vA B = +Vin or −Vin ), the energy stored in the magnetizing inductor can be used to achieve ZVS for switches, as presented in [9]. In the proposed ZVS PWM FB converter with auxiliary transformer, the auxiliary transformer will play its role and transfer the energy stored in the magnetizing inductor to the input voltage source when the magnetizing current flows through the clamping diode under light-load condition, and the magnetizing current will reduce to zero rapidly. Hence, the low magnetizing inductor is not effective for soft switching under light-load condition. Under heavy-load condition, the magnetizing inductor current flows through the lagging-leg switch and the corresponding leadingleg switch at zero state (vA B = 0), and the auxiliary transformer has no influence on the magnetizing inductor current; therefore, the low magnetizing inductor is helpful to achieve ZVS for switches [15]. V. THEORETICAL ANALYSIS A. Conduction Loss Under heavy-load condition, before the auxiliary transformer is introduced, when the clamping diode conducts, the resonant inductor is shorted and its current remains constant, the difference between the resonant inductor current and the primary current flows through the clamping diode. The conduction time of the clamping diode depends on the rise rate of the output filter inductor current. The output filter inductor is usually quite large; therefore, the conduction time of the clamping diode is very long. Under light-load condition, before the auxiliary transformer is introduced, the clamping diode keeps conducting almost half of the switching period. When the auxiliary transformer is introduced, the reset voltage is applied to the resonant inductor when the clamping diode conducts, forcing iL r to decay rapidly, so the clamping diode current declines to zero rapidly correspondingly and its average value is also reduced, as well as the RMS current of the leadingleg switch. Hence, the conduction loss in the primary side is reduced. B. Clamping Diode 1) Heavy-load condition: Equation (23) demonstrates the peak current of clamping diode; generally, kat Vin is smaller than Vin by choosing kat properly. Hence, the peak current of clamping diode can be obtained according to (23), i.e., Vin 2 ≈ Vin . 1 − kat (29) Ip h = (1 + kat ) Zr 1 Zr 1 It can be seen that the peak current is independent of the load current, and it depends on the input voltage, the characteristic impedance of the resonant inductor, and the junction capacitor of the output rectifier diode. Equation (25) shows the clamping-diode conduction time, combining (23), (25) and (29), the clamping-diode conduction time is given as Tc h = 1 . kat ω1 (30) 2) Light-load condition: According to Fig. 10, the peak current of clamping diode under light-load condition equals to IL r p . From aforementioned analysis, it can be seen that IL r p depends on IL f (t1 ), which reflects the different load current under light-load condition. According to (9) and (15), the maximum value of IL r p appears under no-load condition, i.e., Ip l m ax Vin =√ . 2Zr 1 (31) The maximum clamping-diode conduction time is given by Tc l m ax =√ 1 . 2kat ω1 (32) C. Output Rectifier Diode The voltage stress of the output rectifier diode in the FB converter with auxiliary transformer is 2(Vin + kat Vin )/K, which is slightly higher than the classical FB converter, and the difference is Vin 2kat Vin Vin + kat Vin −2 = . (33) ∆V = 2 K K K D. Design Considerations of the Auxiliary Transformer From (30), (32) and (33), we can see that the larger kat is, the shorter the clamping-diode conduction time; however, the higher the voltage stress of the output rectifier diode. Therefore, there is a tradeoff in the choice of kat . Under light-load condition, referring to Fig. 10, the conduction time of the clamping diode must be lesser than the time interval of zero state to avoid the reverse recovery of the clamping diode. Generally, the primary duty cycle is relatively smaller under light-load condition, hence, we have Ts Ts (1 − D) ≈ (34) 2 2 where D is the primary duty cycle of the FB converter. Assume that maximum clamping-diode conduction time under light-load condition is 10% of the switching period, and we get Tc l m ax < Tc l m ax =√ 1 Ts . < 10 2kat ω1 (35) In order to get the concrete design process, a prototype is designed and built with the following parameters: r input voltage Vin : 270(±10%) Vdc ; r output voltage Vo : 54 Vdc ; r maximum output current Io : 20 A; r switching frequency fs : 100 kHz; r resonant inductor Lr : 9 µH; r output filter inductor Lf : 23 µH; CHEN et al.: ZERO-VOLTAGE-SWITCHING PWM FULL-BRIDGE CONVERTER EMPLOYING AUXILIARY TRANSFORMER 1159 Fig. 12. Waveforms comparison of four kinds of FB converters at full-load condition (Io = 20 A). (a) Classical FB converter [11]. (b) With reset winding [12]. (c) With back-to-back Zener diodes [10]. (d) FB converter with auxiliary transformer. r r r r r main switches Q1 −Q4 : IRFP450; clamping diodes D5 −D6 : DSEI 30–06 A; output rectifier diodes DR 1 −DR 2 : DSEP 30–03 A; turns ratio K: 15:4; reflected capacitor CD : 600 pF, which is approximately calculated from the experimental results. According to (35), we can get that kat should be larger than 0.052. VI. EXPERIMENTAL VERIFICATION A prototype with 54 V/20 A output of the ZVS PWM FB converter with auxiliary transformer was built and tested to verify the operation principle. The turns ratio of the auxiliary transformer is 6: 77, which means kat = 0.078. A ring Mn– Zn ferrite core (10 K, 12.7 mm × 7.9 mm × 7 mm) is used. BYV26 C (PHILIPS) is taken as the auxiliary diode Da1 and Da2 and the other parameters are the same as listed in Section V. For the purpose of comparison, a classical FB converter with clamping diodes [11], a FB converter with reset winding, where the main transformer turns ratio is n1 :n3 :n2 = 14:1:4 [12], and an FB converter using back-to-back Zener diodes (1N4747) as the reset voltage source [10] were all built in laboratory. Fig. 12 shows the waveforms of vA B , ip , iL r , iD 5 , iD 6 , and vrect (from the top to the bottom) of the four kinds of FB con- verters at full load under the nominal input voltage of 270 V. As seen in Fig. 12, compared with the classical FB converter, the conduction time of the clamping diode in the other three kinds of FB converters are all shortened under heavy-load condition. Fig. 13 shows the waveforms of the four kinds of FB converters at light load (Io = 30 mA) under the nominal input voltage of 270 V. It can be seen from Fig. 13(a) that if no reset voltage is added, the two clamping diodes conduct for nearly half of the switching period alternately. When the converter transits from zero state (vAB = 0) to active state (vAB = +Vin or −Vin ), the clamping diodes are turned off with reverse recovery and are apt to be destroyed, which deteriorates the reliability of the converter dramatically, especially in high input voltage application. As seen in Fig. 13(b), the reset winding can not decay the clamping diode current during zero state because the primary winding voltage of the main transformer is clamped at zero under light-load condition. Hence, when the converter transits from zero state to active state, the clamping diodes are in conduction state and will be turned off hard, suffering from reverse recovery. During active state, the clamping diode current is declined to zero rapidly. Fig. 13(c) shows the waveforms of the FB converter using back-to-back Zener diodes as the reset voltage source, it can be seen that this method is effective at resetting the clamping diode currents under light-load condition. 1160 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 Fig. 13. Waveforms comparison of four kinds of FB converters at light-load condition (Io = 30 mA). (a) Classical FB converter [11]. (b) With reset winding [12]. (c) With back-to-back Zener diodes [10]. (d) FB converter with auxiliary transformer. Fig. 14. Q4 . Waveforms of the leading switch and the lagging switch. (a) v G S , v D S , and iD of the leading switch Q 1 . (b) v G S , v D S , and iD of the lagging switch Fig. 13(d) shows the waveforms of the FB converter with auxiliary transformer. It can be seen that the clamping diode current decay rapidly without reverse recovery and the conduction time is shortened. Fig. 14(a) and (b) show the waveforms of the gate–source voltage vG S , the drain–source voltage vD S , and the drain current iD of Q1 and Q4 , respectively. It can be seen that all switches realize ZVS. Fig. 15 shows the comparison in the conversion efficiency of four kinds of FB converters. Fig. 15(a) shows the efficiency at different output currents under normal input voltage of 270 V. Fig. 15(b) shows the efficiency at full load under different CHEN et al.: ZERO-VOLTAGE-SWITCHING PWM FULL-BRIDGE CONVERTER EMPLOYING AUXILIARY TRANSFORMER 1161 Fig. 15. Efficiency comparison of four kinds of FB converters. (a) Efficiency at different output currents under normal input voltage. (b) Efficiency at full load under different input voltages. input voltages. It can be seen that the efficiency of the FB converter with reset winding and the FB converter with auxiliary transformer is higher than that of the classical FB converter due to the reduced conduction loss of the clamping diodes, the leading switches, and the resonant inductor. The efficiency of the FB converter with back-to-back Zener diodes is almost the same as that of the classical FB converter, the reason is that the reduced losses of the clamping diodes and the leading switches are transferred to the two back-to-back Zener diodes, and the total losses are almost the same. It should also be noted that the back-to-back Zener diodes method is effective at resetting the clamping diode currents under light-load condition. Compared with the FB converter with auxiliary transformer, the FB converter with reset winding has relatively higher efficiency due to no lossy device and component needed. VII. CONCLUSION The operation principle of the classical FB converter with clamping diodes under light-load condition is analyzed in detail, which is remarkable different from that under heavy-load condition. It is shown that the primary current will change its direction during zero state and the clamping diode will conduct for almost half of the switching period under light-load condition, which causes large conduction loss on the clamping diodes and leading-leg switches and unavoidable serious reverse recovery of the clamping diodes. A new ZVS PWM FB converter with high reliability and reduced conduction loss is proposed to overcome aforementioned problems, which employs an additional auxiliary transformer to make the clamping diode current decay rapidly over the full-load range, thus the conduction losses of the clamping diodes, the leading switches, and the resonant inductor are reduced and the conversion efficiency can be increased. In the meanwhile, the clamping diodes can be turned off naturally without reverse recovery over the whole input voltage range and load range, hence, the reliability of the FB converter is improved. The operation principles, features, and comparisons are illustrated. The experimental results from the prototype are shown to verify the feasibility of the proposed converter. REFERENCES [1] X. Ruan and Y. Yan, “Soft-switching techniques for PWM full bridge converters,” in Proc. IEEE Power Electron. Spec. Conf. (PESC 2000), pp. 634–639. [2] X. Wu, J. Zhang, X. Xie, and Z. Qian, “Analysis and optimal design considerations for an improved full bridge ZVS DC–DC converter with high efficiency,” IEEE Trans. Power Electron., vol. 21, no. 5, pp. 1225– 1234, Sep. 2006. [3] K.-B. Park, C.-E. Kim, G.-W. Moon, and M.-J. Youn, “Voltage oscillation reduction technique for phase-shift full-bridge converter,” IEEE Trans. Ind. Electron., vol. 54, no. 5, pp. 2779–2790, Oct. 2007. [4] B. P. McGrath, D. G. Holmes, P. J. McGoldrick, and A. D. McIve, “Design of a soft-switched 6-kW battery charger for traction applications,” IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1136–1144, Jul. 2007. [5] Y. Jang and M. M. Jovanović, “A new PWM ZVS full-bridge converter,” IEEE Trans. Power Electron., vol. 22, no. 3, pp. 987–994, May 2007. [6] C. Zhao, X. Wu, P. Meng, and Z. Qian, “Optimum design consideration and implementation of a novel synchronous rectified soft-switched phase-shift full-bridge converter for low-output-voltage high-output-current applications,” IEEE Trans. Power Electron., vol. 24, no. 2, pp. 388–397, Feb. 2009. [7] B. O. Blair, G. H. Fasullo, J. E. Harvey, and D. Marabell, “DC/DC ZVS full bridge converter power supply method and apparatus,” U.S. Patent 6 483 724 B1, Nov. 19, 2002. [8] R. Redl, N. O. Sokal, and L. Balogh, “A novel soft-switching full-bridge DC/DC converter: analysis, design considerations, at 1.5 kW, 100 kHz,” IEEE Trans. Power Electron, vol. 6, no. 3, pp. 408–418, Jul. 1991. [9] R. Redl, L. Balogh, and D. W. Edwards, “Optimal ZVS full-bridge DC/DC converter with PWM phase-shift control: Analysis, design considerations, and experimental results,” in Proc. IEEE Appl. Power Electron. Conf. (APEC 1994), pp. 159–165. [10] R. Redl, L. Balogh, and D. W. Edwards, “Switch transitions in the soft switching full-bridge PWM phase-shift DC/DC converter: Analysis and improvements,” in Proc. INTELEC 1993, pp. 350–357. [11] X. Ruan and F. Liu, “An improved ZVS PWM full-bridge converter with clamping diodes,” in Proc. IEEE Power Electron. Spec. Conf. (PESC 2004), pp. 1476–1481. [12] W. Chen and X. Ruan, “A novel zero-voltage-switching PWM full bridge converter,” IEEE Trans. Power Electron., vol. 23, no. 2, pp. 793–801, Mar. 2008. [13] L. Yin, Q. Chen, B. Peng, J. Wang, and X. Ruan, “Key issues of clamping diodes in DCM phase-shift full-bridge converter,” in Proc. IEEE Power Electron. Spec. Conf. (PESC 2007), pp. 1721–1725. [14] Q. Chen, L. Yin, J. Wang, B. Peng, S. C. Wong, X. Ruan, and X. Chen, “Phase-shifted full-bridge PWM converter with clamping diodes and current transformer,” in Proc. IEEE Power Electron. Spec. Conf. (PESC 2008), pp. 2403–2409. [15] Z. Zhang, W. Eberle, Y. F. Liu, and P. C. Sen, “A novel non-isolated ZVS asymmetrical buck voltage regulator module with direct energy transfer,” IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 3096–3105, Aug. 2009. 1162 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 5, MAY 2010 Wu Chen (S’05) was born in Jiangsu Province, China, in 1981. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 2003, 2006 and 2009, respectively. He is currently a Senior Research Assistant with the Department of Electronic Engineering, City University of Hong Kong, Hong Kong, China. His research interests include soft-switching dc/dc converters, inverters, and power electronic system integration. Xinbo Ruan (M’97–SM’02) was born in Hubei, China, in 1970. He received the B.S. and Ph.D. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 1991 and 1996, respectively. In 1996, he was with the Faculty of Electrical Engineering Teaching, and Research Division, NUAA, where he was a Professor in 2002 with the College of Automation Engineering and has been engaged in teaching and research in the field of power electronics. From August to October 2007, he was a Research Fellow with the Department of Electronics and Information Engineering, Hong Kong Polytechnic University, Hong Kong, China. He is a Guest Professor with Beijing Jiaotong University, Beijing, China and Hefei University of Technology, Hefei, China. Since March 2008, he has been with the College of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China. His current research interests include soft-switching dc/dc converters, soft-switching inverters, power factor correction converters, modeling the converters, power electronics system integration, and renewable energy generation system. He has authored or coauthored more than 100 technical papers in journals and conferences and three books. Dr. Ruan is a Senior Member of the IEEE Power Electronics Society and the IEEE Industrial Electronics Society. He was the Vice President of the China Power Supply Society, and from 2008, he has been a member of the Technical Committee on Renewable Energy Systems within the IEEE Industrial Electronics Society. He was the recipient of the Delta Scholar by the Delta Environment and Education Fund in 2003 and was awarded the Special Appointed Professor of the Chang Jiang Scholars Program, by the Ministry of Education, China, in 2007. Qianhong Chen (M’06) was born in Hubei, China, in 1974. She received the B.S., M.S., and Ph.D. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 1995, 1998 and 2001, respectively. From April 2007 to January 2008, she was a Research Associate with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hong Kong, China. Since 2001, she has been with the Faculty of Electrical Engineering, Teaching and Research Division, NUAA, where she is currently a Professor with the Aero-Power Sci-Tech Center, College of Automation Engineering. Her research interests include soft-switching dc/dc converters, application of integrated magnetics, and contactless resonant converters. Junji Ge was born in Jiangsu, China, in 1987. He received the B.S. degree in electrical engineering from Nanjing University of Aeronautics and Astronautics, Nanjing, China, in 2009, where he is currently working toward the M.S. degree in electrical engineering. His current research interests include softswitching dc–dc converters.