LAB – 1

advertisement

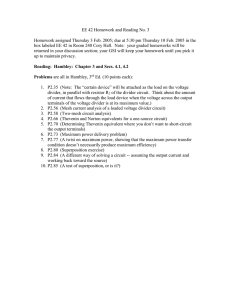

Lab 1: BJT biasing schemes and characterization of op-amp LAB – 1 BJT BIASING SCHEMES AND CHARACTERIZATION OF OPERATIONAL AMPLIFIER Experiment – 1.1 BJT biasing schemes Experiment – 1.2 Characterization of op-amp Experiment 1.1: BJT biasing schemes ►1. 2◄ EXPERIMENT-1.1 BJT BIASING SCHEMES 1.1 OBJECTIVE 1. To sketch potential divider bias and constant current bias schemes of a transistor and understand the operation of each circuit. 2. To analyze these BJT bias circuits to determine circuit voltage and current levels. 3. To design these bias circuits and select appropriate standard value components. 4. To trouble – shoot non-operational BJT bias circuits. 5. To discuss the thermal stability of BJT bias circuits and determine the effects of ICBO and VBE changes with temperature. 1.2 HARDWARE REQUIRED a. Power supply – Dual variable regulated low voltage DC source b. Equipments – CRO, AFO, DMM (Digital Multimeter), DRBs c. Resistors – d. Semiconductor – BC107 or equivalent e. Miscellaneous – Bread board and wires 1.3 INTRODUCTION Transistors used in amplifier circuits must be biased into an on state with constant (direct) levels of collection base and emitter current and constant terminal voltages. The levels of IC and VCE define the transistor dc operating point, or quiescent point. The circuit that provides this state is known as a bias circuit. Ideally, the current and voltage levels in bias circuits should remain absolutely constant. In practical circuits these quantities are affected by the transistor current gain (hFE) and by temperature changes. The best bias circuits have the greatest stability; they hold the currents and voltages substantially constant regardless of the hFE and temperature variations. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 3◄ 1.4 POTENTIAL DIVIDER BIAS Circuit Operation Vcc R1 Rc Q2 . + . VB . VCE . . VBE R2 RE . VC VE . . Fig. 1-1 Potential divider bias Potential divider bias is also known as emitter current bias, or voltage divider bias. A voltage divider bias circuit is shown in Fig. 1-1, and the current and voltage conditions throughout the circuit are illustrated. It is seen that the collector resistor (RC) and emitter resistor (RE) are connected in series with the transistor. Thus the total dc load in series with the transistor is (Rc+RE) and this total resistance must be used when drawing the dc load line for the circuit. Resistors R1 and R2 constitute a voltage divider that divides the supply voltage to produce the base bias voltage (VB). Voltage divider bias circuits are normally designed to have the voltage divider current (I2) very much larger than the transistor base current (IB). In this circumstance VB is larger unaffected by IB, so VB can be assumed to remain constant. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 4◄ Analysis Referring to fig. 1-1, VB = VCC x R2 / (R1 + R2) (1.1) With VB constant, the voltage across the emitter resistor is also a constant quantity, VE = VB – VBE (1.2) This means that the emitter current is constant, IE = (VB – VBE )/ RE (1.3) The collector current is approximately equal to the emitter current, so IC is held at a constant level. IC ≈ IE (1.4) The collector – emitter voltage is VCE = VC – VE (1.5) and the transistor collector voltage is VC = VCC – IC RC (1.6) VCE can also be determined as VCE ≈ VCC – IC (RC + RE) (1.7) Clearly with IC and IE constant, the transistor collector – emitter voltage remains at a constant level. It should be noted that the transistor hFE value is not involved in any of the above equations. DC load line and the bias point The values of IC and VCE specify the dc operating point (Q – point) and these values are written as ICQ and VCEQ respectively. For the known values of the components and supply voltage, we can analytically calculate the operating point. Another approach to find the Q – point is the graphical method. Here, we draw the straight line (the dc load line) from the above equation on the IC – VCE characteristics of the transistor as shown in Fig. 1-2. After calculating the base current, we identify the curve on the characteristics. The intersection of the load line with this characteristic curve gives the Q-point. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 5◄ Fig. 1-2 Graphical determination of Q point If the bias current changes, the Q-point will move on the load line because the characteristic curve will change. Potential divider bias circuit design Bias circuit design is just a matter of determining the required voltage across each resistor and the appropriate current levels. Then the resistor values are calculated by application of ohm’s law. Designs usually begin with specification of the supply voltage and the required levels of IC and VCE. The resistor values are calculated to meet these requirements, and standard value resistors are selected. When designing a voltage divider bias circuit the voltage divider current (I2 in Fig. 1-1) should be selected much larger than the transistor base current IB. This makes the base voltage VB a stable quantity largely unaffected by the transistor hFE value. However, a high level of I2 result in smaller resistance values for R1 and R2, and this gives the circuit undesirable low input impedance. A rule – of thumb approach to selection of I2 is to use a voltage divider current approximately equal to one – tenth of the transistor collector current. I2 = IC / 10 (1.8) EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 6◄ This gives reasonably large values for R1 and R2 while still keeping I2 much large than IB If VE is not specified, it should be selected much larger than the transistor VBE, VE >> VBE This is because VBE can vary from transistor to transistor, and it can also change with temperature increase or decrease. Making VE very much larger than VBE minimizes the effect of VBE changes on the circuit bias conditions. Typically, as another rule of thumb, VE is selected as 5v regardless of the supply voltage. When VCC is low, VE can be as low as 3V. The equations used for calculating each resistor value are: R1 = (VCC – VB) / I2 RC = (VCC – VCE – VE )/ IC R2 = VB / I2 RE ≈ VE / IC Design problem Design the voltage divider bias circuit to have VCE = VE = 5v and IC = 5mA when the supply voltage is 15v. Assume the transistor hFE is 100. Design procedure Vcc=+15V Rc 1K R1 18K 10V Q2 5.7V + + 5V - VBE 5V R2 12K RE 1K Fig 1-3 Voltage divider bias circuit designed RE = VE VE 5V ≅ = = 1KΩ (standard value) I E I C 5mA RC = (VCC − VCE − V E ) 15V − 5V − 5V = = 1KΩ (standard value) IC 5mA EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes From eq. (1.8), I 2 = ►1. 7◄ IC = 500 µA 10 From eq. (1.2), VB = VE+VBE = 5V+0.7V = 5.7V R2 = VB 5.7V = = 11.4 KΩ (use 12KΩ standard value) I 2 500 µA R1 = (VCC − V B ) 15V − 5.7V = = 18.6 KΩ (use 18kΩ standard value) I2 500 µA 1.5 TROUBLE – SHOOTING BJT BIAS CIRCUITS When a bias circuit is constructed in a laboratory situation, the supply voltage (VCC) and the voltage levels at the transistor terminals (VC VB and VE) should be measured with respect to the ground or negative supply terminal when the measured voltages are not as expected, the circuit must be further investigated to locate the fault. The following is a list of errors that commonly occur. • Power supply not switched on • Power supply current limiter control incorrectly set • Cables incorrectly connected to the power supply • VOM (volt – ohm – milliammeter) function incorrectly selected. • Wrong VOM terminals used. • Incorrect component connections • Resistor in wrong places. Figure (1.4) shows unsuitable measured voltages and probable errors in a voltage divider bias circuit. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes Vcc R1 open circuited ►1. 8◄ Rc short circuited R1 Transistors terminals open circuited Rc + Q2 VBE . Vc=Vcc R2 RE RE open circuited R2 short circuited . (a) Collector voltage equal to supply voltage Vcc R1 R1 & R2 interchanged Rc + - R2 open circuited . Q2 VBE R2 Transistor terminals short circuited RE . Vc=VE VE . . (b) Collector voltage equal to emitter voltage Fig. 1-4 Unsatisfactory measured voltages on a voltage divider bias circuit, and probable circuit faults. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 9◄ 1.6 THERMAL STABILITY OF BIAS CIRCUITS Thermal stability is the measure of how stable IC and VCE remain when the circuit temperature changes, sine many transistor circuits are required to operate over a wide temperature range. The base-emitter voltage (VBE) and the collectorbase reverse saturation current (ICBO) are the two temperature sensitive quantities that largely determine the thermal stability of a transistor circuit. The EB and CB junction have the temperature characteristics as stated below: • For a Si transistor, VBE changes by approximately -1.8 mV/oC • ICBO approximately doubles for every 10oC rise in temperature changes in ICBO and VBE produce • Significant changes in IC • Circuit Q point • Possibility of thermal runaway Stability factor The stability factor (S) of a circuit is the ration of the change in collector current to the change in collector – base leakage current. S = ∆IC / ∆ICBO or, ∆IC = S x ∆ICBO (1.9) The value of S depends on the circuit configuration and on the resistor values. A stability factor of 50 (or larger) is considered poor, while a factor of 10 or less is considered good. For voltage divider bias, the stability factor can be shown to be S =1+ h FE hFE R E 1+ R E + R1 R2 (1.10) The change in ICBO over a given temperature range can be calculated by recalling that ICBO doubles for every 10oC increase in temperature. The temperature change (∆T) is divided by 10 to give the number of 10oC changes (n). If the starting level of collector-base leakage current is ICBO (I), the new level is ICBO (2) = ICBO (1) x 2n (1.11) EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 10◄ The ICBO change and the circuit stability factor can be used to determine the change in IC. Then the resulting VCE change can be investigated. Effect of VBE change Consider the voltage divider bias circuit designed in Fig.1.3 From eq. (1.3), IC ≈ IE = (VB – VBE) / RE Assuming that VB remains substantially constant, an equation for IC change with VBE change can be writer as ∆IC ≈ ∆IE = ∆VBE / RE (1.12) when the change in IC is determined, then the result mg VCE change can be investigated. Example 1-1 Calculate the stability factors for the voltage divider bias circuit designed in Fig. 1.3. Also determine the IC change produced when the circuit temperature increase from 25oC to 125oC by the effect of (i) ICBO, which is equal to 15nA at 25oC (ii) VBE changes Solution Calculation of stability factor S =1+ h FE 100 = 7.65 = S = 1+ hFE R E 100 ×1K 1+ 1+ 1K + 18 K 12 K R E + R1 R2 Effect of ICBO Changes ∆T = 125oC – 25oC = 100oC or, the number of 10oC changes, in = 100oC / 10oC =10 From eq. (1.11), ICBO (2) = ICBO (1) x 2n = 15nA x 210 = 15.36µA ∆ICBO = ICBO (2) – ICBO (1) = 15.36µA - 15µA = 15.345µA = S x ∆ ICBO = 7.65 x 15.345µA from eq.(1.9) ∆IC = 117.39µA EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 11◄ Effect of VBE changes ∆VBE = ∆T x (1-8mV/oC) = 100oC x 1.8mV/oC = 180mV From eq (1-12), ∆IC = ∆VBE/RE = 180mV / 1K = 180µA Diode compensation The use of a diode to compensate for VBE changes is illustrated in Fig. 1-5 Vcc R1 Rc + Q1 + VBE VD1 - D1 RE R2 Fig 1-5 A diode can be used to compensate for VBE changes in a voltage divider bias circuit In this case, and, VB = VR2 + VD1 (1.13) IC ≈ IE = (VR2 + VD1 – VBE) / RE (1.14) When VBE changes by ∆VBE, the diode voltage changes by an approximately equal amount (∆VD1). ∆VBE and ∆VD1 tend to cancel each other, leaving IC largely constant at IC ≈ IE = VR2 / RE (1.15) EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 12◄ 1.7 CONSTANT CURRENT BIASING The fabrication of resistors and capacitors in integrated circuits is not economical. Thus, circuits are fabricated using the maximum number of transistors and the minimum number of resistors and capacitors. The biasing arrangements used in the integrated circuits use a constant current source (also called current mirror) to maintain Q-point stable. Fig 1-6(a) shows a simple realization of the current source and Fig 1-6(b) shows a simple realization of the current source, I. +VCC RC Q1 R2 IL 1k -VEE Fig. 1-6 (a) Constant current biasing (b) Simple realization of current source (current mirror) The current mirror is a dc network in which the current through the boad is the mirror image of another current of the same network. If the reference current of the network is changed, the current through the load will also change. A basic current mirror constructed using two back-to back npn transistors is shown in Fig. 1-6(b). the load current is the collector current of Q2, and the reference collector current of Q3. Note, in particular, that the collector of Q1 is connected directly to the base of the same transistor, establishing the same potential at each point. The result is that VC3 = VBE3 = VBE2 = 0.7V. The controlling element is resistor R. If you change its value, you can change the reference current EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 13◄ Once the resistance is set, the collector current of Q2 will immediately change to the new level. The operation of the mirror network is totally dependent on the fact that Q2 and Q3 are matched transistors, ie., transistors with very similar characteristics. Therefore, I REF = I L = (VCC − V EE − V BE ) R (1.16) We can connect this simulated current source in place of IL in Fig. 1-6(a) and get a stable Qpoint. Note that the current IL is independent of hFE and RB. This gives us liberty in choosing the value of RB. 1.8 PRE-LAB QUESTIONS 1) What is faithful amplification? What are the conditions to be fulfilled to achieve faithful amplification in a transistor amplifier? 2) What do you understand by transistor biasing? What is its need? 3) What do you understand by stabilization of Q-point? 4) Define Q-point and explain the concept of dc load line. 5) Analyze the voltage divider bias circuit in Fig. 1-7 to determine the transistor terminal voltages and currents (ie, VB, VC, VE, VBC, VCE, IC and IE). Draw the load line and plot the Q-point. Also determine whether the transistor is biased in cut-off, saturation, or the linear region. +VCC=18V R1 33K Rc 1.2K Q1 R2 12K RE 1K Fig 1-7 Voltage divider bias for problem 1-5 6) Design a voltage divider bias circuit using a BC107 transistor to have VCE = 4V, VE = 5V and IC = 1.3mA, the supply is VCC = 18V. (Note: Refer data sheet for hie and hfe values) EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 14◄ 7) Calculate the stability factor for the voltage divider bias circuit designed in problem 1-6. 8) Determine the Q-point change (ie., IC change & VCE change) produced in VD bias circuit designed in problem 1-6 when the circuit temperature in creased from 50oC to 150oC, and ICBO = 10nA at 50oC. 9) Determine the Q-point change produced in voltage divider bias circuit designed in problem 1-6 by the effect of VBE changes over a temperature range of 50oC to 150oC. 10) Calculate the mirrored current I in the circuit of Fig.1-8 Fig 1-8 Current mirror circuit for problem 1-10 1.9 EXPERIMENT (1) Voltage divider 1.1 Determine the values of R1, R2, RC and RE from the design problem 6 in the prelab question. 1.2 Assemble the circuit use BC107 transistor or equivalent. If the exact values of the components are not available, pickup the near by standard values. Measure hie and hFE of the transistor used. If the parameters of the transistor do not match the design specifications, recalculate the component values with these parameters. 1.3 Measure the Q-point. For measuring the Q-point, follow the procedure given below: Measure the voltage VC between the collector and the common terminal and then the voltage VE between emitter and common terminal. The difference (VC – VE) gives VCE. The collector current IC is given by (VCC-VC) / RC compare the measured values with the designed values. 1.4 Follow the same procedure the measure other transistor terminal currents and voltage. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 15◄ (2) Constant current biasing 2.1 From eq. (1-16) determine the value of R for the constant current biasing circuit as shown in Fig. 1-8 using the following data. RC = 2KΩ, RB = 220KΩ, VCC = 15V, VEE = 15V, VBE = 0.7V, IC = 5mA. Assume large hFE. Neglect ICBO. 2.2 Assemble the circuit use the BC107 transistors. If the exact values of the components are not available, pick up the nearby standard values. Measure hie and hFE of the transistor used. If the transistors do not match the design specifications, recalculate the component values with these parameters. Fig 1-8 Constant current biasing circuit 2.3 Measure the value of ICQ and VCEQ as per procedure given in step 1.3. Compare the measured value with the design parameter. Tabulate the readings. 1.10 POSTLAB QUESTIONS 1. In the implementation of voltage divider bias circuit change the value of R1 to R1/2 and then to 2R1 and measure the Q-point in each case. Comment on the changes in the Qpoint values. 2. In the implementation of constant current biasing circuit, increase the value of R by 1KΩ and measure the IC of Q1. Now, decrease the value of R by 1KΩ and measure the IC of Q1. Comment on the change in IC in each case. EC0222 Electronic Circuits Lab Manual Experiment 1.1: BJT biasing schemes ►1. 16◄ 3. The measurements appearing in Fig. 1-9 reveal that the network is not operating properly. Be specific in describing why the levels obtained reflect a problem with the expected network behavior. In other words, the level obtained reflect a very specific problem in each case. +VCC=16V +VCC=16V R1 91K Rc 3.6K 9.4V Beta=100 R1 91K Rc 3.6K Beta=100 2.64V 4V R2 18K RE 1.2K R2 18K RE 1.2K (a) (b) Fig 1-9 4. For the VDB circuit implemented in the experiment, answer the following questions. a. Does VC increase or decrease if R1 is increased? b. Does IC increase or decrease if β(hFE) is reduced? c. Does IC increase or decrease if VCC is reduced? d. What happens to VCE if the transistor is replaced one with larger β (hFE)? e. What happens to IC (sat) if β is increased? f. What happens to VCE if the ground leg of R2 opens? g. What happens to VCE if the transistor EB junction fails by becoming open? h. What happens to VCE if the transistor EB junction fails by becoming a short i. How will VE be affected when replacing the collector resistor with one whose resistance is at the lower end of the tolerance range? j. If the transistor collector junction becomes open, what will happen to VE? k. What might cause VCE to become nearly 18V? l. Analyze the circuit to investigate the effect of interchanging the voltage divider resistors. EC0222 Electronic Circuits Lab Manual