JW-10 TRANSISTOR BIASING Voltage divider (dc) biasing • There

advertisement

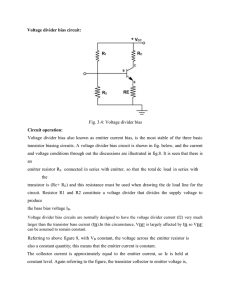

JW-10 TRANSISTOR BIASING Voltage divider (dc) biasing • There are many forms of dc biasing to give Q-point in mid-range → voltage divider (potentiometer) biasing is most common • The series base resistor is replaced by a voltage divider (R1 & R2) i.e. RB = R1 R2 / [R1 + R2] • Voltage divider R1 & R2 fixes VB VB = [R2 /(R1 + R2)] x VS VS → in this case VB = VBE = 0.7 V → hence transistor always forward biased • Hence IB is fixed by VB → so IC = β IB • dc output voltage VCE is determined by volts drop across RL • Design such that dc output voltage is about halfway between power rails i.e. Vo = VCE ≈ VS/2 RL R1 I I VR C B V CE I vi V R2 B (v o ) V BE • VS = VCE + ICRL 0V Design procedure • Design a potentiometer biased amplifier for the circuit shown above. • Assume the load resistor is 1 kΩ and the supply voltage is 10 V. • Design for an output voltage halfway between 0 V and Vs IC (mA) Collector current 10 mA LOAD LINE 50 µ A 40 µ A Q-point 30 µ A IB 25 µ A 20 µ A 5 mA 10 µ A 0 µA 0 5V 10 V V CE (V) Output voltage → Vo = VCEQ = Vs/2 = 10 V/2 = 5 V • The characteristic curve for this transistor shows that → a suitable quiescent base current is 25 µA → a suitable quiescent load current is 5 mA. • Now choose bias chain to provide base current of 25 µA • The current flowing through the bias chain divider (R1 & R2) is usually designed to be about ten times more than the base current I ≈ 10 IBQ = 10 X 25 µA = 250 µA • For transistor operation VB ≥ VBE = 0.7 V VB = [R2 /(R1 + R2)] x VS = 0.7 V • Also VB = I R2 • Thus R2 = VB/I = 0.7 V / 250 µA = 2.8 kΩ • Choose R2 to be the nearest lower standard value so that there is enough current available to base and bias chain i.e. R2 = 2.7 kΩ • Now calculate R1, using VB, R2 and Vs Thus R1 ≈ 39 kΩ Improvements to performance JW-10 • Complete voltage divider bias circuit includes capacitors & emitter resistor → FULLY STABILISED COMMON EMITTER (FSCE) CIRCUIT Input/output capacitors • Operating point set by no-signal (dc) conditions → ie when power supply applied → if i/p signal has an added dc component it can shift operating point → same can happen at output • Passing input/output signals through a capacitor blocks dc, passes ac • Capacitor reactance depends on signal frequency → XC = 1/(2πfC) [Ω] VS RL R1 Ci I I I vi V VR Co B V CE V BE R2 → At 1 Hz, XC = 16 kΩ for C = 10 µF C B RE CE → At 10 kHz, XC = 1.6 Ω for C = 10 µF VE v o ( V C Q) IE 0V → Capacitor passes 10 kHz signal but blocks the 1 Hz signal → since dc ≡ 0 Hz, XC tends to ∞ • Typical values lie between 10 µF – 100 µF Emitter resistor & thermal stability • Remember that (intrinsic) electrons and holes are generated by thermal effects → these increase with T ⇒ increase leakage current • In a biased transistor, BC junction always reverse biased → IC (hence IE) includes leakage components → If IC increases so does leakage & IE increases, thus operating point shifts → device heats up, leakage increases, IC increases, IE increases ⇒ and so on ⇒ THERMAL RUNAWAY ⇒ destroys transistor • A heat sink may prevent destruction but will not stop temp variations • An emitter resistor in the circuit fixes VE and thus IE I C → if IC rises due to leakage, so do IE and VE • But VBE = VB - VE Thus if VE rises VBE comes down ⇒ IB reduces, IC reduces & operating point maintained RE CE IE ⇒ this is NEGATIVE FEEDBACK • Emitter resistor only included to improve thermal stability under dc bias - don’t want it to influence ac performance • Need to decouple emitter resistor so that ac signal goes direct to ground while dc flows through RE → Add capacitor with low reactance to ac & high reactance to dc ⇒ CE ~ 100 µF at 1 kHz Decoupling Capacitor ⇒ for f = 50 Hz, XC = 32 Ω