ESE370: Circuit-Level for Digital Systems Modeling, Design, and Optimization

advertisement

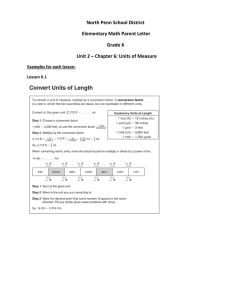

ESE370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 28: November 7, 2014 Memory Overview 1 Penn ESE370 Fall2014 -- DeHon Today • Memory – Motivation – Organization – Basic components – Optimization concerns • Project 2 is on this 2 Penn ESE370 Fall2014 -- DeHon Know how to store state 3 Penn ESE370 Fall2014 -- DeHon Register Storage • Could just put together a large number of registers • Concerns? 4 Penn ESE370 Fall2014 -- DeHon Concerns? • Large number of wires – Could determine area – 5l wire pitch how wide? • May want to store for many cycles 5 Penn ESE370 Fall2014 -- DeHon Usage Scenario • How many state values read on each cycle? 6 Penn ESE370 Fall2014 -- DeHon Concerns? • Large number of wires – Could determine area • May want to store for many cycles • Not able to update all on every cycle • Not able to use all on every cycle 7 Penn ESE370 Fall2014 -- DeHon Limited Data Use • What else do we need to share the wires if can only use one register on each cycle? – Use with shared data path • Need to select the one output – Can only update one • Need to control which one gets written 8 Penn ESE370 Fall2014 -- DeHon Limited Data Use • Add load enable to register • Logic to enable one register on write • Mux to select output Penn ESE370 Fall2014 -- DeHon we 9 Good Solution? • Could get away with just latch – Not full register with master/slave latch • Pay large amount for decode and mux – Proportional to memory bits Penn ESE370 Fall2014 -- DeHon we 10 Memory Idea • Maximize storage density (bits/cm2) • By minimizing the size/complexity of the repeated element • Use shared periphery circuits to provide full functionality • Trades off bandwidth (concurrent access) to save area 11 Penn ESE370 Fall2014 -- DeHon Memory Bank 12 Penn ESE370 Fall2014 -- DeHon Tristate Driver 13 Penn ESE370 Fall2014 -- DeHon Tri-State Drivers 14 Penn ESE370 Fall2014 -- DeHon Share Address Decode • Word – group of bits read/written together – All have same control (explored address decoder on midterm2) 15 Penn ESE370 Fall2014 -- DeHon Share Address Decode • Words • Mux select bits (words) from row read – When only want a subset 16 Penn ESE370 Fall2014 -- DeHon Share Address Decode • Result: only spend N0.5 area (perimeter) on selecting rather than linear in bits 17 Penn ESE370 Fall2014 -- DeHon Gate Density • When is 14n > 5n+32*sqrt(n) ? 18 Penn ESE370 Fall2014 -- DeHon Memory Row • Use shared enable for wire economy – Word line 19 Penn ESE370 Fall2014 -- DeHon Memory Column • Use shared bus for area and wire economy – Row enable selects the cells to read/write from bus 20 Penn ESE370 Fall2014 -- DeHon Memory Cell • Hold data • Conditionally drive onto output bus • Conditionally overwritten with data from bus 21 Penn ESE370 Fall2014 -- DeHon 5T SRAM Memory Bit 22 Penn ESE370 Fall2014 -- DeHon SRAM Memory bit • Core is back-to-back inverters for storage 23 Penn ESE370 Fall2014 -- DeHon SRAM Memory bit • Pass gate mux for output to column – Bit-Line (BL) 24 Penn ESE370 Fall2014 -- DeHon SRAM Memory bit • How do we write into this cell? – No directionality to pass gate – If drive BL strong enough, can flip value in selected cell • Ratioed operation 25 Penn ESE370 Fall2014 -- DeHon Column Capacitance • What is capacitance of bit line (column)? – Waccess– transistor width of column device – d rows g=Cdiff/Cgate 26 Penn ESE370 Fall2014 -- DeHon Time Driving Bit Line • In terms of Waccess, Wbuf, d • For Waccess=Wbuf=1, d=512, g=0.5 27 Penn ESE370 Fall2014 -- DeHon Column Capacitance Consequence • Want Waccess, Wbuf small to keep memory cell small • Increasing Waccess, also increases Cbl – Don’t really win by sizing up • Conclude: Driving bit line will be slow 28 Penn ESE370 Fall2014 -- DeHon Column Sensing • Speedup read time by sensing limited swing • Sense circuit detects small change in bit line voltage – Precharge to intermediate voltage • Amplifier for output 29 Penn ESE370 Fall2014 -- DeHon Output Amps • Bottom of array includes Sense Amplifiers from bit lines to output 30 Penn ESE370 Fall2014 -- DeHon Column Write • Writes driven from outside array • Use large driver – Strong enough to flip memory bit – Strong so can charge column quickly 31 Penn ESE370 Fall2014 -- DeHon Column Write • Writes driven from outside array • Use large driver – Strong enough to flip memory bit – Strong so can charge column quickly • Disable when not write – Be careful on your project2 – Could overwrite wrong row 32 Penn ESE370 Fall2014 -- DeHon Complete Memory Bank 33 Penn ESE370 Fall2014 -- DeHon Idea • Memory for compact state storage • Share circuitry across many bits – Minimize area per bit maximize density • Aggressively use: – Pass transistors, Ratioing – Precharge, Amplifiers to keep area down 34 Penn ESE370 Fall2014 -- DeHon Admin • HW7 due Tuesday • MT2 solutions posted 35 Penn ESE370 Fall2014 -- DeHon