ESE370: Circuit-Level for Digital Systems Modeling, Design, and Optimization

advertisement

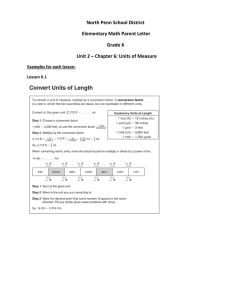

ESE370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 17: October 18, 2010 (Energy) Ratioed Logic 1 Penn ESE370 Fall2010 -- DeHon Today • Energy and Power – Data dependence – Switching vs. Leakage – Energy vs. Delay • Ratioed Gates – Correctness – Performance – Power – Implications Penn ESE370 Fall2010 -- DeHon 2 Data Dependent Activity • Consider an 8b counter – What is activity, a, for: • Low bit? • High bit? • Assuming random inputs (no glitching) – Activity at output of nand4? – Activity at output of xor4? 3 Penn ESE370 Fall2010 -- DeHon Total Power • Ptot = Pstatic + Psc + Pdyn • Pdyn + Psc = a(½Cload+Csc)V2f • Ptot ≈ a(½Cload+Csc)V2f+VI’s(W/L)e-Vt/(nkT/q) IDS W IS e L Penn ESE370 Fall2010 -- DeHon VGS VT nkT / q VDS kT / q 1 e 1 VDS 4 Slow Down • Ptot ≈ a(½Cload+Csc)V2f+VI’s(W/L)e-Vt/(nkT/q) • What happens to power contributions as reduce clock frequency? • What suggest about Vt? 5 Penn ESE370 Fall2010 -- DeHon ITRS 2009 Year of Production MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (contacted) Lg: Physical Lgate for High Performance logic (nm) [1] 2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023 2024 54 45 38 32 27 24 21 18.9 16.9 15 13.4 11.9 10.6 9.5 8.4 7.5 29 27 24 22 20 18 17 15.3 14 12.8 11.7 10.7 9.7 8.9 8.1 7.4 1 0.95 0.88 0.75 0.65 0.55 0.53 0.7 0.68 EOT: Equivalent Oxide Thickness (nm) [2] Extended planar bulk UTB FD MG 0.6 0.57 0.57 0.54 0.5 0.77 0.7 0.67 0.64 0.62 0.59 0.57 0.55 0.53 0.5 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 5 4.8 4.5 4.3 4.2 0.99 0.97 0.95 0.93 0.9 0.37 0.35 0.32 0.3 0.28 Channel doping (E18 /cm3) [3] Extended Planar Bulk 3.7 4 4.5 5 5.7 6.6 7.5 13 12 10.5 9.5 8.7 8 7.3 7 6 5.5 5.1 4.7 4.3 3.9 8 7.6 7 6.4 5.8 1 0.97 0.97 0.94 0.9 1.17 1.1 1.07 1.04 1.02 Junction depth or body Thickness (nm) [4] Extended Planar Bulk (junction) UTB FD (body) MG (body) EOTelec: Electrical Equivalent Oxide Thickness (nm) [5] Extended Planar Bulk 1.32 1.26 1.2 1.06 UTB FD 0.95 0.85 1.1 1.08 MG 0.82 Cg ideal (fF/m m) [6] Extended Planar Bulk 0.76 0.73 0.67 0.72 UTB FD 0.73 0.75 0.71 0.63 0.58 0.59 0.54 0.5 0.47 0.45 0.5 0.48 0.45 0.42 0.39 1.9 MG Jg,limit: Maximum gate leakage current density (kA/cm 2) [7] Extended Planar Bulk 0.65 0.83 0.9 1 UTB FD 1.1 1.2 1.3 1.1 1.2 1.3 1.4 1.5 1.7 1.3 1.4 1.5 1.7 1.9 2.1 2.2 2.5 2.7 2.9 0.78 0.76 0.73 0.71 0.68 0.66 0.64 0.62 0.6 MG Vdd: Power Supply Voltage (V) [8] P bulk/UTB FD/MG 1 0.97 0.93 0.9 0.87 0.84 0.81 285 289 294 291 295 309 302 221 221 220 228 232 236 235 206 202 207 207 209 219 213 219 228 231 Vt,sat: Saturation Threshold Voltage (mV) [9] Extended Planar Bulk UTB FD MG Isd,leak (nA/m m) [10] Bulk/UTB FD/MG 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1 1 1 1 1.06 1.12 1.19 1.26 1.34 1.42 1.5 1.59 1.69 1.79 1.9 2.01 170 170 160 140 130 110 110 140 140 130 120 120 120 110 140 140 130 130 120 120 120 120 110 110 1,870 2,000 2,060 2,110 2,170 1.53 1.72 1.92 2.09 2.32 0.18 0.18 0.18 0.18 0.18 0.55 0.53 0.5 6 0.46 Mobility enhancement factor due to strain [11] Bulk/UTB FD/MG Effective Ballistic Enhancement Factor, Kbal [12] Bulk/UTB FD/MG Rsd: Effective Parasitic series source/drain resistance (Ω-µm) [13] Extended Planar Bulk UTB FD MG Id,sat: NMOS Drive Current (µA/µm) [14] Extended Planar Bulk 1,210 1,200 1,190 1,300 UTB FD 1,450 1,580 1,680 1,470 1,520 1,670 1,730 1,770 1,830 1,970 1,490 1,630 1,710 1,790 1,860 1 1.08 1.19 1.3 1.41 1.01 1.11 1.21 1.32 1.43 MG Equivalent injection velocity, vinj (107 cm/s) [15] Extended Planar Bulk 0.76 0.77 0.77 0.78 UTB FD 0.84 0.9 0.86 0.93 MG 0.98 Cg fringing capacitance (fF/m m) [16] Extended Planar Bulk 0.24 0.25 0.26 0.24 UTB FD 0.23 0.23 0.25 0.17 0.17 0.17 0.17 0.17 0.17 0.17 0.19 0.18 0.18 0.18 0.18 MG Cg,total: Total gate capacitance for calculation of CV/I (fF/µm) [17] Extended Planar Bulk UTB FD MG Penn ESE370 Fall2010 -- DeHon 1 0.97 0.93 0.95 0.96 0.96 0.94 0.8 0.75 0.76 0.71 0.67 0.64 0.62 0.68 0.66 0.63 0.61 0.58 0.48 ITRS 2009 45nm Low Power Isd,leak Isd,sat High Performance 100nA/mm 1200 mA/mm Cg,total Vth 1fF/mm 285mV 0.91fF/mm 585mV 50pA/mm 560mA/mm C0 = 0.045mm × Cg,total 7 Penn ESE370 Fall2010 -- DeHon High Power • V=1V • Csc = 0 – (just for simplicity, typically <Cload) • Cload=22C0 ≈ 1 fF = 10-15F • WN = 2 Ileak = 9×10-9 A • P=a(0.5×10-15) freq + 9×10-9 W 8 Penn ESE370 Fall2010 -- DeHon Compare • • • • P=a(0.5×10-15) freq + 9×10-9 W a=0.2 P=10-16×freq + 9×10-9 W For what freqs does leakage power dominate switching power? 9 Penn ESE370 Fall2010 -- DeHon ITRS 2009 45nm Low Power Isd,leak Isd,sat High Performance 100nA/mm 1200 mA/mm Cg,total Vth 1fF/mm 285mV 0.91fF/mm 585mV 50pA/mm 560mA/mm C0 = 0.045mm × Cg,total 10 Penn ESE370 Fall2010 -- DeHon Reduce V • What happens as reduce V? – Delay? – Energy? • Static • Switching • Ptot ≈ a(½Cload+Csc)V2f+VI’s(W/L)e-Vt/(nkT/q) 11 Penn ESE370 Fall2010 -- DeHon Reduce V (no physical scale) tgd=Q/I=(CV)/I V S×V Id=(mCOX/2)(W/L)(Vgs-VTH)2 Id S2×Id tgd tgd /S 12 Penn ESE370 Fall 2010 -- DeHon Observe • Ignoring leakage Et Const 2 E V 2 t V 1 13 Penn ESE370 Fall2010 -- DeHon Energy vs. Power? • What do we care about? – Battery operated devices? – Desktops? 14 Penn ESE370 Fall2010 -- DeHon Ratioed Logic 15 Penn ESE370 Fall2010 -- DeHon Note on what about to see • Not clear win • Should be able to analyze – Chance to exercise analysis – Kind of thing you want to be able to analyze • Pattern should recognize • May be a stepping stone to something interesting to come… 16 Penn ESE370 Fall2010 -- DeHon Idea • Building both pull-up and pull-down can be expensive – many gates • Seems wasteful to build logic function twice – Once in pullup, once in pulldown – Large capacitance 17 Penn ESE370 Fall2010 -- DeHon Idea • Maybe only need to build one • Build NFET pulldown – Exploit high N mobility 18 Penn ESE370 Fall2010 -- DeHon Ratioed Inverter • Does this work? WP=1 WN= 1 19 Penn ESE370 Fall2010 -- DeHon Ratioed Inverter • How do we need to size N to make it work? WP=1 20 Penn ESE370 Fall2010 -- DeHon DC Transfer Function 21 Penn ESE370 Fall2010 -- DeHon Worst-Case Output Drive? WP=1 22 Penn ESE370 Fall2010 -- DeHon Noise Margin Tradeoff • Impact of increasing (reducing) noise margin? 23 Penn ESE370 Fall2010 -- DeHon Class stopped here 24 Penn ESE370 Fall2010 -- DeHon Size for R0/2 drive? 25 Penn ESE370 Fall2010 -- DeHon Compare Static CMOS • Total Transistor Width • Input capacitance load 26 Penn ESE370 Fall2010 -- DeHon Power? • Istatic ? • Output high? – Ileak • Output low? – Ipmos_on – Vdd/(R0/2) -- for our sample case 27 Penn ESE370 Fall2010 -- DeHon Power • Ptot ≈ a(½Cload+Csc)V2f +PlowV2/Rpon +(1-Plow)VI’s(W/L)e-Vt/(nkT/q) 28 Penn ESE370 Fall2010 -- DeHon How size for R0/2 drive? 29 Penn ESE370 Fall2010 -- DeHon How size for R0/2 drive? 30 Penn ESE370 Fall2010 -- DeHon Which Implementation is faster in ratioed logic? 31 Penn ESE370 Fall2010 -- DeHon Illustrates • Preferred gate changes 32 Penn ESE370 Fall2010 -- DeHon How size for R0/2 drive? • K-input nor 33 Penn ESE370 Fall2010 -- DeHon When better than CMOS nor-k? • Better = smaller, lower input capacitance 34 Penn ESE370 Fall2010 -- DeHon Admin • Project – Hope you got a chance to try out many things this weekend – Due Friday • Andre office hours Tuesday 4:30pm 35 Penn ESE370 Fall2010 -- DeHon Ideas • • • • Energy-Delay tradeoff: Et2 There are other logic disciplines We have the tools to analyze Ratioed Logic – Tradeoff noise margin for • Reduced area? Capacitive load? – Dissipates static power in one mode 36 Penn ESE370 Fall2010 -- DeHon