ESE370: Circuit-Level for Digital Systems Modeling, Design, and Optimization

advertisement

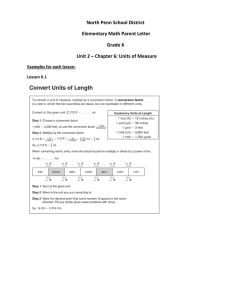

ESE370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 5: September 17, 2010 Restoration 1 Penn ESE370 Fall2010 -- DeHon Today • How do we make sure logic is robust – Can assemble into any (feed forward) graph – Can tolerate loss and noise – ….while maintaining digital abstraction 2 Penn ESE370 Fall2010 -- DeHon Outline • • • • • • Two problems Cascade failure Restoration Transfer Curves Noise Margins Non-linear 3 Penn ESE370 Fall2010 -- DeHon Wire Crossings and Shorts Wires connected/shorted Wires not connected 4 Penn ESE370 Fall2010 -- DeHon Two Problems 1. Output not go to rail 2. Signals may be perturbed by noise 5 Penn ESE370 Fall2010 -- DeHon Output not go to Rail • CMOS, capacitive load – Mostly doesn’t have problem • CMOS, resistive load? – Igd≠0 ? – How close to rail do I need to get? 6 Penn ESE370 Fall2010 -- DeHon Wire Resistance 7 Penn ESE370 Fall2010 -- DeHon Wire Resistance R Penn ESE370 Fall2010 -- DeHon L A 8 Wire Resistance • Sanity check – Wire twice as long = resistors in series – Wire twice as wide = resistors in parallel R Penn ESE370 Fall2010 -- DeHon L A 9 Wire Resistance • 1000 mm long wire? • 1 cm long wire? • Length of die side? 10 Penn ESE370 Fall2010 -- DeHon Die Sizes Processor Die Size Transistor Count Process Core 2 Extreme X6800 143 mm² 291 Mio. 65 nm Core 2 Duo E6700 143 mm² 291 Mio. 65 nm Core 2 Duo E6600 143 mm² 291 Mio. 65 nm Core 2 Duo E6400 111 mm² 167 Mio. 65 nm Core 2 Duo E6300 111 mm² 167 Mio. 65 nm Pentium D 900 280 mm² 376 Mio. 65 nm Athlon 64 FX-62 230 mm² 227 Mio. 90 nm Athlon 64 5000+ 183 mm² 154 Mio. 90 nm http://www.tomshardware.com/reviews/core2-duo-knocks-athlon-64,1282-4.html 11 Penn ESE370 Fall2010 -- DeHon Implications • What does the circuit really look like for an inverter in the middle of the chip? 12 Penn ESE370 Fall2010 -- DeHon Implications • What does the circuit really look like for an inverter in the middle of the chip? 13 Penn ESE370 Fall2010 -- DeHon IR-Drop • Since interconnect is resistive and gates pull current off the supply interconnect – The Vdd seen by a gate is lower than the supply Voltage by • Vdrop=Isupply x Rdistribute – Two gates in different locations • See different Rdistribute • Therefore, see different Vdrop 14 Penn ESE370 Fall2010 -- DeHon Output not go to Rail • CMOS, capacitive load – Mostly doesn’t have problem • CMOS, resistive load • Due to IR drop, “rails” for two communicating gates may not match 15 Penn ESE370 Fall2010 -- DeHon Two Problems 1. Output not go to rail – Is this tolerable? 2. Signals may be perturbed by noise – Voltage seen at input to a gate may not lower/higher than input voltage 16 Penn ESE370 Fall2010 -- DeHon Noise Sources? • What did we see in lab when zoomed in on signal transition? • Signal coupling – Crosstalk • Leakage • Ionizing particles • IR-drop in signal wiring 17 Penn ESE370 Fall2010 -- DeHon Two Problems 1. Output not go to rail – Is this tolerable? 2. Signals may be perturbed by noise – Voltage seen at input to a gate may not lower/higher than input voltage • What happens to degraded signals? 18 Penn ESE370 Fall2010 -- DeHon Preclass • All 1’s logical output? 19 Penn ESE370 Fall2010 -- DeHon Preclass • 1.0 inputs, gate: o=1-AB output voltage? 20 Penn ESE370 Fall2010 -- DeHon Preclass • 0.95 inputs, gate: o=1-AB output voltage? 21 Penn ESE370 Fall2010 -- DeHon Degradation • Cannot have signal degrade across gates • Want to be able to cascade arbitrary set of gates 22 Penn ESE370 Fall2010 -- DeHon Gate Creed • Gates should leave the signal “better” than they found it – “better” closer to the rails 23 Penn ESE370 Fall2010 -- DeHon Restoration Discipline • Define legal inputs – Gate works if Vin “close enough” to the rail • Restoration – Gate produces Vout “closer to rail” • Tolerates some drop between out and in • Call this our “Noise Margin” 24 Penn ESE370 Fall2010 -- DeHon Noise Margin • Voh – output high • Vol – output low • Vih – input high • Vil – input low • NMh = Voh-Vih • NMl = Vol-Vil Penn ESE370 Fall2010 -- DeHon One mechanism, addresses numerous noise sources. 25 Restoration Discipline • Define legal inputs – Gate works if Vin “close enough” to the rail – Vin > Vih or Vin < Vil • Restoration – Gate produces Vout “closer to rail” • Vout < Vol or Vout > Voh 26 Penn ESE370 Fall2010 -- DeHon Restoring Transfer Function 27 Penn ESE370 Fall2010 -- DeHon Restoring Transfer Function For multi-input functions, hold non-controlling inputs at Vil, Vih respectively. (relate preclass exercise) 28 Penn ESE370 Fall2010 -- DeHon Ideal Transfer Function 29 Penn ESE370 Fall2010 -- DeHon Linear Transfer Function? • O=Vdd-A Noise Margin? 30 Penn ESE370 Fall2010 -- DeHon Non-linearity • Need non-linearity in transfer function • Could not have built restoring gates with – R, L, C circuit – Linear elements 31 Penn ESE370 Fall2010 -- DeHon Transistor Non-Linearity 32 Penn ESE370 Fall2010 -- DeHon All Gates • If hope to assemble design from collection of gates, – Voltage levels must be consistent and supported across all gates Vol MAX g.Vol Vil MIN g.Vil Voh MIN g.Voh Vih MAX g.Vih gG gG Penn ESE370 Fall2010 -- DeHon gG gG 33 Admin • HW2 is out • Monday in Ketterer – Lab combo • Wednesday back here 34 Penn ESE370 Fall2010 -- DeHon Big Idea • Need robust logic – Can assemble into any (feed forward) graph – Can tolerate loss and noise – ….while maintaining digital abstraction • Restoration and noise margins – Every gate makes signal “better” – Design level of noise tolerance 35 Penn ESE370 Fall2010 -- DeHon