1 P h

advertisement

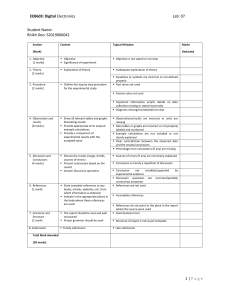

Philadelphia University Coordinator:Dr. Hasan Al-Refai Internal Examiner: Prof. Dr. Mohammed Mahafzah 750231: Computer Logic Design Second Exam Faculty of Information Technology Department of Computer Science Examination Paper Academic Year 2014/2015 Time: 50 Minutes First Semester 5th May, 2015 Information for Candidates 1.This examination paper contains 5questions, totalling 20marks. 2.The marks for parts of questions are shown in round brackets. Advice to Candidates 1. You should attempt all questions. 2. You should write your answers clearly. I. Basic Notions Objectives: The aim of the questions in this part is to evaluate the required minimal student knowledge and skills. Answers in the pass category represent the minimum acceptable standard. Question 1: (3 Marks, 1 Mark Each) Select the correct answer for the following multiple choice questions: 1) A device which converts Hexadecimal numbers to Binary numbers is called a) b) c) d) Encoder Decoder Multiplexer Demultiplexer 2) The BCD representation of the decimal number (26) is a) 00100110 b) 01011001 c) 10001001 d) 01001101 3) How many “Enable” inputs should be used to connect 8 decoders in order to build a larger decoder? a) 2 b) 5 c) 3 d) 6 II. Familiar Problems Solving Objectives: The aim of the questions in this part is to evaluate that the student has some basic knowledge ofthe key aspects of the lecture material and can attempt to solve familiar problems Question 2: (3 marks) Obtain the canonical product of the sum form of the following function . F (A, B, C) = (A + B′) (B + C) (A + C′) Question 3: (5marks) Given the following function F (w, x, y, z) = ∑ (3, 6, 7, 9, 11, 12, 13, 14, 15) 1) Simplify the expression into sum of products using Karnaugh map. 2) If found that the function has don’t care conditions where d=∑ m (8, 10), simplify the expression into product of sums using the proper don’t-care conditions. Question 4: (3 marks) 1 A combinational circuit is defined by the following Boolean function: F1 (A, B) = A' B +A B + A B' 1) Design the circuit with a decoder and external gates. (Note: you are not allowed to use decoder block) Question 5: (3 marks) Design a 32x1 multiplexer using two 16x1 multiplexers and one 2x1 multiplexer. (Use blocks diagrams). III. Unfamiliar Problems Solving Objectives: The aim of the questions in this part is to evaluate that the student can solve familiar problems with ease and can make progress towards the solution of unfamiliar problems, and can set out reasoning and explanation in a clear and coherent manner. Question 5 :( 3marks) Design a (4-bit) full Subtractor using full adders and additional gates. Good Luck 2