FAULT DIAGNOSIS AND COMPARATOR REDESIGN FOR AN 8-BIT 20-MS/S

advertisement

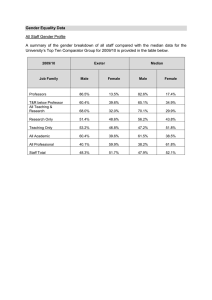

FAULT DIAGNOSIS AND COMPARATOR REDESIGN FOR AN 8-BIT 20-MS/S CALIBRATED PIPELINED ANALOG-TO-DIGITAL CONVERTER IN 0.5-µm CMOS Nicholas Thomas Martin B.S., California State University, Sacramento, 2008 PROJECT Submitted in partial satisfaction of the requirements for the degree of MASTER OF SCIENCE in ELECTRICAL AND ELECTRONIC ENGINEERING at CALIFORNIA STATE UNIVERSITY, SACRAMENTO SUMMER 2011 FAULT DIAGNOSIS AND COMPARATOR REDESIGN FOR AN 8-BIT 20-MS/S CALIBRATED PIPELINED ANALOG-TO-DIGITAL CONVERTER IN 0.5-µm CMOS A Project by Nicholas Thomas Martin Approved by: __________________________________, Committee Chair Perry Heedley, Ph.D. __________________________________, Second Reader Thomas Matthews, Ph.D. ____________________________ Date ii Student: Nicholas Thomas Martin I certify that this student has met the requirements for format contained in the University format manual, and that this project is suitable for shelving in the Library and credit is to be awarded for the Project. __________________________, Graduate Coordinator Preetham Kumar, Ph.D. Department of Electrical and Electronics Engineering iii ________________ Date Abstract of FAULT DIAGNOSIS AND COMPARATOR REDESIGN FOR AN 8-BIT 20-MS/S CALIBRATED PIPELINED ANALOG-TO-DIGITAL CONVERTER IN 0.5-µm CMOS by Nicholas Thomas Martin This project is a fault diagnosis and redesign effort for an 8-bit 20-MS/s pipelined analogto-digital converter designed and fabricated in a 0.5µm CMOS process technology. This integrated circuit was designed using a 1.5 bit/stage pipelined architecture and uses seven stages, which forms the most critical part of the chip referred to as the ‘pipeline core’. From the information received from the advisors of the previous team, the comparator included an adjustable reset time design-for-test (DFT) feature, but test results indicated minimal adjust range of the reset time.My part of this project was focused on the diagnosis and redesign of the comparator located within the Sub-ADC of the pipeline core. _______________________, Committee Chair Perry Heedley, Ph.D. _______________________ Date iv ACKNOWLEDGMENTS First and foremost I would like to thank my advisors, Drs Perry Heedley and Thomas Matthews, for establishing the mixed signal design lab (MSDL) at CSUS and providing me with an opportunity to design an integrated circuit. Successful completion of this project is a direct result of the endless hours you spent providing me with professional guidance and support. Your passion for the field of analog and mixed-signal design has inspired me to maintain my pursuit of higher education and I welcome any future cooperative project opportunities to continue to learn from you. In addition, I would like to thank Tom Palomino for his significant contribution to the layout of this project and advising me on the intricacies in the art of analog layout. I would also like to acknowledge my employer, Defense Microelectronics Activity (DMEA), for providing me with the resources and time away from work that were instrumental in the timely completion of this degree. Last but not least, I would like to thank my fiancé Cheyanne Cook, and family for their continued love, support, and encouragement throughout every phase of this master’s degree. v TABLE OF CONTENTS Page Acknowledgements ..............................................................................................................v List of Tables .................................................................................................................... vii List of Figures .................................................................................................................. viii Chapter 1. INTRODUCTION ...........................................................................................................1 1.1 Analog-to-Digital Converters ....................................................................................1 1.2 Project Overview .......................................................................................................2 1.3 Pipelined Analog-to-Digital Converters ....................................................................4 1.4 Pipelined ADC Architecture ......................................................................................5 1.5 Dynamic Comparator.................................................................................................8 2. THE RESIDUE STAGE ................................................................................................10 2.1 The 1.5-Bit Stage ....................................................................................................10 2.2 The Sub-ADC and Sub-DAC .................................................................................11 2.3 Comparator Theory of Operation ...........................................................................14 3. FAULT DIAGNOSIS AND REDESIGN OF THE COMPARATOR ..........................18 3.1 Fault Diagnosis of the Original Comparator ...........................................................18 3.1.1 Simulation Results ............................................................................................20 3.1.2 Effects on Comparator Performance .................................................................23 3.2 Redesign of the Comparator ....................................................................................26 3.2.1 Detailed Explanation of the Redesigned Comparator.......................................26 3.2.2 Simulation Results for the Redesigned Comparator .........................................29 4. LAYOUT .......................................................................................................................35 4.1 Original Comparator Layout....................................................................................35 4.2 Redesigned Comparator Layout ..............................................................................36 5. CONCLUSIONS............................................................................................................41 References ..........................................................................................................................42 vi LIST OF TABLES Page Table 1.1 Ideal 1.5-Bit per Stage Transfer Functions ....................................................... 11 Table 2.1 Truth Table and Functional Description of the Sub-ADC and Sub-DAC ........ 14 Table 3.1 Comparator Design Specifications ................................................................... 23 Table 3.2 Input Referred Comparator Offset Voltage vs. DAC current ........................... 24 Table 3.3 Original vs. Redesigned DAC Current Range .................................................. 27 Table 3.4 Original and Redesigned Comparator Decision Times .................................... 32 vii LIST OF FIGURES Page Figure 1.1 Diagram of the analog-to-digital conversion process ........................................ 2 Figure 1.2 Pipelined-ADC 1.5-bit/stage architecture ......................................................... 6 Figure 2.1 The 1.5-Bit per Stage Block Diagram ............................................................. 10 Figure 2.2 The Sub-ADC and Sub-DAC .......................................................................... 12 Figure 2.3 Latching Comparator with Preamplifier .......................................................... 15 Figure 3.1 Schematic for the Original Comparator .......................................................... 18 Figure 3.2 SMC used in the Original Comparator ............................................................ 19 Figure 3.3 Vreset Range for the Original Comparator ..................................................... 22 Figure 3.4 Redesigned Comparator SMC ......................................................................... 28 Figure 3.5 Schematic for the Redesigned Comparator ..................................................... 30 Figure 3.6 Vreset Range for the Redesigned Comparator ................................................ 31 Figure 3.7 Overdrive Recovery Test for the Redesigned Comparator ............................. 33 Figure 3.8 Decision Time for the Redesigned Comparator at the SS PVT Corner .......... 34 Figure 4.1 Layout for the Original Comparator ................................................................ 35 Figure 4.2 Layout for the Redesigned Comparator .......................................................... 36 Figure 4.3 Layout for the Current Mirrors and Preamplifier ............................................ 38 Figure 4.4 Layout for the Reset Switch ............................................................................ 39 Figure 4.5 Layout for the SMC ......................................................................................... 40 viii 1 Chapter 1 INTRODUCTION 1.1 Analog-to-Digital Converters The role of a data converter within the realm of electronics is synonymous to that of a translator within the realm of communications. When a language barrier exists between two people, a translator - which is fluent in both languages - can bridge the gap by inserting himself or herself into the flow of communication by acting as a translation conduit. The translator accomplishes this task by committing to memory a segment of dialogue received from one of the individuals, followed by a verbal translation to the second individual. Data converters provide a similar function, but unlike the translator, which bridges a language barrier gap, converters deal with a technology interface gap. A fundamental boundary exists between the continuous nature of the physical world and the discrete nature of the digitized computer world. Analog signals provide a continuous representation of a signal in terms of amplitude and time, while the discrete nature of digital signals is limited to quantized values for both. As in all aspects of engineering a tradeoff exits between the processing and data manipulation of these two types of signals. Analog signals have the advantage of theoretically providing infinite resolution, although from a practical standpoint this has not proven to be the case. Once implemented into a circuit, analog signals are susceptible to degradation in the presence of noise, prove difficult to perform complex arithmetic functions on, and often consume far more power and area than their digital counterparts. Digital signals benefit from the scaling of 2 complementary metal-oxide semiconductor (CMOS) processes, to extremely small sizes, with the associated advantages of being faster, denser, lower power circuits that can perform complex arithmetic functions. Unfortunately, digital processors performing complex operations require signals to be in a discrete and quantized form, typically binary, which is in contrast to the analog nature of light, sound and other measureable quantities of the physical world. Data converters facilitate the necessary conversion between domains, analog to digital, and bridge the gap between the continuous physical world and digitized computer world. Figure 1.1 illustrates this conversion process. A key component in analog-to-digital converters (ADCs) is a comparator, which is the focus of this project. Figure 1.1 Diagram of the analog-to-digital conversion process [1] 1.2 Project Overview Projects assigned to students within the Mixed-Signal Design Laboratory (MSDL) at California State University, Sacramento (CSUS), adhere to a design methodology created by industry experts, which is a multi phase process consisting of reviews by peers and advisors at major milestones during the lifecycle of the project [2]. The intent of taking 3 this approach is to emphasize the importance of identifying critical issues early, as well as the value of sharing knowledge in a peer review setting, all in support of creating silicon integrated circuits with minimum errors to ensure a first pass success. One of the major benefits of having the MSDL at CSUS is that the complexity of future projects can evolve by leveraging off work performed on past projects by former students. The development of a new proof-of-concept for an invention, such as a calibration technique for a data converter, can be a lengthy endeavor if the project entails the design of both the data converter and the calibration technique. If the focus of the project is to examine the ability of a calibration technique to mitigate a performance constraint, then an easy solution to reduce the aforementioned time burden is to use a previous project as a foundation to leverage off, thus eliminating the need to repeat the design of the original project (in this case, a data converter). One of the constraints limiting the migration of pipelined analog-to-digital data converters (ADCs) to deep-submicron technology is the poor analog characteristics of the transistors available in these processes [3] [4]. A calibration method to correct some of these analog imperfections, developed and verified in a MATLAB behavioral model by a group of CSUS students, is being implemented in a prototype chip based on an existing pipelined ADC previously created by graduate students working in the MSDL at CSUS [5] [6]. 4 Prior to applying the new calibration technique to the pipelined ADC, it was determined that a few modifications had to be made to the operational amplifier and comparator. The operational amplifier required a unique modification, the addition of a gain reduction switch, to allow the effectiveness of the calibration method to be determined over a range of gain errors. Another requirement was to perform a fault analysis and redesign of the comparator used in the original design [9], based on data obtained during the development of the dynamic offset test bench (DOTB) [7]. While testing the existing pipelined ADC’s comparator with the DOTB, a surprising discovery was encountered in the test results. One of the comparator’s design-for-test (DFT) features which was intended to provide scalability of the reset time had minimal impact on the results, thus indicating improper biasing of the circuits used to implement this DFT feature. This report presents the fault diagnosis and redesign of the dynamic comparator that is part of an 8-bit 20MS/s calibrated pipelined analog-to-digital converter (ADC) implemented in a 0.5µm CMOS process. 1.3 Pipelined Analog-to-Digital Converters Pipelined ADCs are ubiquitous within communication and video-processing systems, primarily because they provide a solution to systems requiring a data converter that is low power, medium resolution, and has a high-speed data throughput. As processes have scaled into the deep submicron regime, all the attractive attributes of pipelined ADCs have continued to benefit from scaling, despite the poor analog performance at these 5 smaller geometries. In order to maintain this continuation of performance improvement as processes shrink to nanometer dimensions, the focus of circuit designers has transitioned from improving the performance of the core pipeline circuits, to designing calibration techniques that compensate for the poor analog performance of the transistors. Such calibration techniques for pipelined ADCs are presently of great interest to CMOS circuit designers. 1.4 Pipelined ADC Architecture A commonly used pipelined ADC configuration is the 1.5-bit/stage architecture [11], which is the basis for this project. A block diagram of this architecture is shown in Figure 1.2. The ADC comprises seven stages, with the first through six stages being identical, and stage seven being a modified version of the previous stages. One of the many options a designer encounters when designing a pipelined ADC is whether to use identical stages, as in this project, or to tailor each stage to a unique set of specifications. The use of identical stages has the advantage of cutting down design time, which is accomplish by designing the first stage and then reusing it for the remaining stages. This technique is acceptable considering that the first stage must be the most accurate, given that any error or distortion created within it will propagate through the remaining stages, thus reducing their ability to resolve an accurate value. The drawback to this technique is twofold. Higher accuracy translates to bigger circuits that use more silicon area, and bigger circuits also lead to an increase in power consumption. Since device mismatches increase as transistor sizes shrink [8], the use of small devices causes a loss in accuracy. A 6 common way to reduce these errors is to average them out by increasing device size, which typically leads to a large first stage. Keeping this same size for all the stages in the pipeline increases area and power consumption. Figure 1.2 Pipelined-ADC 1.5-bit/stage architecture [9] [11] If the increase in area and/or power consumption is not tolerable, stage scaling is an alternative option [10] [14]. Stage scaling is exactly as the name implies for an N-bit pipelined ADC. Design the first stage to be N-bit accurate and relax the accuracy requirement of each subsequent stage by one bit. This technique is acceptable because the LSB size is scaled up by 2x as it propagates through each stage. The drawback to this approach is the added design time. Each of the seven stages has a unique set of requirements, compared to the aforementioned technique of employing identical stages. 7 The pipelined ADC used in this project utilizes identical stages, which is acceptable given that power constraints are not a limiting factor for this project. Data conversion within a pipelined ADC is an iterative process that begins with the front end sample and hold amplifier (SHA) sampling the analog input signal and holding that value while the first stage performs a conversion. In a 1.5-bit/stage pipeline architecture each stage determines only one bit, although a second bit is also generated by the subADC for error correction. These bits are then fed to two different locations, out of the stage to a series of shift registers for use by the error correction circuit, and to the sub-DAC to be converted back into an analog value. The summer subtracts the analog value of the bits provided by the sub-DAC from its input to create the residue signal, followed by amplification by two, which expands the residue signal back to the full-scale signal range of the pipeline. Each subsequent stage performs the same conversion process on the residue signal from the previous stage as it propagates through the pipeline. When the final stage converts the residue signal from the next to the last stage in the pipeline the conversion process is complete, so this stage need not create a residue signal. The redundancy provided by each stage is a result of the three allowable ranges that can be resolved by the two comparators within the sub-ADC in the 1.5-bit/stage architecture. Each of the first six stages contributes one bit of information, with the final stage contributing two bits to the final ADC output code. Utilizing redundancy does have the drawback of added circuitry, but provides the advantage of a relaxed input offset 8 requirement for the comparators and the ability to correct over range conditions within the digital error correction range [6] [11]. The digital error correction circuit combines the fourteen time-aligned bits received from the shift registers to create the final 8-bit binary output code for the ADC. The inherent latency of a pipelined ADC is a result of the serial fashion in which the bits are determined, one by each stage, with the residue passed along to the next stage to continue the process. This latency is tolerable when applied to many applications, such as communication and video processing, which benefit from the high throughput nature of this architecture. 1.5 Dynamic Comparator Pipelined ADC comparators are the interface between the analog nature of the physical world and the discrete nature of the digital world. These low-resolution converters are what quantizes the analog signal into a binary representations. The resolution of a pipelined ADC is dependent upon the performance of the comparators in the sub-ADC. The error correction provided by the 1.5-bit/stage architecture relaxes the need for the comparators to have a low offset voltage [11]. Timing requirements, however, make the speed of the comparators of primary importance. For many applications, an emphasis is also placed on reducing the power consumption of the converter. 9 In order to achieve the aforementioned characteristics, dynamic comparators are typically used in pipelined ADCs. These comparators can use smaller device sizes for increased speed and reduced area and power consumption. The smaller devices also lead to increased offset. To counteract the large offsets, while still benefiting from the advantages of the smaller devices, the previously mentioned redundancy technique is used to relax comparator offset requirements. Purely dynamic comparators only dissipate power during transient conditions when they latch. However, comparators often include a pre-amplifier stage, which reduces kickback noise and provides a further reduction in offset, at the cost of a static current draw. This slight increase in power consumption and area is often deemed to be an acceptable tradeoff between performance and area and power consumption. 10 Chapter 2 THE RESIDUE STAGE 2.1 The 1.5-Bit Stage Figure 2.1 The 1.5-Bit per Stage Block Diagram [12] The architecture of the pipelined ADC being used for this project is a 1.5-bit/stage topology [11]. A block diagram of the residue stage used in the 1.5-bit/stage architecture is shown in Figure 2.1. This residue stage consists of three major sub-circuits: a Sub-ADC, a Sub-DAC, and an amplifier. Although each stage produces 1.5-bits, only 1-bit per stage is resolved after error correction so the amplifier uses a gain of 2 to amplify the residue back to full scale. Each residue stage provides an analog output, VOUT, and a 2-bit digital output, AN and BN. The analog output, VOUT, is the residue left after the analog representation of the bits resolved in the stage provided by the Sub-DAC 11 are subtracted, and provides the input signal, VIN, for the following stage. The two bits, AN and BN, are the encoded comparator bits from the Sub-ADC, which represent the portion of the signal converted in the stage, including an extra half bit of redundancy provided for the error correction performed later in the digital decode logic. The transfer functions and their corresponding analog and digital outputs for all possible inputs are listed in Table 2.1. Table 1.1 Ideal 1.5-Bit per Stage Transfer Functions [12] 2.2 The Sub-ADC and Sub-DAC The Sub-ADC has two primary functions, determining the values for the two digital bits, AN and BN, which are provided to the digital decode and error correction logic, and providing control bits which determine the switch settings (S1/S2/S3) to the Sub-DAC. Two comparators, a clocked RS latch, and an encoder comprise the circuitry of the Sub-ADC. As shown in Table 2.1, depending on the value of the input signal the transfer function contains the subtraction of either -Vref, zero, or +Vref from 2*VIN to create the output voltage, VOUT. Selection of the appropriate voltage to subtract is accomplished by the Sub-DAC, which consists of a network of switches that are controlled by the 12 Sub-ADCs output bits. Figure 2.2 shows the combined circuits for the Sub-ADC and the Sub-DAC. Figure 2.2 The Sub-ADC and Sub-DAC [12] The operation of the Sub-ADC and Sub-DAC is dependent upon four fully differential reference signals, shown single ended for simplicity in Figure 2.2, and three clock signals that control the three different modes of operation. The timing and theory of these modes of operation will be discussed in detail in the following section. Referring to Figure 2.2, the Sub-ADC and Sub-DAC operate as follows. The comparators sense the value of the input signal, VIN, and make a decision during the non-overlap time between the falling edge of the advanced clock for phase 1, Φ1ADV and the rising edge of the advanced clock for phase 2, Φ2ADV, sending their decisions to the latch. Note that the 13 comparators must make their decisions during the non-overlap time between clock phases, since they must wait until the output of the previous stage settles to start their conversions yet still provide their decisions to the sub-DAC at the start of next clock phase. When Φ2ADV goes high the clocked RS-latch latches the comparator outputs, preventing further changes in the latch output bits from occurring. This lock-out of later changes avoids errors in the near metastable cases when the comparator input and reference voltages have nearly the same value. On the rising edge of Φ2 the NAND based encoder produces signals S1 through S3 for use by the Sub-DAC, along with the output bits, AN and BN, for use by the digital decode and error correction logic. The network of switches which form the Sub-DAC determine the routing of the appropriate reference voltage to the residue amplifier based on the value of the encoder signals S1 through S3. In this design these switches were designed to be active low, meaning that they are closed when a logic 0 is input. Table 2.2 defines the operation of the Sub-ADC and Sub-DAC. 14 Table 2.1 Truth Table and Functional Description of the Sub-ADC and Sub-DAC [12] 2.3 Comparator Theory of Operation The comparator implemented in the pipelined ADC used for this project uses a latching topology with a preamplifier, which is similar to that used in [13]. A second differential pair was added to accommodate the four single-ended inputs required with fully differential signals for both the input voltage and the reference voltage. A swing-minimizing circuit (SMC) was used to reduce charge-injection errors due to clock 15 feed through [4] [6]. As shown in Figure 2.3 the comparator is comprised of three main circuits: a preamplifier, a regenerative stage and the SMC. Preamplifier Regenerative SMC Figure 3 Latching Comparator with Preamplifier [9] The preamplifier is comprised of two differential pairs and performs the function of subtracting the differential reference voltage, Vrefp - Vrefn, from the differential input signal, Vinp - Vinn. The positive single-ended input and reference voltages are applied to one differential pair, and the negative voltages to the other, to reduce the linear range needed by the differential pairs. One of the desirable attributes of the preamplifier is that it reduces the input referred offset voltage (Vos) of the comparator, including both static 16 offsets due to device mismatches and dynamic offsets due to charge injection. Preamplifiers are also effective at reducing kickback noise from the regenerative stage to the inputs. A tradeoff exists between the speed and offset of the latching comparator topology, with the sizing of the cross-coupled transistors in the regenerative stage being critical to circuit performance. Speed, offset, and power consumption are typically the key parameters that define a comparator’s performance. For a given bias current, the choice of minimum sized transistors ensures high speed performance, with the penalty being greater offsets because of their inherently larger random mismatches [8]. The alternative is to use larger devices that provide lower offsets, with the consequence being a reduction in speed due to their larger capacitances, unless a sacrifice in power is made by increasing the bias currents. The addition of the SMC circuitry provides the benefit of reducing the amount of charge injected onto the NMOS cross-coupled pair by limiting the signal swing on the gate of the reset switch. A simple current DAC within the SMC provides the ability to adjust the bias on the gate of the reset switch, to control the time constant during the reset phase and avoid memory effects. These benefits are obtained through the proper sizing of the transistors in the SMC that turn on and off the reset switch. 17 The operation of the latching comparator occurs over two regenerative time periods. The first regenerative time period, which is the shorter of the two, occurs during the short delay between the advanced and normal phases of the Φ 1 clock. During this time interval, the NMOS cross-coupled pair begins regenerating the small voltage difference provided by the preamplifier to a larger value. This voltage continues to grow exponentially with time because of the positive feedback. The second regenerative time period begins on the falling edge of Φ1, when the switches shown turn on to connect the PMOS cross-coupled pair at the top to the NMOS cross-coupled pair at the bottom, to aid in regeneration. The short delay between the two clocks allows the signal to grow somewhat before these switches are turned on, to reduce errors due to charge injection from the switches. At this point VOUT changes and triggers an RS latch (not included in this figure) which outputs a full swing digital CMOS representation of the comparator’s decision and latches the result, which is held during the reset phase. 18 Chapter 3 FAULT DIAGNOSIS AND REDESIGN OF THE COMPARATOR 3.1 Fault Diagnosis of the Original Comparator As mentioned previously, one of the comparator’s design-for-test (DFT) features which was intended to provide scalability of the reset time had minimal impact on the results, thus indicating improper biasing of the circuits used to implement this DFT feature. Scalability of the reset time was intended to be accomplished through adjustment of the reset switch (M16) impedance by controlling the reset signal (Vreset) supplied by the SMC (M19-28), as shown in Figure 3.1. Vdd M3 M4 M5 Vb M10 M11 M12 M13 M19 M20 M22 B0 Vout M6 Vrefp M7 M8 Vinp Vinn M21 Vb Φ1 M9 M14 M23 B1 M24 B2 M25 M15 Vrefn Vreset Ibias M16 M26 M27 B A M1 M2 M28 Φ1a M17 M18 Vss Figure 3.1 Schematic for the Original Comparator 19 A unique feature of this comparator was the programmability employed in the SMC to allow precise adjustment of the reset signal voltage, which was accomplished through the use of a simple current DAC (M19-M24). The current DAC used 3 bits and allowed the current to be varied from 200uA up to 900uA. Since little scalability of the comparators reset time was observed while toggling the bits of the current DAC, the fault diagnosis centered on evaluating the performance of the SMC (Figure 3.2). Vdd Vbias B2 M19 W=10.05u L=0.75u M=8 M20 W=10.05u L=0.75u M=12 M21 W=10.05u L=0.75u M=16 M22 W=3.0u L=0.6u M=1 M23 W=3.0u L=0.6u M=1 M24 W=3.0u L=0.6u Vss B1 B0 M=1 M25 W=3.0u L=0.6u M=1 Vreset M26 W=3.0u L=0.6u M=2 M27 W=3.0u L=0.6u M=1 Vss Φ1a M28 W=3.0u L=0.6u M=1 Figure 3.2 SMC used in the Original Comparator 20 3.1.1 Simulation Results The first step was to validate the operating point of all the devices in the SMC by performing a DC bias point analysis with all of the current DAC legs turned on. This required setting all of the current DAC bits (B0/B1/B2) and the compliment of Φ1 low. Setting this clock low puts the comparator into reset mode which is a worst-case scenario in terms of headroom since Vreset increases by the Vgs drop of M27. The simulation results indicated that all of the current legs (M19-21) and the cascode device (M25) were operating in the triode region rather than in saturation, as required for proper operation of the current DAC. Further investigation revealed a maximum current of 238µA was supplied by the current DAC instead of the designed value of 900µA with all of the DAC legs turned on. This extreme difference between the intended and actual values of the maximum current supplied by the DAC indicated a lack of ability to control the reset signal voltage and prompted the need for a simulation to determine the accuracy of the current supplied when the DAC was set to the minimum value. This required leaving the LSB set low (B2) and setting the remaining bits (B1,B0) high. The setting for the compliment of the clock remained the same as in the previous DC bias point analysis. The results indicated that the LSB current transistor (M19) and cascode device were operating in the triode region and that a minimum current of 163µA was supplied by the current DAC when an anticipated current of 200µA was expected. 21 Finally, a transient simulation was performed to determine the actual range of the reset voltage (Vreset), first with the current DAC set to the maximum value, and then with it set to the minimum value. The results are shown in Figure 3.3. As expected, the maximum value decreased the impedance of the reset switch which reduced the preamplifier gain to below unity. Unfortunately, the minimum DAC current did not increase the impedance of the reset switch to the point where the comparator performance suffered as a result of memory errors. A properly functioning DAC would have produced a Vreset voltage range extending over both of these boundary conditions, exercising both performance limitations of the comparator, which was the original intent of this design-for-test (DFT) feature. Without a properly functioning DAC an optimal reset switch impedance could not be determined. This was particularly problematic on the low end, since it was determined later that currents far below the minimum DAC current were actually needed. Figure 3.3 Vreset Range for the Original Comparator 22 Figure 3.3 Ra for the Original Comparator 23 3.1.2 Effects on Comparator Performance Parameter Value Offset <100mV Decision Time <5ns Area <0.03mm2 Power Minimum Possible Table 3.1 Comparator Design Specifications The design specifications for the original comparator are given in Table 3.1. The improper biasing of the current DAC within the SMC rendered the original comparator inoperable at the slow process corner, while operating at a low supply voltage and high temperature. It also contributed to a lack of control over the adjustable reset voltage, resulting in little variation in the reset time and essentially a useless DFT feature. Furthermore, having several devices operating in the triode region also greatly increased the capacitance on the reset node, which increased the decision time required for the comparator. Further testing of the original comparator with the Dynamic Offset Test Bench (DOTB) [7] indicated that the range of current values achieved by the current DAC were less than optimal and contributed to a high input referred offset voltage. It was determined that the 24 maximum design value for the DAC current of 900uA established a gain of less than unity for the comparator during reset at this DAC setting, which would result in the inputreferred offset being higher than any offset voltage developed across the regenerative nodes A and B in Figure 3.1. In an effort to establish the optimal range for the current DAC in the SMC, the DAC was replaced with an ideal current source, and the input offset voltage for the comparator was measured using the DOTB over the range of current values shown in Table 3.2 [15]. Ibias (µA) Vos (mV) Ibias (µA) Vos (mV) Ibias (µA) Vos (mV) 200 32.1 150 18.6 100 5.4 190 29.4 140 15.5 90 4.0 180 27.3 130 12.4 80 3.0 170 24.9 120 9.4 70 0.8 160 22.2 110 7.1 60 0.6 Table 3.2 Input Referred Comparator Offset Voltage vs. DAC current Referring to Table 3.2, a predictable trend is observed between the reduction of the input referred offset voltage and the current being sourced by the DAC in the SMC. As stated previously, the impedance of the reset switch is controlled by varying the value of the reset voltage (Vreset), and the reset switch also serves as a key part of the load for the preamplifier. There exists two boundaries for the impedance values that the reset switch 25 must have to ensure proper operation of the comparator. The first being if the current sourced by the DAC is too high. This condition reduces the reset switch impedance, thus ensuring no errors occur due to memory of previous decisions, with the tradeoff being that a preamplifier gain of less than unity causes an increase in the input referred offset voltage. The second boundary condition occurs when the current sourced by the DAC is too low. This condition has the exact opposite effect, creating the desired outcome of having a preamplifier gain that is greater than unity, which reduces the input referred offset voltage. Unfortunately, the limiting factor in this case is that when the reset switch impedance is set too high, then comparator performance suffers as a result of memory errors. Use of the current values listed in Table 3.2 for the DAC in a transient analysis of the comparator led to the conclusion that the minimum and maximum values for the DAC current range should be set to 75µA and 250µA, respectively. It was observed that current values in excess of 250µA generated an excessively large input referred offset voltage because the preamplifier gain was less than unity due to the low reset switch impedance. Furthermore, the comparator proved to be incapable of making a decision for current values less than 75µA. This was attributed to memory errors caused by the inability of the reset switch to equalize the potential between nodes A and B in Figure 3.1 in the time available, due to the high switch resistance. 26 3.2 Redesign of the Comparator Based on the results determined during the fault analysis of the original comparator SMC shown in Figure 3.2, it was determined that modifications were necessary to ensure the ability to properly adjust the reset time, and more importantly, to ensure that the comparator performs correctly and meets all of the specifications listed in Table 3.1. The following items were addressed during the redesign of the comparator: 1. Modify the range of current values being supplied by the current DAC 2. Evaluate ways to improve headroom constraints 3. Size the DAC switches (M22-24) based on current density 4. Adjust the size of cascode device (M25) 3.2.1 Detailed Explanation of the Redesigned Comparator The first step taken in the redesign of the comparator was to determine the correct range and resolution for the current DAC. As stated previously, the upper and lower boundary conditions for the correct operation of the SMC are 250µA and 75µA respectively, so this became the target specification for the new current DAC. One of the drawbacks of the original current DAC design was that it supplied no current to the SMC with all of the DAC bits set high. This limitation coupled with a desired step size of 25µA led to the decision to add an additional current leg to the DAC that would supply a minimum output 27 current regardless of the DAC bit settings. Table 3.3 lists the range and step size provided by the original current DAC and the target for the redesigned DAC. B2 B1 B0 Original DAC Redesigned DAC 1 1 1 0µA 75µA 1 1 0 200µA 100µA 1 0 1 300µA 125µA 1 0 0 400µA 150µA 0 1 1 500µA 175µA 0 1 0 600µA 200µA 0 0 1 700µA 225µA 0 0 0 900µA 250µA Table 3.3 Original vs. Redesigned DAC Current Range Figure 3.4 shows the schematic of the redesigned comparator SMC. In order to meet the specifications for step size and current range listed in Table 3.3, several modifications had to be made to the original current DAC. The first was to use a wide-swing cascode current mirror topology to alleviate the headroom constraints found in the original SMC design. As mentioned previously, an additional current leg (M35-36) was added to supply current for an input code of 111 and all of the current DAC switch sizes (M22-23, M34, M36) were scaled according to current density to ensure a uniform Vds drop across all of the switches. The final modification to the current DAC was a reduction in the bias current for the diode-connected device (M30) from 100µA to 50µA, which was necessary to establish the step sizes listed in Table 3.2. The redesigned current DAC provides a 28 minimum output current of 75µA from the additional leg which can be increased up to 250uA in 25uA steps using the DAC input bits B0-B2. VDD M29 W=6.0u L=1.1u M=4 M31 W=3.0u L=0.6u M=4 M30 W=10.05u L=0.75u M=4 M32 W=3.0u L=0.6u M=4 M30 W=10.05u L=0.75u M=4 M19 W=10.05u L=0.75u M=2 M20 W=10.05u L=0.75u M=4 M33 W=10.05u L=0.75u M=8 Vss B2 M22 W=3.0u L=0.6u B1 M=2 M23 W=3.0u L=0.6u B0 M=4 M34 W=3.0u L=0.6u Vss M=8 M35 W=10.05u L=0.75u M=6 M36 W=3.0u L=0.6u M=6 M25 W=8u L=0.6u M=12 Vcascode Vreset M26 W=3.0u L=0.6u M=2 M27 W=3.0u L=0.6u M=1 VSS Φ1a M28 W=3.0u L=0.6u M=1 Figure 3.4 Redesigned Comparator SMC During the fault diagnosis of the original comparator it was determined that a key contributor to the lack of headroom for the DAC was the biasing of the cascode device (M25), which forced all of the current legs into the triode region of operation. This device had been strategically placed between the current DAC and the reset node (Vreset) to 29 shield the reset node from the output capacitance of the DAC, thereby maintaining the switching speed of the reset signal while still reducing the swing. Unfortunately, due to improper sizing the cascode device was also operating in the triode region, thus coupling all of the output capacitance of the current DAC to the reset node, making the cascode device useless and slowing the speed of the comparator. Reviewing the headroom constraints for all of the devices within the original comparator SMC led to the conclusion that there were two easily identifiable faults with the design of the cascode device. First, it was a minimum sized device conducting currents ranging from 200µA to 900µA, which resulted in excessive Vgs values ranging from 3.2V to 5.6V respectively. Second, simulation results over process corners indicated that this device could not remain in saturation with its gate tied to VSS. Resizing the cascode device for the new maximum current value of 250µA corrected the first fault and adding an additional bias leg (M29/M31) to create a bias potential (Vcascode) for the gate of the cascode device corrected the second fault. 3.2.2 Simulation Results for the Redesigned Comparator Results obtained from a DC bias point analysis conducted over process, supply voltage and temperature (PVT) corners for each of the eight DAC settings for the redesigned comparator circuit shown in Figure 3.5 indicated that all of the devices within the SMC met headroom requirements and were operating within their intended region. 30 To complete the evaluation of the redesigned comparator, the parasitic capacitances were extracted from the new layout and included in the simulations. The results are displayed below in Figure 3.6, and show the improvement in the range of the reset signal (Vreset) produced by the redesigned comparator SMC for the maximum and minimum current DAC values. Vdd M3 M4 M10 M5 Vb M11 M12 M13 M29 M30 M31 M32 Vrefp M21 M7 M8 Vinp Vinn M23 M22 Vss B2 Vout M6 M20 M19 M33 Φ1 B1 M24 B0 M34 Vss M25 M9 M14 M15 Vcascode Vrefn Vreset M16 Ibias M26 M27 M1 M2 M28 Vg Φ1a Vg M17 M18 M35 M36 Vss Figure 3.5 Schematic for the Redesigned Comparator Figure 3.6 Vreset Range for the Redesigned Comparator 31 Figure 3.6 for the Redesigned Comparator 32 Extensive simulations were performed on the redesigned comparator to see how the circuit behaved as the input signal was decreased over three PVT corners, slow (SS), typical (TT), and fast (FF). As expected, as the difference between the input signal and reference voltage decreases, the comparison time increases. To verify performance, an overdrive recovery test was performed on the redesigned comparator with and without parasitic capacitances. For this test the comparator was initially driven with a full-scale input in one direction and then a 0.5-LSB input in the opposite direction on the next clock cycle. The decision times of the original and redesigned comparator, with and without parasitics, are listed in Table 3.4. Figure 3.7 is a plot of the redesigned comparator performance for the worst-case corner (SS), and Figure 3.8 displays the decision time of the comparator at this same PVT corner. Corner Temp Supply Original Redesigned Original Redesigned Comparator Comparator Comparator Comparator Decision Decision Decision Decision Time W/O Time W/O Time W/ Time W/ Parasitics Parasitics Parasitics Parasitics SS 85° 4.5V 3.16ns 939.24ps 3.72ns 1.60ns TT 25° 5.0V 1.62ns 735.85ps 2.08ns 1.26ns FF 0° 5.5V 1.22ns 631.83ps 1.29ns 1.08ns Table 3.4 Original and Redesigned Comparator Decision Times Vin = 0.24V Vin = -1.0V Vin = 0.26V Figure 3.7 10mV Overdrive Recovery Test for the Redesigned Comparator Vref = 0.25V Vin = 1.0V 33 Figure 3.7 Overdrive Recovery Test for the Redesigned Comparator 34 Figure 3.8 Decision Time for the Redesigned Comparator at the SS PVT Corner Figure 3.8 Decision Time for the Redesigned Comparator at the SS PVT Corner 35 Chapter 4 LAYOUT 4.1 Original Comparator Layout The layout for the original comparator shown in Figure 4.1 met the maximum area specification set in Table 3.1 and left ample white space – a less dense layout as a result of large spacing between components – which will be discussed in the following section as a benefit to the layout of the redesigned comparator. Figure 4.1 Layout for the Original Comparator [9] Prior to starting the layout for the redesigned comparator a review was performed on the layout for the original comparator to identify if further optimization of performance could be obtained through changes in component placement. Tracing of the high-speed input signals’ propagation path through the comparator revealed that it was subjected to several differential turns, primarily between the output of the comparator and the PMOS cross- 36 coupled pair. It was noted that optimization for speed through reduction of parasitic capacitances associated with the high-speed signal path could be obtained by removing the differential turns through reconfiguration of component placement to create a linear path [16]. 4.2 Redesigned Comparator Layout The layout for the redesigned comparator shown in Figure 4.2 is denser than the original comparator layout as a result of increased device count and area from the proposed modifications, but still met the maximum area specification set in Table 3.1. It also fit in the space available in the overall chip layout, which was an important additional requirement. Figure 4.2 Layout for the Redesigned Comparator 37 Reduction of the parasitic capacitances associated with the high-speed signal path was accomplished by reconfiguring the device placements to obtain a straight path between the preamplifier output, the NMOS cross-coupled pair and the output of the comparator. This led to an improvement in the decision time of the redesigned comparator. The redesigned comparator layout is comprised of two sections, analog and digital. This is a common practice employed in mixed-signal design to isolate clocks from coupling into sensitive analog signal nodes, which would corrupt the integrity of the sampled signal. Figure 4.3 is the analog section of the layout for the redesigned comparator. The NMOS and PMOS current mirrors use a common centroid layout centered around the reference to reduce errors in the currents. The preamplifier’s input differential pairs are placed strategically below the PMOS current mirror to reduce routing, thus minimizing parasitic capacitances. The best way to reduce random offsets as a result of process variation within a differential pair is to interdigitate the transistors. However, because the transistors in the differential pairs are small and the extra capacitive loading this requires was not desired, a Photo Lithographically Invariant (PLI) layout with step symmetry was used instead, which in this case provided better results due to the required speed of the comparator [9]. 38 Figure 4.3 Layout for the Current Mirrors and Preamplifier Figure 4.4 is the layout for the reset switch, which is comprised of two minimum sized transistors, and is the key contributor to balancing the parasitic capacitances between the critical regenerative nodes, which are labeled A and B in Figure 4.4. A significant improvement between the original and redesigned comparator layout is the close matching of the parasitic capacitances between these nodes, which is essential to obtain a low dynamic offset. The extracted capacitance values for nodes A and B in the original comparator layout were 0.5023 fF and 0.5138 fF, respectively. These values were reduced by approximately 50% in the layout for the redesigned comparator because of the previously mentioned signal path improvements. After several iterations on the stubs for the reset switch, by adjusting the length of metal for each stub, an extracted value of 39 0.2593 fF and 0.2578 fF for nodes A and B was obtained [16]. This reduced the percent difference between the parasitic capacitances on nodes A and B from 2.3% in the original layout to only 0.6% in the new layout. Figure 4.4 Layout for the Reset Switch 40 Figure 4.5 Layout for the SMC Figure 4.5 shows the right hand “digital” side of the redesigned comparator. Careful planning and thought went into the placement of devices to ensure that maximum separation between the output of the second regenerative latch (PMOS cross-coupled pair) and the SMC circuitry was used to avoid coupling clock noise into the sensitive regenerative nodes. 41 Chapter 5 CONCLUSIONS The objective of this project was the fault diagnosis and comparator redesign for an 8-bit 20-MS/s calibrated pipelined analog-to-digital converter in 0.5-µm CMOS. Simulation results obtained during the fault diagnosis phase identified several transistors within the current DAC and SMC that were not operating in the saturation region. The redesign effort was comprised of changing the DAC current mirror topology to a wide-swing cascode to improve headroom, resizing of the DAC switches for equal Vds drops, and resizing of the SMC cascode device to ensure proper biasing over PVT corners. Verification of performance of the proposed modifications was obtained through simulation results of an extracted netlist from the redesigned comparator layout. Successful implementation of the redesigned comparator will be determined upon evaluation of test results pending the fabrication of the pipelined analog-to-digital converter. 42 REFERENCES [1] Savengsveksa, Vilaysack, “The Design of an 8-bit 20-MSample/s Pipelined Analog-to-Digital Converter,” California State University, Sacramento, May 2007. [2] Perry L. Heedley and Thomas W. Matthews, “An Engineering Team Approach to Mentoring Graduate Students through Projects,” 2005 American Society for Engineering Education Annual Conference. [3] Perry L. Heedley, Kenneth C. Dyer, Thomas W. Matthews, Patrick Isakanian and Chuc Thanh, “A 30-mW 8-b 125MS/s Pipelined ADC in 0.13µm CMOS,” 2005 IEEE International Midwest Symposium on Circuits and Systems. [4] Perry L. Heedley, Kenneth C. Dyer, Thomas W. Matthews, Patrick Isakanian and Chuc Thanh, “A 30-mW 8-b 125-MS/s Pipelined ADC in 0.13-µm CMOS,” Analog Integrated Circuits and Signal Processing, vol. 56, numbers 1-2, pp. 43-51, March 2008. [5] David Flowers, Kenneth Dyer, Darshinee Patel, Pritesh Shah, Tapan Shah, Perry Heedley, and Thomas Matthews, “A Simplified Calibration Technique for Pipelined ADCs using Reference Tapering,” 2008 IEEE International Midwest Symposium on Circuits and Systems. 43 [6] Vilaysack Savengsveksa, Perry L. Heedley, Thomas Matthews, Kamel Ahmad, and Jose Negrete, “An 8-b 20Msample/s Pipelined A/D Converter in 0.5-µm CMOS with 7.8 ENOB,” 2005 IEEE International Midwest Symposium on Circuits and Systems. [7] Thomas W. Matthews and Perry L. Heedley, “A Simulation Method for Accurately Determining DC and Dynamic Offsets in Comparators,” 2005 IEEE International Midwest Symposium on Circuits and Systems. [8] Marcel J. M. Pelgrom, A.C.J. Duinmaijer, and A.P.G. Welbers, “Matching properties of MOS transistors,” IEEE J. of Solid-State Circuits, vol. 23, no. 6, pp. 1324-1333, Dec. 1988. [9] Jose Emmanuel Negrete, “Design of a Comparator Circuit for an 8 Bit 20 MHz Pipelined Analog-to-Digital Converter in 0.5µm CMOS,” California State University, Sacramento, May 2006. [10] P. Kwok and H. Luong, “Power Optimization for Pipelined Analog-to-Digital Converters,” IEEE Trans. Circuits Syst. II, vol. 46, no. 5, pp. 549-553, May 1999. [11] Stephen H. Lewis, H. Scott Fetterman, George F. Gross, Jr., R. Ramachandran, and T. R. Viswanathan, “A 10-b 20-Msample/s Analog-to-Digital Converter,” IEEE J. Solid-State Circuits, vol. 27, no. 3, Mar. 1992. 44 [12] Kevin B. Geoghegan, “Design of an 8-bit, Pipelined, Analog-to-Digital Converter Implemented in a 0.5-µm CMOS Process,” California State University, Sacramento, May 2006. [13] G. M. Yin. F. O. Eynde, and W. Sansen, “A high-speed CMOS comparator with 8-bit resolution,” IEEE J. of Solid-State Circuits, vol. 27, pp.208-211, February 1992. [14] David W. Cline and Paul R. Gray, “A Power Optimized 13-b 5 Msamples/s Pipelined Analog-to-Digital Converter in 1.2µm CMOS,” IEEE J. of Solid-State Circuits, vol. 31, no. 3, March 1996. [15] Thomas W. Matthews and Perry L. Heedley, private communication. [16] Tom Palomino, private communication.