DESIGN OF A CHARGE PUMP FOR A PHASE LOCKED LOOP

advertisement

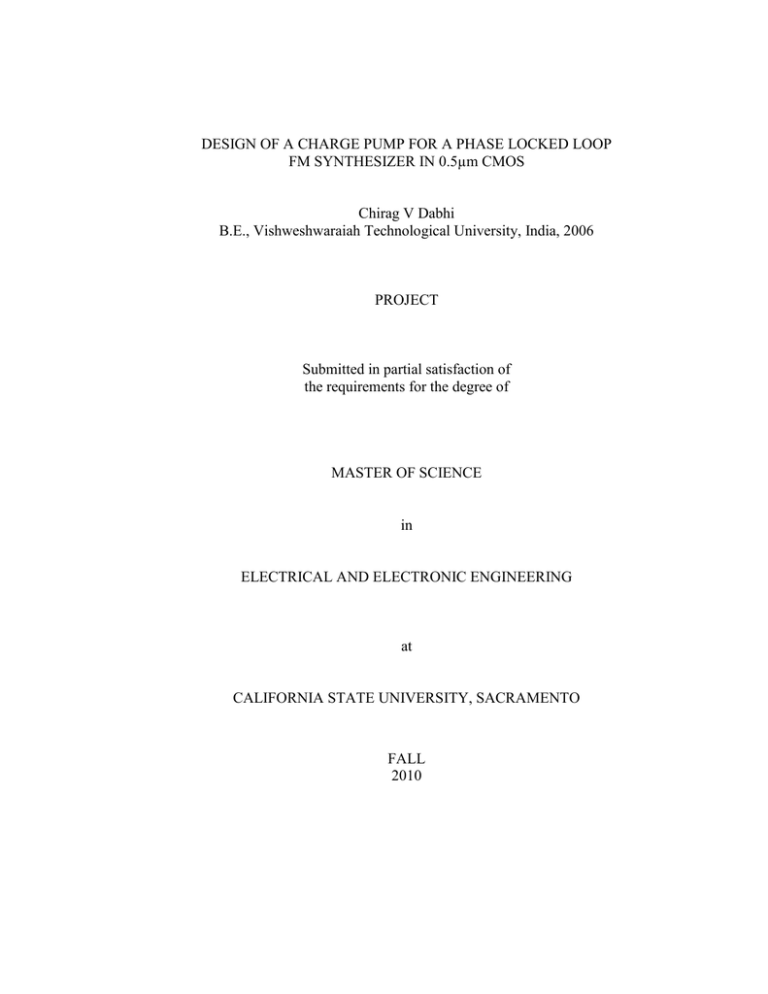

DESIGN OF A CHARGE PUMP FOR A PHASE LOCKED LOOP FM SYNTHESIZER IN 0.5µm CMOS Chirag V Dabhi B.E., Vishweshwaraiah Technological University, India, 2006 PROJECT Submitted in partial satisfaction of the requirements for the degree of MASTER OF SCIENCE in ELECTRICAL AND ELECTRONIC ENGINEERING at CALIFORNIA STATE UNIVERSITY, SACRAMENTO FALL 2010 DESIGN OF A CHARGE PUMP FOR A PHASE LOCKED LOOP FM SYNTHESIZER IN 0.5µm CMOS A Project by Chirag V Dabhi Approved by: __________________________________, Committee Chair Perry Heedley, Ph.D. ____________________________ Date __________________________________, Second Reader Thomas Matthews, Ph.D. ____________________________ Date ii Student: Chirag V Dabhi I certify that this student has met the requirements for format contained in the University format manual, and that this project is suitable for shelving in the Library and credit is to be awarded for the Project. __________________________, Graduate Coordinator Dr. Preetham B. Kumar Department of Electrical and Electronic Engineering iii ________________ Date Abstract of DESIGN OF A CHARGE PUMP FOR A PHASE LOCKED LOOP FM SYNTHESIZER IN 0.5µm CMOS by Chirag V Dabhi The aim of this project was to design, simulate and layout a charge pump for a phase-locked loop (PLL) FM synthesizer in a 0.5um CMOS process. The charge pump uses Up and Down input signals provided by a phase-frequency detector and converts them into output charge pulses integrated on a loop filter capacitor. According to the difference between the reference clock and the divided output of the voltage-controlled oscillator (VCO), the charge pump charges or discharges the loop filter capacitor. The capacitor voltage is subsequently used to control the frequency of the VCO, thereby controlling the frequency at the output of the PLL. ______________________, Committee Chair Perry Heedley, Ph.D. ______________________ Date iv ACKNOWLEDGMENTS This project would not have been possible without the help of Dr. Perry Heedley and many other people who assisted me. Dr. Heedley’s help sessions really helped me through the completion of this project from the architecture study through the completed layout. I would also like to thank my team mates, Jaydip Patel and Pramod Kapadia, for their support, as well as Dr. Thomas Matthews for his advice on my design and Chad Beach for his CAD support. I would also like to thanks my parents, sisters and wife for their love, support and continuous encouragement. I dedicate this work to all those who helped me through this project. v TABLE OF CONTENTS Page Acknowledgments......................................................................................................... v List of Tables ............................................................................................................ viii List of Figures ............................................................................................................. ix Chapter 1. INTRODUCTION ................................................................................................. 1 Operation of a Phase-Locked Loop ................................................................. 1 Objective .......................................................................................................... 3 Methodology ..................................................................................................... 3 Organization of Report .................................................................................... 4 2. CHARGE PUMP ARCHITECTURE .................................................................... 5 Charge Pump Operation .................................................................................... 5 Selected Charge Pump Architecture ................................................................. 8 3. CHARGE PUMP DESIGN CONSIDERATIONS …………………………… . 13 Dead Zone ...................................................................................................... 14 Current and Switching Time Mismatch .......................................................... 17 Charge Sharing................................................................................................ 22 4. CHARGE PUMP DESIGN CALCULATIONS .................................................. 25 Design Specifications...................................................................................... 25 Current Source Design .................................................................................... 26 Current Sink Design ........................................................................................ 29 Unity Gain Buffer Design ............................................................................... 32 Charge Pump Triode Switch Design............................................................... 34 5. SIMULATIONS .................................................................................................. 36 Charge Output Vs Phase Difference ............................................................... 36 Charge Output Vs Output Voltage .................................................................. 39 vi Dead Zone ....................................................................................................... 41 Post-Layout Simulations ................................................................................. 44 6. FLOORPLANNING AND LAYOUT ................................................................. 49 Floorplanning of the Charge Pump ............................................................... 49 Layout of the Current Source ......................................................................... 50 Layout of the Current Sink ............................................................................. 51 Layout of the Unity Gain Buffer ..................................................................... 52 Full Layout of the Charge Pump ..................................................................... 53 7. CONCLUSION ..................................................................................................... 54 References ……………. . ........................................................................................... 55 vii LIST OF TABLES Page 1. Table 4.1 Design Specifications for the Charge Pump ..…..…..……………... 25 2. Table 4.2 Device Sizes for the PMOS Wide-Swing Cascode Current Source . 29 3. Table 4.3 Device Sizes for the NMOS Wide-Swing Cascode Current Sink .....31 4. Table 4.4 Device Sizes for the Charge Pump Switches ………… ………….. 35 viii LIST OF FIGURES Page 1. Figure 1.1 Block Diagram of a Phase-Locked Loop ………... …………..… 1 2. Figure 2.1 Charge Pump with Phase Frequency Detector …...………..…… 5 3. Figure 2.2 Charge Pump Response ….....……………..……………….. …. 7 4. Figure 2.3 Loop Filter … ……………………….…….………………….... 7 5. Figure 2.4 Selected Charge Pump Architecture ……..………..……… ….. 9 6. Figure 2.5 Circuit Used to Provide Complementary CMOS Inputs to the Charge Pump ……………………………………………………. 10 7. Figure 2.6 Single Ended Charge Pumps …… ………………………….. 8. Figure 3.1 PFD’s Output Narrow Up and Down Pulses for Zero Phase Difference ………………………………………………………. 14 9. Figure 3.2 Output Waveforms for the Phase Frequency Detector (PFD) … … 15 10. Figure 3.3 Dead Zone in the Charge Pump Response . …………………..… 16 11. Figure 3.4 Jitter Resulting from the Dead Zone . ………………..………… 17 12. Figure 3.5 Implementation of Current Sources using MOS Transistors …... 18 13. Figure 3.6 Effect of Iup and Idw Current Mismatch ………………………… 20 14. Figure 3.7 Effect of Switching Time Mismatch ……………………………... 21 15. Figure 3.8 (a) Schematic Illustrating Charge Sharing between Nodes A,B and the Loop Filter Capacitor …………………………………… 23 16. Figure 3.8 (b) Waveforms Illustrating Charge Sharing between Nodes A,B and the Loop Filter Capacitor …………………………………… 24 17. Figure 4.1 Wide-Swing Cascode Current Source used in Charge Pump …… 26 18. Figure 4.2 Wide-Swing Cascode Current Sink used in Charge Pump ……….30 ix 11 19. Figure 4.3 Unity Gain Buffer …...…………………………………………….. 32 20. Figure 5.1 Charge Output in Pico-Columbs vs. Phase Difference in Degrees for the TT Corner …………………………………………….……. 37 21. Figure 5.2 Charge Output in Pico-Columbs vs. Phase Difference in Degrees for the SS Corner …………………………………………….……. 37 22. Figure 5.3 Charge Output in Pico-Columbs vs. Phase Difference in Degrees for the FF Corner …………………………………………….……. 38 23. Figure 5.4 Variations in Output Charge over the Output Voltage Range (TT Corner ) ……………………………………………………..... 39 24. Figure 5.5 Variations in Output Charge over the Output Voltage Range (SS Corner ) ……………………………………………………..... 40 25. Figure 5.6 Variations in Output Charge over the Output Voltage Range (FF Corner ) ……………………………………………………..... 40 26. Figure 5.7 Charge Output with Zero Phase Difference Showing No Dead Zone Exists (TT corner ) ………………………………………………... 42 27. Figure 5.8 Charge Output with Zero Phase Difference Showing No Dead Zone Exists (SS corner ) ………………………………………………... 43 28. Figure 5.9 Charge Output with Zero Phase Difference Showing No Dead Zone Exists (FF corner ) ………………………………………………... 43 29. Figure 5.10 Charge Output in Pico-Columbs vs. Phase Difference in Degrees Including Back-Annotated Layout Parasitics (TT corner) ……….. 44 30. Figure 5.11 Charge Output in Pico-Columbs vs. Phase Difference in Degrees Including Back-Annotated Layout Parasitics (SS corner) ……….. 45 31. Figure 5.12 Charge Output in Pico-Columbs vs. Phase Difference in Degrees Including Back-Annotated Layout Parasitics (FF corner) ……….. 45 32. Figure 5.13 Variations in Output Charge over the Output Voltage Range Including Back-Annotated Layout Parasitics (TT corner) …….… 46 x 33. Figure 5.14 Variations in Output Charge over the Output Voltage Range Including Back-Annotated Layout Parasitics (SS corner) .…….…46 34. Figure 5.15 Variations in Output Charge over the Output Voltage Range Including Back-Annotated Layout Parasitics (FF corner) .…….…47 35. Figure 5.16 Charge Output with Zero Phase Difference Including Back-Annotated Layout Parasitics Showing No Dead Zone Exists (TT corner) ……………………………………………………..…47 36. Figure 5.17 Charge Output with Zero Phase Difference Including Back-Annotated Layout Parasitics Showing No Dead Zone Exists (SS corner) ……………………………………………………..…48 37. Figure 5.18 Charge Output with Zero Phase Difference Including Back-Annotated Layout Parasitics Showing No Dead Zone Exists (FF corner) ……………………………………………………..…48 38. Figure 6.1 Floorplan for the Charge Pump Layout ……………………… ….. 49 39. Figure 6.2 Layout of the Current Source ………………………………….… 50 40. Figure 6.3 Layout of the Current Sink ………………………………….…… 51 41. Figure 6.4 Layout of the Unity Gain Buffer ………………………………… 52 42. Figure 6.5 Full Layout of the Charge Pump ………………………….…….. 53 xi 1 Chapter 1 INTRODUCTION Operation of a Phase-Locked Loop A Phase-Locked Loop (PLL) is a closed-loop negative feedback control system that maintains a generated system clock with a fixed relation to the phase of a reference clock. Figure 1.1 Block Diagram of a Phase-Locked Loop [6] Figure 1.1 shows the general block diagram of a phase-locked loop. The major building blocks of the phase-locked loop are a phase frequency detector, a charge pump, a loop filter, a voltage-controlled oscillator and a frequency divider. As shown in Figure 1.1, the reference clock is generated off-chip from an accurate reference such as a crystal oscillator. The reference clock is compared with a divided version of the system clock 2 using a phase frequency detector (PFD). The phase frequency detector compares the phase and frequency between the reference clock and the divided clock, and produces either a pump up or pump down signal when the divided clock either lags or leads the reference clock, respectively. The pump up and pump down signals are fed into the charge pump, which converts these signals into positive and negative current pulses. These current pulses charge or discharge the loop filter to produce the control voltage (Vcntrl) which controls the frequency of the voltage-controlled oscillator (VCO). The pump up signal charges the loop filter thereby increasing the voltage on the loop filter, which in turn increases the frequency of the voltage-controlled oscillator. This causes the divided clock to increase in frequency until it is in phase with the reference clock. The pump down signal, on the other hand, discharges the loop filter thereby decreasing the voltage on the loop filter, which in turn decreases the frequency of the voltage-controlled oscillator to eliminate the phase lead of the VCO clock. An ideal phase-locked loop generates a system clock with edges occurring at fixed intervals in time. However, an actual PLL system clock experiences small variations in the timing of these edges from their ideal points in time. This variation in the period of the system clock is called jitter. The loop filter voltage controls the frequency of the voltage-controlled oscillator. The loop filter removes any high frequency components of the loop filter voltage and smoothes out its response thereby reducing jitter. The frequency of the crystal oscillator is accurate but the maximum frequency available is approximately 150 MHz. Phase-locked loops can generate very accurate 3 low-jitter clocks at higher frequencies. Phase-locked loops are widely used in frequency synthesizers, for demodulation of both AM and FM signals, and to generate higher frequency clocks in the gigahertz range for digital integrated circuits (ICs) such as microprocessors. Objective A team of Electrical and Electronics Engineering graduate students at California State University, Sacramento undertook a project to develop phase-locked loop for a FM synthesizer in a 0.5µm CMOS process. The objective of this project was to build a phase-locked loop for a FM synthesizer. Each student on the team was responsible for a specific block for the phase-locked loop IC. The author of this report was responsible for the design and layout of the charge pump. For more information on the other building blocks of the phaselocked loop, please see the following references [6, 7, 8 and 9]. Methodology To build this phase-locked loop IC, we followed an industrial analog design methodology, which consists of four major phases: Architecture phase, Preliminary Design phase, Layout phase and Final Design phase. During the architecture phase the circuit topologies to be used during the design are decided. The preliminary design phase includes the transistor-level design of all circuits needed to meet the given specification. The layout phase covers the physical design of all the circuit blocks in the design. The 4 final design phase covers post-layout simulations and layout changes needed to meet all the specifications. The phase-locked loop design and layout was done using IC design tools from Mentor Graphics. The MOSIS educational program provided silicon for the fabrication of this phase-locked loop. Organization of Report Chapter 2 discusses the operation of the charge pump circuit and the charge pump architecture selected for this phase-locked loop. Chapter 3 discusses charge pump design considerations for the selected architecture. Chapter 4 discusses design calculations of the various blocks of the charge pump architecture. Chapter 5 discusses preliminary design simulations for the charge pump. Chapter 6 discusses the floorplan and layout of the entire charge pump. Chapter 7 discusses conclusions drawn at the end of design and layout of the charge pump. 5 Chapter 2 CHARGE PUMP ARCHITECTURE Figure 2.1 Charge Pump with Phase Frequency Detector [12] Charge Pump Operation Figure 2.1 shows the basic architecture of the charge pump with a phase frequency detector and a loop filter capacitor Cp. The charge pump consists of two current sources and the switches used to connect these current sources to the loop filter capacitor. The top current source is connected to switch S1 to source current and the bottom current source is connected to switch S2 to sink current. The phase frequency detector (PFD) is a digital logic circuit, which compares the frequency and phase between 6 the reference clock and a divided version of the VCO clock. The PFD generates Up or Down signals to increase or decrease the charge stored on the loop filter capacitor and thereby increase or decrease the VCO control voltage labeled Vcntrl in the figure. If the reference clock leads the divided clock, the phase frequency detector outputs an UP signal; if the reference clock lags the divided clock a DOWN signal is generated. However, when both the reference and divided clocks have the same frequency and phase the phase frequency detector generates narrow Up and Down pulses. For more information about the operation of the phase frequency detector, please refer to reference [3]. The Up signal turns on the S1 switch, which adds charge to the capacitor Cp to increase Vcntrl, which increases the frequency of the voltage-controlled oscillator. As the voltage on the loop filter increases the frequency of the voltage-controlled oscillator increases to cause the phase of the divided clock to increase to align with the reference clock. On the other hand, the down signal turns on the S2 switch, which removes charge from the capacitor Cp, thereby decreasing the voltage on the loop filter to correct the phase lead of the divided clock. Figures 2.2a and 2.2b show the operation of the Up and Down signals. When both the Up and Down signals are low both S1 and S2 are off, thereby maintaining a constant voltage on the loop filter. 7 Figure 2.2 a Figure 2.2 b Figure 2.2 Charge Pump Response [12] Figure 2.3 Loop Filter [9] 8 Figure 2.3 shows the architecture of the complete loop filter. Capacitor C1 is the main loop filter capacitor while C2 is added to remove glitches. Resistor Rp is added to stabilize the response of the complete loop by adding a zero to improve the phase margin. For more information on the loop filter, please refer to references [4 and 9]. Selected Charge Pump Architecture Figure 2.4 shows the architecture of the selected charge pump, which has a single-ended output and complementary digital CMOS logic signals as inputs. The single-ended output does not need differential loop filters, which makes the phase-locked loop design more compact in terms of area since the loop filter requires the most area of the overall phase-locked loop. Of the available charge pump architectures, the selected architecture reduces the charge-sharing problem effectively [7]. Figure 2.6 shows some of the other available architectures [2]. Figure 2.4 shows the selected charge pump architecture with the CMOS digital inputs UP, UPB, DW and DWB controlling MOS switches, which operate in the triode region. The outputs of the phase frequency detector are full-swing (VDD to ground) CMOS logic signals, which drive the MOS switches shown in Figure 2.4. One of the advantages of this type of charge pump is that it does not require an extra circuit to convert the CMOS inputs into limited-swing differential signals like current-mode logic (CML) inputs would. The outputs of the phase frequency detector are the full-swing CMOS logic pump up and pump down signals. So this architecture does require an extra 9 circuit to provide the needed complementary CMOS signals, as well as to align these signals in time. Figure 2.5 shows the circuit used to accomplish this. Figure 2.4 Selected Charge Pump Architecture 10 Figure 2.5 Circuit used to Provide Complementary CMOS Inputs to the Charge Pump As shown in Figure 2.4, the selected charge pump architecture consists of two current mirrors, an operational amplifier and four MOS switches working in the triode region. In practice, CMOS wide-swing cascode current mirror circuits are used to implement the ideal current sources IUP and IDW. CMOS wide-swing cascode current mirrors increase the output impedance and output voltage swing of the charge pump. In this architecture the current sources are always on, so nodes A and B would charge to Vdd or discharge to Gnd when the switches turn off if not for the opamp. This unity gain buffer prevents the charge sharing errors this would cause by keeping nodes A and B at the loop filter voltage. The main function of this operational amplifier is to keep the voltage at the drains of the triode switches at the loop filter voltage. 11 Figure 2.6 Single Ended Charge Pumps (a) Switch in Drain, (b) Switch in Gate, (c) Switch in Source. [2] Three possible topologies are shown in Figure 2.6 for single-ended charge pumps. Figure 2.6 (a) shows a circuit where the MOS switches are placed in the drains of the current mirror FETs. In this circuit, when the MOS switches turn off, the current sources charge the voltages on the drains of M1 and M2 to ground and the positive supply, respectively. When the switches are turned on again charge sharing between the drain capacitances and the loop filter result in an error in the loop filter voltage, which is undesirable. Figure 2.6 (b) shows a circuit where the MOS switches are placed in the gates of the current mirror FETs. While this is an improvement compared to the circuit in Figure 2.6 (a), in the circuit shown in Figure 2.6 (b) the bias currents for M3 and M4 cannot be scaled down without increasing the switching time constant for this configuration. In addition, the gate capacitance of M3/M4 is substantial when the output current of the charge pump is high. Figure 2.6 (c) shows a circuit where the MOS 12 switches are placed in the sources of the current mirror FETs. Here the bias currents for M3/M4 do not affect the switching time constant so low bias currents can be used. We can also achieve faster switching times since each switch is connected to the source of a single transistor with lower parasitic capacitance. For more information on other charge pump architectures please refer to reference [2]. 13 Chapter 3 CHARGE PUMP DESIGN CONSIDERATIONS Charge pump phase-locked loops are remarkably good at accurate phase detection. As explained earlier, when the switches are off the charge pump stays in a high impedance mode and delivers no charge to the loop filter. Therefore, an ideal charge pump PLL provides infinite dc gain and achieves zero static phase error [2]. However, practical charge pump PLLs have mismatches in the charging and discharging of the loop filter. Because of mismatches between the source and sink currents in the charge pump the voltage on the loop filter does not stay constant even if the PLL is in a locked condition [6]. This along with other practical, non-ideal effects causes variations in the period of the VCO output clock, called jitter. The causes of this jitter depend on many non-ideal effects in the different building blocks in the phase-locked loop. The following section discusses the major non-ideal effects and practical design considerations for charge pumps, including : Dead zone Current and Switching Time Mismatch Charge Sharing 14 Dead Zone Sequential phase frequency detectors (PFD’s) have become very popular in phase-locked loops in recent years because of their excellent performance and low-cost [13]. PFD’s are implemented with simple digital logic circuits and typically have three possible states - up, down and off (neither up nor down). Which state is output depends upon the frequency and phase difference between the reference clock and the divided clock. For more information on sequential phase frequency detectors, please refer to reference [9]. Figure 3.1 PFD’s Output Narrow Up and Down Pulses for Zero Phase Difference [6] As shown in Figure 3.1, phase frequency detectors are designed to output two identical narrow width up and down pulses for zero phase difference between the reference clock and the divided clock. These signals turn on the charge pump for a specific amount of time. The width of these up and down pulses depends upon the delay of the reset signal in 15 the phase frequency detector. (For more information on design of the phase frequency detector please refer to the reference [3]). Figure 3.2 illustrates why these narrow width pulses are necessary for zero phase difference between the reference clock and the divided clock. Figure 3.2 Output Waveforms for the Phase Frequency Detector (PFD) [6] (a) Zero input phase difference (b) Small input phase difference The PFD would not output up pulses or down pulses for zero phase difference, as shown in Figure 3.2 (a). Then as shown in Figure 3.2 (b), when the phase difference between the reference clock and the divided clock begins to increase a very narrow up pulse would be generated. The ideal width of this pulse is shown as dashed lines in Figure 3.2 (b). But practically, these up and down signals take time to rise due to the capacitance at the input nodes of the charge pump switches. It is possible that these signals may never 16 reach a high enough voltage to turn on the charge pump switches. Thus, the charge pump would never respond to small phase differences between the reference clock and the divided clock, effectively breaking the feedback loop. As shown in Figure 3.3, for small phase differences the charge pump output current is zero. Therefore the gain of the PFD-charge pump combination would be zero for small phase differences between the reference clock and the divided clock, which would allow the VCO to run open loop, resulting in undesirable jitter. This is called a dead zone. Figure 3.3 Dead Zone in the Charge Pump Response [6] Having a dead zone allows the voltage-controlled oscillator to accumulate random phase error with respect to the input while receiving no corrective feedback. Thus, as 17 illustrated in Figure 3.4, the clock edges of the voltage-controlled oscillator output experience substantial random variations, or jitter [6]. Figure 3.4 Jitter Resulting from the Dead Zone [6] Current and Switching Time Mismatch Two additional important non-ideal effects for charge pumps are mismatches between the source and sink current sources and mismatches between the switching times of the Up and Down signals. Practically the current sources in the charge pump are implemented using transistors. As shown in Figure 3.5 the current sources are usually implemented using PMOS and NMOS FETs. In practice, the PMOS and the NMOS current sources provided by M1 and M2 and biased with Vb1 and Vb2 do not have the same value of current flowing through them, due to random device mismatches [11]. Even though the UPB and Down signals may be perfectly aligned in time, the mismatch in the current values will charge or discharge the loop filter even if the phase difference is zero. This change in the loop filter 18 voltage varies the frequency of the voltage-controlled oscillator even though no change was intended. Figure 3.5 Implementation of Current Sources using MOS Transistors [12] To understand the current mismatch effect, first we assume that the UPB and Down pulses are perfectly aligned in time for the case of zero phase difference, as shown in Figure 3.6. Due to mismatches in the source and sink current sources, the output 19 current of the charge pump is non-zero, even with zero phase difference. So the output current of the charge pump charges the loop filter capacitor increasing output voltage at each phase comparison even though PLL is in locked condition and no change was intended. In such a condition, the PLL will respond in such a way that it creates a small phase difference between the reference clock and the divided clock, so that the average output current of the charge pump is zero for every comparison. An equation which relates this phase offset to the current mismatch is given by [12], 3.1 Where ∆T = width of Ip pulse, Tclk = the clock period, ∆I = current mismatch, 20 Figure 3.6 Effect of Iup and Idw Current Mismatch [6] The second important non-ideal effect is the switching time mismatch between the UPB and Down pulses. The outputs of the phase-frequency detector are pump up and pump down signals, but these Up/Down signals are converted into Up, Upb and Down, 21 Downb signals as shown in Figure 2.5. The mismatch in the switching times for the Up/Upb and Down/Downb pulses will cause variations in the loop filter voltage even if the PLL is in a locked condition, as shown in Figure 3.7. This change in the loop filter voltage was unintended and results in undesirable jitter. For more information on design issues related to switching time mismatch, please refer to reference [3]. Figure 3.7 Effect of Switching Time Mismatch [6] 22 Charge Sharing The third major non-ideal problem in the design of a charge pump is charge sharing. As shown in Figure 3.8 charge sharing happens between the drain capacitors of the PMOS current source at node A, the NMOS current source at node B and the loop filter capacitor. As shown in Figure 3.8, when the Upb and Down switches are off nodes A and B are charged by the source and sink currents toward Vdd and Gnd, respectively. When the switches are turned on again the capacitance on node B takes charge from the loop filter capacitor to charge it to the loop filter voltage. Similarly, the capacitance on node A adds charge to the loop filter capacitor as the voltage on it is decreased from Vdd to Vcntrl, as shown in Figure 3.8 (b). To better understand this problem, let us assume that the UPB and Down signals are exactly aligned, as shown in Figure 3.8 (b). Also, to isolate this effect we will assume that there is no current mismatch between the PMOS and NMOS source and sink currents. Now, if the loop filter voltage is around half the supply voltage, then the voltage on node A increases to a high value near Vdd and the voltage on node B decreases to a small value near ground. These changes in the voltages on nodes A and B create error charges, which will charge or discharge the loop filter capacitor the next time these switches are turned on. This change in the loop filter voltage causes the voltage-controlled oscillator frequency to change even though the phase-locked loop is in a locked condition, leading to jitter. 23 (a) Figure 3.8 (a) Schematic Illustrating Charge Sharing between Nodes A, B and the Loop Filter Capacitor[12] 24 Figure 3.8 (b) Waveforms Illustrating Charge Sharing between Nodes A, B and the Loop Filter Capacitor[12] 25 Chapter 4 CHARGE PUMP DESIGN CALCULATIONS The design of the charge pump requires two major practical issues to be considered : 1. Current mismatch between Iup and Idw 2. Switching time mismatch between the Up/Upb and Dw/Dwb signals. Design Specifications A major requirement when designing a charge pump is to minimize the mismatch between the Iup and Idown current sources. In the selected architecture, the switches operate in the triode region. To minimize the charge injection error these switches are kept minimum sizes. The specifications for this charge pump are given in Table 4.1. Process Technology 0.5µm CMOS Supply Voltage (VDD) 5Volts Nominal charge pump Up /Down current (IUP and IDW) 100µAmp 3σ relative current mismatch between IUP and IDW currents < ±5% Output control voltage range (Vctrl) 1.1 to 2.7Volts Table 4.1 Design Specifications for the Charge Pump 26 Current Source Design As discussed earlier, practical current sources are implemented with MOS transistors. In this design, current sources were implemented using a wide swing cascode current mirror architecture. The output impedance of these cascode current mirrors is high, which is needed to reduce the variation of output current over the output voltage range. Figure 4.1 Wide-Swing Cascode Current Source used in Charge Pump 27 Figure 4.1 shows the wide swing cascode current source used in this design. The main current source devices are the M1 and M3 PMOS transistors, with M2 and M4 acting as the cascode devices. The specified charge pump current for this design was 100µA. The typical Von = Vgs – Vt for the current sources M1 and M3 and the cascode devices M2 and M4 were all chosen as 250mV. These values for Von were chosen based on the required output voltage swing for the charge pump. The main current source devices M1 and M3 need to match well to achieve the low variation specified for the source current. The random mismatch in the output current is given by equation (4.1) [9, 11]. From equation 4.1 it can be seen that the current varies inversely with the channel length L of the transistors. Because of that, the channel lengths for M1 and M3 were kept high. It can be shown that mismatches between the cascode FETs, M2 and M4, do not contribute much to the variation of the current, so the channel length for these cascode devices did not need to be as high. For more information about matching requirement for cascode devices please refer to [9]. Id Id The 2 VT A VT VGS VT L 2k ' Id (4.1) W ratio for all devices was calculated from the drain current using Equation 4.2, L C W I D n ox (VGS Vt )2 neglecting channel length modulation 2 L (4.2) 28 For the current source devices: C W 100 n ox (0.250)2 2 L W 103 L PMOS L was chosen as 3um, so W = 309um. For the cascode devices: C W 100 n ox (0.250)2 2 L W 103 L PMOS L was chosen as 0.6um, so W = 61.8um. Table 4.2 shows the sizes used for the current source and cascode FETs used in this PMOS wide swing cascode current mirror. The sizes for M7-M10 were based on the design of the NMOS current sink, which will be considered next. The size for the triode device, M5, was chosen to set the desired Vds across the main current source devices. Note that during simulations the values for Von were increased to maintain a minimum Von of 200 mV in the FF corner ( VDD= 5.5V, Temp = 00 C). 29 Sizes for the PMOS Hand Calculations Simulation Results wide swing cascode current source W L W L main devices ( M1 / M3 ) 309/3 273.6/3 cascode devices ( M2 / M4 ) 61.8/0.6 48/0.6 Table 4.2 Device Sizes for the PMOS Wide-Swing Cascode Current Source Current Sink Design Practical current sinks are implemented using NMOS transistors. As discussed earlier, variations in the output current of wide swing cascode current mirrors depend primarily on the channel length L of the main current source devices. Figure 4.2 shows the schematic of the NMOS wide-swing cascode current sink used in the charge pump. The channel lengths of the main current source devices M1 and M3 were kept high to minimize mismatches, as discussed previously for the PMOS current source. Also, since mismatches between the cascode devices do not contribute much to the variation of the output current, the channel lengths of the cascode devices were kept minimum. This both saves area and helps to minimize the drain capacitance on the output of the current sink. 30 Figure 4.2 Wide-Swing Cascode Current Sink used in Charge Pump The W ratio for the main current mirror devices was calculated using Equation 4.2 , L 100 nCox W 2 L (0.250) 2 Where, VON = 0.25V W 58 L NMOS L was chosen as 3 um, so W = 174um. 31 The W ratio for the cascode devices was calculated using Equation 4.2 , L 100 nCox W 2 L (0.250) 2 Where, VON = 0.25V W 58 L NMOS L was chosen as 0.6um, so W=34.8um. Table 4.3 shows the sizes used for the current source and cascode FETs used in this NMOS wide-swing cascode current mirror. The size for the triode device, M5, was chosen to set the desired Vds across the main current source devices. Note that during simulations the values for Von were increased to maintain a minimum Von of 200 mV in the FF corner (VDD= 5.5V, Temp = 00 C). Sizes for the NMOS Hand Calculations Simulation Results wide-swing cascode W L W L main devices ( M1 / M3 ) 174/3 120/3 cascode devices ( M2 / M4 ) 34.8/0.6 26.4/0.6 current sink Table 4.3 Device Sizes for NMOS Wide-Swing Cascode Current Sink 32 Unity Gain Buffer Design In this charge pump design a unity gain buffer is used to keep the voltage on both sides of the charge pump approximately equal. This helps to minimize charge sharing effects in the charge pump. Figure 4.3 Unity Gain Buffer The unity gain buffer was implemented using a two-stage op-amp architecture as shown in Figure 4.3. The input differential pair for this op-amp was designed using PMOS devices to achieve the required input common-mode range. With NMOS devices 33 the lowest input common-mode voltage possible in this process was found during simulations to be 1.3V. Since the charge pump output swing requirement is 1.1V-2.7V, a PMOS input differential pair was used instead. Another important design consideration for this op-amp is the current source and sink capability. As shown in Figure 2.4, when the charge pump is pumping up the output voltage the Upb switch is on and the loop filter capacitor is charging. In this condition the op-amp has to source current to the Idw current sink through the Dwb switch. Also, when the charge pump is pumping down the output voltage the op-amp has to sink the Iup current through the Up switch. To achieve this source and sink capability the op-amp bias current in the second stage was chosen to be greater than 200 uA. This allows the opamp to source or sink the required 100µA while diverting less than half of the normal bias current. The unity-gain bandwidth for the op-amp was chosen based on the loop bandwidth of the PLL, which is 1Mhz. The unity gain bandwidth for the two-stage op-amp is given by UGBW = Gm/Cc, where : (4.3) Gm = transconductance of the PMOS input devices Cc = compensation capacitor Since the loop bandwidth for the PLL was 1 MHz, the unity gain bandwidth for the op-amp needed to be at least 10-20 MHz to ensure the opamp was fast enough to track 34 variations in the loop filter voltage. In the worst corner ( SS ) the opamp unity gain bandwidth was set to 17 Mhz. Charge Pump Triode Switch Design In this charge pump the MOS switches operate in the triode region. Since the drains of the Upb and Dw switches are directly connected to the output node of the charge pump, any charge injected when they turn off will cause an error in the loop filter voltage. This charge injection will also cause undesirable jitter in the output of PLL. Therefore to minimize the effects of charge injection these switches need to be kept as small as possible. However, making these switches too small will increase the voltage drop across them, which in turn will reduce the output swing of the charge pump. These competing requirements had to be balanced when selecting the sizes for these switches. In this design the voltage drop across the switches was kept below 50 mV with 100 µA of current flowing through them. The equation for the on-resistance of a MOSFET operating in the triode region was used to calculate the W/L ratio for the switches, as follows : Ron 1/ ((W / L)* k '*(VGS Vt )) W 75 L n W n 45 m Where, L=0.6µm. (4.4) 35 Note that the NMOS and PMOS switches were kept the same size to match their charge injection. Switch Name Hand Calculations Width Wµm Length Lµm Simulation Results Width Wµm Length Lµm M_upb,M_up 45 0.6 40.2 0.6 M_dwb,M_dw 45 0.6 40.2 0.6 Table 4.4 Device Sizes for the Charge Pump Switches 36 Chapter 5 SIMULATIONS Charge Output Vs Phase Difference In this pre-layout simulation the linearity of the charge pump output versus the input phase difference was measured in terms of the amount of charge delivered to the loop filter capacitor. During this simulation a constant loop filter voltage of 2V was maintained. The results are shown in Figures 5.1 through 5.3. The X-axis shows the phase difference between the reference clock and the divided clock at the input of the phase-frequency detector. The Y-axis shows the amount of charge delivered to the loop filter capacitor. Figure 5.1 shows the simulation results for the TT corner (VDD= 5V, Temp = 500 C). Figure 5.2 shows the results for the SS corner (VDD=4.5V, Temp=850 C) and Figure 5.3 shows the results for the FF corner (VDD= 5.5V, Temp =00 C), respectively. Although small non-linearities are present, these results are acceptable in a closed-loop feedback system such as this PLL. These results also show that no dead zone exits in this charge pump, as will be discussed in more detail later in this chapter. 37 Figure 5.1 Charge Output in Pico-Columbs vs. Phase Difference in Degrees for the TT Corner Figure 5.2 Charge Output in Pico-Columbs vs. Phase Difference in Degrees for the SS Corner 38 Figure 5.3 Charge Output in Pico-Columbs vs. Phase Difference in Degrees for the FF Corner 39 Charge Output Vs Output Voltage In this pre-layout simulation the amount of charge delivered to the loop filter was measured as the output voltage was varied from 1.1V to 2.7V. A constant input phase difference of 8 degrees was maintanied between the reference clock and the divided clock, so the output charge should have been constant. The variations in output charge shown here were acceptably small thanks to the high output impedance of the charge pump. Figure 5.4 shows the results for the TT corner (VDD= 5V, Temp = 500 C ), Figure 5.5 shows the results for the SS corner (VDD= 4.5V, Temp = 850 C ) and Figure 5.6 shows the results for the FF corner (VDD= 5.5V, Temp = 00 C ), respectively. Figure 5.4 Variations in Output Charge over the Output Voltage Range(TT Corner) 40 Figure 5.5 Variations in Output Charge over the Output Voltage Range(SS Corner) Figure 5.6 Variations in Output Charge over the Output Voltage Range(FF Corner) 41 Dead Zone Ideally when the reference clock and divided clock are perfectly aligned in time the charge pump switches will still turn on for small amount of time to prevent a “dead zone”, where no corrective feedback is applied to the loop filter voltage as the input phase varies. This is typically accomplished by introducing a slight delay in the reset signal in the phase-frequency detector. In this design the delay was 200-300psec, depending on the corner. In this pre-layout simulation the phase difference between the reference clock and the divided clock was varied over a narrow range near zero degrees and the charge delivered to loop filter was measured, in order to test for a dead zone. With zero phase difference the switches do turn on as desired, but the charge injected by the identically sized PMOS and NMOS switches is different since their Vgs voltages are different. The result is a slight positive charge output, as shown in the following figures. Figure 5.7 shows the results for the TT corner (VDD= 5V, Temp = 500 C ), Figure 5.8 shows the results for the SS corner (VDD= 4.5V, Temp = 850 C ) and Figure 5.9 shows the results for the FF corner (VDD= 5.5V, Temp = 00 C ), respectively. 42 Figure 5.7 Charge Output with Zero Phase Difference Showing No Dead Zone Exists (TT corner) 43 Figure 5.8 Charge Output with Zero Phase Difference Showing No Dead Zone Exists (SS corner) Figure 5.9 Charge Output with Zero Phase Difference Showing No Dead Zone Exists (FF corner) 44 Post-Layout Simulations The simulations presented previously were repeated including back annotated parasitic from the layouts. The results are shown in following figures. Figure 5.10 Charge Output in Pico-Columbs vs. Phase Difference in Degrees Including Back-Annotated Layout Parasitics (TT corner) 45 Figure 5.11 Charge Output in Pico-Columbs vs. Phase Difference in Degrees Including Back-Annotated Layout Parasitics (SS corner) Figure 5.12 Charge Output in Pico-Columbs vs. Phase Difference in Degrees Including Back-Annotated Layout Parasitics (FF corner) 46 Figure 5.13 Variations in Output Charge over the Output Voltage Range Including Back-Annotated Layout Parasitics (TT corner) Figure 5.14 Variations in Output Charge over the Output Voltage Range Including Back-Annotated Layout Parasitics (SS corner) 47 Figure 5.15 Variations in Output Charge over the Output Voltage Range Including Back-Annotated Layout Parasitics (FF corner) Figure 5.16 Charge Output with Zero Phase Difference Including Back-Annotated Layout Parasitics Showing No Dead Zone Exists (TT corner ) 48 Figure 5.17 Charge Output with Zero Phase Difference Including Back-Annotated Layout Parasitics Showing No Dead Zone Exists (SS corner ) Figure 5.18 Charge Output with Zero Phase Difference Including Back-Annotated Layout Parasitics Showing No Dead Zone Exists (FF corner ) 49 Chapter 6 FLOORPLANNING AND LAYOUT Floorplanning of the Charge Pump Floorplanning is done before layout begins in order to plan the placement of the major circuit blocks in the overall chip or macro block layout. A major consideration in the floorplan is where the input and output pins need to connect. Another major concern was separating noisy digital signals such as UP and DW from sensitive analog signals such as Vout. Figure 6.1 shows the floorplan for the layout of this charge pump. The area allocated for the charge pump in this chip was 350µm×350µm. Also, each block in this charge pump was first cleared of all DRC and LVS errors, to ease assembly of the overall charge pump layout. Figure 6.1 Floorplan for the Charge Pump Layout 50 Layout of the Current Source Figure 6.2 shows the layout of the current source. Dummy devices were added near the main current source devices to achieve good neighborhood matching. Also to achieve good matching between the main current source devices standard analog layout techniques like interdigitation and common centroid layouts were used. For more information about the layout techniques used here, please refer to [9]. Figure 6.2 Layout of the Current Source 51 Layout of the Current Sink Figure 6.3 shows the layout of the current sink for the charge pump. To achieve good matching between the main current source devices good analog layout techniques such as the use of common centroid layouts and interdigitation were used. Dummy devices were also added to achieve good neighborhood matching. Figure 6.3 Layout of the Current Sink 52 Layout of the Unity Gain Buffer Figure 6.4 shows the layout of the unity gain buffer. The first stage of this unity gain buffer is a differential amplifier with an active load, which required particular care in the layout to achieve good matching and symmetry, and to avoid undesirable noise coupling. For more information about good layout techniques for core analog building blocks like this, please refer to [9]. Figure 6.4 Layout of the Unity Gain Buffer 53 Full Layout of the Charge Pump Figure 6.5 shows the full layout of the charge pump for this design, which required an overall area of 313µm×383µm. Figure 6.5 Full Layout of the Charge Pump 54 Chapter 7 CONCLUSION A charge pump has been successfully designed, simulated and laid out for a phase-locked loop integrated circuit in 0.5um CMOS. In this design current sources were implemented using wide-swing cascode current sources to achieve higher output impedance, thereby reducing errors in the charge supplied to the loop filter capacitor as the output voltage varies. A unity gain buffer was included to reduce errors due to charge sharing as the charge pump switches turn on and off. This charge pump was simulated across process, temperature and supply voltage variations including back-annotated layout parasitic capacitances, and meets all the required specifications. 55 REFERENCES [1] Gardner, F., "Charge-Pump Phase-Lock Loops", IEEE Trans. Communications, Vol. COM-28, Nov. 1980, pp. 1849-1858. [2] Woogeun Rhee, "Design of high-performance CMOS charge pumps in phaselocked loops", Proceedings of the 1999 IEEE International Symposium on Circuits and Systems, 1999, Volume 2, pp. 545-548. [3] Jwalant Ahir, “Design of a Phase Frequency Detector”, California State University, Sacramento, Project, Fall 2005. [4] Chad Beach, “Design of the Loop filter”, California State University, Sacramento, Project, Spring 2006. [5] Jan M. Rabaey, Anantha Chandrakansan and Borivoje Nikolic, “Digital Integrated Circuits”, Prentice-Hall, Second Edition, 2003. [6] Behzad Razavi, “Design of Analog CMOS integrated Circuits,” Tata McGrawHill, 2000. [7] Martin Ken and D. Johns, “Analog Integrated Circuit Design,” New York: McGraw-Hill, 2000. [8] Behzad Razavi, “RF Microelectronics,” Prientice-Hall, Inc., 1998. [9] Prof. Heedley Online lecture notes, http://gaia.ecs.csus.edu/~pheedley/ [10] Chad Beach website, http://gaia.ecs.csus.edu/~beachc [11] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, “Matching Properties of MOS Transistors,” IEEE Journal of Solid-State Circuits, vol. 24, pp. 1433-1440, 1989. [12] Niyut Patel, “Design of a Charge Pump for a Sonet OC-12, 622.04MHz, Phaselocked loop in 0.35µm CMOS”, California State University, Sacramento, Project, Spring 2006. [13] F. M. Gardner. Phase-lock Techniques, 2nd ed. New York: Wiley. 1979, ch. 6. 56 [14] F. M. Gardner, "Charge-'pump phase-lock loops,'' IEEE Trans. Commun., vol. COM-28. pp. 1849-1858. Nov. 1980.