Spectral Methods for Testing of Digital Circuits Doctoral Defense Nitin Yogi

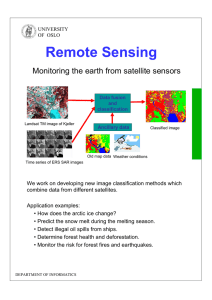

advertisement

Spectral Methods for Testing

of Digital Circuits

Doctoral Defense

Nitin Yogi

Dept. of ECE, Auburn University

Dissertation Committee:

Chair: Prof. Vishwani D. Agrawal

Prof. Victor P. Nelson

Prof. Adit D. Singh

Prof. Charles E. Stroud

Outside reader: Prof. Paul M. Swamidass

June 12, 2009

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

2

Manufacturing Test Challenges

NIST

Advances in

Microelectronic

Fabrication

Effects

• Decreasing feature sizes

• Increasing design complexities

Microchip Corp.

Manufacturing Test Issues

•

•

•

•

Increase in test generation complexity

More specific test patterns required

Higher number and more complex defects

Increase in test data volume

• Increase in test time

June 12, 2009

Nitin Yogi - Doctoral Defense

3

Primary Goals of this Work

1. Develop an efficient test generation algorithm

• High fault coverage

• Low test generation complexity

• Low number of test vectors

Issues addressed

Increase in

test generation

complexity

June 12, 2009

Increase in

test data volume

Nitin Yogi - Doctoral Defense

4

Primary Goals of this Work

2. Develop a minimization approach for

N-Model tests (multiple fault models)

• High test minimization capability

• Ability to handle diverse and custom fault models

Issues addressed

Increase in

test data volume

June 12, 2009

Higher number

& more complex

defects

Nitin Yogi - Doctoral Defense

5

Primary Goals of this Work

3. Develop a Built-In Self Test (BIST) synthesis

scheme

• High fault coverage

• Low area overhead

• Low test application time

Issues addressed

More specific

test patterns

required

June 12, 2009

Increase in

test time

Nitin Yogi - Doctoral Defense

6

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

7

Spectral Analysis Fundamentals

• Basic idea: Interpret information in frequency

domain

• Binary bit-streams converted to spectral

coefficients using transforms like Hadamard,

Haar, etc.

• Motivation: Good quality test vectors exhibit

certain discernible spectral characteristics

– Premise supported by findings of earlier works

June 12, 2009

Nitin Yogi - Doctoral Defense

8

Walsh Functions and Hadamard Matrix

w0

Walsh functions (order 3)

w1

w2

• Walsh functions: a complete

orthogonal set of basis functions

that can represent any arbitrary bitstream.

• Walsh functions form the rows of a

Hadamard matrix.

w3

w4

H(3) =

w5

w6

w7

1

1

1

1

1

1

1

1

1

-1

1

-1

1

-1

1

-1

1

1

-1

-1

1

1

-1

-1

1

-1

-1

1

1

-1

-1

1

1

1

1

1

-1

-1

-1

-1

1

-1

1

-1

-1

1

-1

1

1

1

-1

-1

-1

-1

1

1

1

-1

-1

1

-1

1

1

-1

Example of Hadamard

matrix of order 3

time

June 12, 2009

Nitin Yogi - Doctoral Defense

9

Test Vectors and Bit-streams

Outputs

June 12, 2009

Input 4

Input 5

1

0

0

1

0

.

.

0

0

1

0

0

1

.

.

1

1

0

1

0

1

.

.

1

0

1

1

0

0

.

.

1

Input J

Input 3

→

Input 2

Vector K

1

0

1

1

0

.

.

1

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Nitin Yogi - Doctoral Defense

1

1

0

1

0

.

.

0

A binary

bit-stream

Time

Vector 1 →

Vector 2 →

Vector 3 →

Vector 4 →

Vector 5 →

Input 1

Circuit Under Test (CUT)

10

1

0

1

0

0

0

1

0

1

0

1

1

1

1

0

0

0

0

0

1

1

1

0

1

0

1

1

1

0

1

0

1

1

0

1

0

1

.

1

0

1

.

.

Vector 1

Vector 2

Vector 3

.

.

.

Input 2

Test

vector set

Input 1

Spectral Analysis of a Bit-stream

Original

binary

bit-stream

Modified

bit-stream

1

0

1

1

-1

1

1

1

1

0

1

0

0 to -1

1

-1

1

-1

Bit-stream of

Input 2

June 12, 2009

Nitin Yogi - Doctoral Defense

11

Spectral Analysis of a Bit-stream (cont.)

Bit stream

to analyze

1

-1

1

1

1

-1

1

-1

Hadamard Matrix H(3)

1

1

1

1

1

1

1

1

1

-1

1

-1

1

-1

1

-1

1

1

-1

-1

1

1

-1

-1

1

-1

-1

1

1

-1

-1

1

1

1

1

1

-1

-1

-1

-1

1

-1

1

-1

-1

1

-1

1

1

1

-1

-1

-1

-1

1

1

Bit

stream

Spectral

coeffs.

1

-1

1

1

1

-1

1

-1

2

6

-2

2

2

-2

-2

2

1

-1

-1

1

-1

1

1

-1

Correlating with Walsh

functions by multiplying with

Hadamard matrix.

June 12, 2009

Nitin Yogi - Doctoral Defense

=

Prominent

spectral

component

12

Power Spectrum: “Interrupt” Signal*

Normalized Power

Examples of

essential

components

Examples of

noise

components

Theoretical

random noise

level (1/128)

Spectral Coefficients

* A primary input signal for PARWAN processor

June 12, 2009

Nitin Yogi - Doctoral Defense

13

Normalized Power

Power Spectrum: “DataIn[5]” Signal

Examples of

essential

components

Examples of

noise

components

Theoretical

random noise

level (1/128)

Spectral Coefficients

* A primary input signal for PARWAN processor

June 12, 2009

Nitin Yogi - Doctoral Defense

14

Normalized Power

Power Spectrum: Random Signal

Theoretical

random noise

level (1/128)

Spectral Coefficients

June 12, 2009

Nitin Yogi - Doctoral Defense

15

Reverse Hadamard Transform

Spectral

coeffs.

Hadamard Matrix H(3)

1

1

1

1

1

1

1

1

1

-1

1

-1

1

-1

1

-1

1

1

-1

-1

1

1

-1

-1

June 12, 2009

1

-1

-1

1

1

-1

-1

1

1

1

1

1

-1

-1

-1

-1

1

-1

1

-1

-1

1

-1

1

1

1

-1

-1

-1

-1

1

1

1

-1

-1

1

-1

1

1

-1

2

6

-2

2

2

-2

-2

2

Original

binary

bit-stream

Bit-stream

÷8 =

1

-1

1

1

1

-1

1

-1

Nitin Yogi - Doctoral Defense

-1 to 0

1

0

1

1

1

0

1

0

16

Spectral Vector Generation

Hadamard Matrix H(3)

sign

1

1

1

1

1

1

1

1

1

-1

1

-1

1

-1

1

-1

1

1

-1

-1

1

1

-1

-1

1

-1

-1

1

1

-1

-1

1

1

1

1

1

-1

-1

-1

-1

1

-1

1

-1

-1

1

-1

1

1

1

-1

-1

-1

-1

1

1

1

-1

-1

1

-1

1

1

-1

Perturbed

spectral

coeffs.

Bit-stream

1

6

2

-1

3

-2

3

-1

1

1

1

-1

1

-1

1

-1

÷8

=

New binary

bit-stream

-1 to 0

1

1

1

0

1

0

1

0

Bits changed

June 12, 2009

Nitin Yogi - Doctoral Defense

17

Effect of Noise

Effect of noise

No. of faults

detected by

original vectors

Frequency

0.04

0.03

ST = 0

0.02

ST = 1

ST = 5

0.01

ST = 9

0

3100

3150

3200

3250

3300

3350

Number of faults detected

•

3400

More faults

detected than

original vectors

Noise inserted in ATPG vectors using increasing spectral threshold (ST)

values (i.e. increasing noise)

June 12, 2009

Nitin Yogi - Doctoral Defense

18

Significance of spectral properties

Mean number of detected faults

Number of faults

3350

3250

Spectral

noise

3150

3050

Random

noise

2950

2850

2750

2650

0

•

10

20

Spectral threshold

30

40

Two types of test vectors generated

– Spectrally inserted noise by eliminating spectral coefficients below a threshold

– Randomly inserted noise by flipping proportion of bits randomly

June 12, 2009

Nitin Yogi - Doctoral Defense

19

Significance of spectral properties

Number of faults

Std. dev. of detected faults

90

80

70

60

50

Spectral

noise

40

30

20

10

0

Random

noise

0

June 12, 2009

10

20

Spectral threshold

30

Nitin Yogi - Doctoral Defense

40

20

Significance of spectral properties

Tests generated with ST=1 & ST=13 (3 sets for each)

Distribution of number of detected faults (250 samples)

0.03

Frequency

0.025

Spectral

noise

0.02

Random

noise

0.015

0.01

0.005

0

3540

3560

3580

3600

3620

3640

3660

Number of detected faults

•

T-test results

–

–

h=1

(hypothesis that the two data sets have

equal means is rejected)

p = 8.85 x 10-18

(probability with which both data sets

will have equal values is low)

June 12, 2009

Spectral noise

Random noise

Mean

3615.04

3598.52

Std. dev.

14.20

19.24

Nitin Yogi - Doctoral Defense

21

Significance of spectral properties

Tests generated with ST=1, ST=13 & ST=25 (3 sets for each)

Distribution of number of detected faults (500 samples)

Frequency

0.035

0.03

0.025

Spectral

noise

0.02

0.015

Random

noise

0.01

0.005

0

3525

3575

3625

3675

Number of detected faults

•

T-test results

–

–

h=1

(hypothesis that the two data sets have

equal means is rejected)

p = 1.54 x 10-78

(probability with which both data sets

will have equal values is low)

June 12, 2009

Spectral noise

Random noise

Mean

3625.87

3602.99

Std. dev.

12.34

18.76

Nitin Yogi - Doctoral Defense

22

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

23

Spectral RTL Test Generation

• We propose a novel test generation

algorithm using:

– Register Transfer Level (RTL) information

– Spectral techniques

• Primary goals:

– Low test generation complexity

– High fault coverage

– Low test vector length

June 12, 2009

Nitin Yogi - Doctoral Defense

24

Faults Modeled for an RTL Module

Inputs

Combinational

Logic

RTL

stuck-at

fault

sites

Outputs

FF

FF

A circuit is an interconnect of several RTL modules.

June 12, 2009

Nitin Yogi - Doctoral Defense

25

Proposed Test Generation Algorithm

RTL

circuit

Step 1

Generate test vectors

for RTL faults

Determine

prominent spectral

components by

spectral analysis

Spectral properties

Step 2

Generate new test

vectors by spectral

coeff. perturbation

Fault simulate test

vectors and compact

0100101001001011

1011100010011011

1101011101010011

1110000101110001

0001010110101101

1000001011010101

Test vector

set

June 12, 2009

Nitin Yogi - Doctoral Defense

26

Results for ITC’99 and ISCAS’89 Circuits

Circuit

name

No. of

gatelevel

faults

b01-A

RTL-ATPG spectral tests

FlexTest Gate-level ATPG

Random tests

Cov.

(%)

No. of

vectors

CPU

(secs)

Cov.

(%)

No. of

vectors

CPU

(secs)

No. of

vectors

Cov

(%)

228

99.57

128

19

99.77

75

1

640

97.78

b01-D

290

98.77

128

19

99.77

91

1

640

95.80

b09-A

882

84.68

640

730

84.56

436

384

3840

11.71

b09-D

1048

84.21

768

815

78.82

555

575

7680

6.09

b11-A

2380

88.84

768

737

84.62

468

1866

3840

45.29

b11-D

3070

89.25

1024

987

86.16

365

3076

3840

41.42

b14

25894

85.09

6656

5436

68.78

500

6574

12800

74.61

s1488

4184

95.65

512

103

98.42

470

131

1600

67.47

s5378

15584

76.49

2432

2088

76.79

835

4439

3840

67.10

s5378*

15944

73.59

1399

718

73.31

332

22567

2880

62.77

s9234

28976

17.36

64

721

20.14

6967

18241

160

15.44

s9234*

29400

49.47

832

2734

48.74

12365

4119

2176

33.06

s35932

103204

95.70

256

1801

95.99

744

3192

320

50.70

* Reset input added.

N. Yogi and V. D. Agrawal, “Spectral RTL Test Generation for Gate-Level Stuck-at Faults,” in Proc. 15th IEEE Asian

Test Symp., 2006, pp. 83–88.

June 12, 2009

Nitin Yogi - Doctoral Defense

27

Results for PARWAN Processor

RTL Spectral ATPG*

Gate-level ATPG*

(FlexTest)

Random vecs.

Circuit

Cov. (%)

No. of

vecs.

CPU

(secs)

Cov. (%)

No. of

vecs.

CPU

(secs)

Cov. (%)

No. of

vecs.

Parwan

98.23%

2327

2442

93.40%

1403

26430

80.95%

2814

Parwan

(with DFT)

98.77%

1966

2442

95.78%

1619

20408

87.09%

2948

*Sun Ultra 5, 256MB RAM

N. Yogi and V. D. Agrawal, “Spectral RTL Test Generation for Microprocessors,” in Proc. 20 th International Conf. VLSI

Design, Jan. 2007, pp. 473–478.

June 12, 2009

Nitin Yogi - Doctoral Defense

28

Test Coverage Distribution

Test coverage distribution

for PARWAN processor (500 samples)

160

140

Spectral

ATPG

Frequency

120

Commercial

ATPG

100

80

60

40

20

99.5

99

98.5

98

97.5

97

96.5

96

95.5

95

94.5

94

93.5

93

0

Test Coverage

June 12, 2009

Nitin Yogi - Doctoral Defense

29

Test Coverage Distribution

Test coverage distribution

for b11-area circuit (500 samples)

160

140

Spectral

ATPG

Frequency

120

100

Commercial

ATPG

80

60

40

20

92.5

92

91.5

91

90.5

90

89.5

89

88.5

88

87.5

87

86.5

86

85.5

85

84.5

84

0

Test coverage

June 12, 2009

Nitin Yogi - Doctoral Defense

30

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

31

Multiple Fault Models

• N-Model tests: For a set of N given fault models, N ≥ 1,

the N-model tests target detection of all faults in the

superset of faults for all N fault models.

• Importance

– Each fault model targets specific defects

• Sematech study (Nigh et. al. VTS’97) concluded …

To detect most defects, tests for all fault models need to included.

• Minimization problem

– Obtain minimized test set for considered fault models

• Take advantage of vectors detecting faults in multiple fault models

– Fault simulator/ATPG handles only one fault model at a time

• Need for a new minimization approach

June 12, 2009

Nitin Yogi - Doctoral Defense

32

Multiple Fault Model Test Minimization

• Obtain fault dictionary by fault simulations

– Determine faults detected by each vector

• ‘F’ faults : for all considered fault models

• ‘N’ vectors : generated to cover all faults ‘F’

• Test minimization by Integer Linear Program (ILP)

considering the test application cost

– ILP formulation

• Set of integer variables

• Set of constraints

• Objective function

– Solving the ILP assigns values to variables such that:

• Constraints are met

• Objective function is optimum

June 12, 2009

Nitin Yogi - Doctoral Defense

33

Combined ILP

• Define two [0, 1] integer variables:

– { tj , ij } – for each vector ; j = 1 to N

•

•

•

•

June 12, 2009

tj = 0 : drop vector j

tj = 1 : select vector j

ij = 0 : no IDDQ measurement for vector j

ij = 1 : measure IDDQ for vector j

Nitin Yogi - Doctoral Defense

34

Combined ILP (cont.)

• Constraints {ck} for kth fault, k = 1 to F

– For kth fault detected by vectors u, v and w

c k : tu + tv + tw ≥ 1

iu + iv + iw ≥ 1

tu ≥ iu

tv ≥ iv

tw ≥ i w

June 12, 2009

Only if kth fault

is an IDDQ fault

Nitin Yogi - Doctoral Defense

35

Combined ILP (cont.)

• Objective function

– Minimize

N

N

j=1

j=1

{ ∑ tj + W × ∑ ij }

• N : total number of vectors

• tj : variables to select vectors

• ij : variables to select IDDQ measurements

• W : weighting factor, W ≥ 0

– How strongly to minimize IDDQ vectors

(May depend on the relative cost of current

measurement)

June 12, 2009

Nitin Yogi - Doctoral Defense

36

Hybrid LP – ILP

• Approximate solution to ILP

• Algorithm:

1. All variables redefined as real [0,1] variables (LP

model)

2. Loop :

a. Solve LP

b. Round variables {tj} , {ij} as follows:

1. Round to 0 if ( 0.0 < variables ≤ 0.1)

2. Round to 1 if ( 0.9 ≤ variables < 1.0)

c. Exit loop if no variables are rounded

3. Reconvert variables to [0,1] integers & solve ILP

June 12, 2009

Nitin Yogi - Doctoral Defense

37

Conventional Test Vector Minimization

Mentor Fastscan vectors

Un-minimized

Minimized

Fault

Cov. (%)

Stuck-at

167

130

96.00

IDDQ(pseudo stuck-at)

53

45

99.09

Transition delay

299

229

96.55

Total

519

404

-

Stuck-at

150

145

99.30

IDDQ(pseudo stuck-at)

71

70

85.75

s5378 Transition delay (LOS)

319

293

98.31

Transition delay (LOC)

256

242

90.05

Total

796

750

-

Circuit

c3540

Type of vecs

June 12, 2009

Nitin Yogi - Doctoral Defense

38

Results: N-Model Test Minimization

Conventional test minimization results: Ckt

No. of vecs. & IDDQ meas.

c3540

Vecs: 404

IDDQ: 45

s5378

Vecs: 750

IDDQ: 70

N-Model test minimization results:

Combined ILP model

Ckt.

c3540

s5378

No. of

vecs.

& IDDQ

meas.

Hybrid LP – ILP solution

ILP solution

W = 0.1

Vecs

/ IDDQ

Vecs

225

IDDQ

40

Vecs

320

IDDQ

78

CPU$

(s.)

5044*

2314

W=1

Vecs

/ IDDQ

226

41

326

73

W = 10

CPU$

(s.)

5047*

5154*

Vecs

/ IDDQ

247

37

353

64

CPU$

(s.)

5047*

5161*

W = 0.1

Vecs

/ IDDQ

225

41

320

80

CPU$

(s.)

167

529

W=1

Vecs

/ IDDQ

226

39

326

72

CPU$

(s.)

189

617

W = 10

Vecs

/ IDDQ

CPU$

(s.)

248

516

34

353

793

63

* CPU time limit of 5000 s exceeded

SUN Sparc Ultra 10, four CPU machine with 4.0 GB RAM shared among 4 CPUs

$

Order of magnitude

N. Yogi and V. D. Agrawal, “N-Model Tests for VLSI Circuits,” in Proc. 40th IEEE South-eastern Symp. System Theory,

reduction in CPU time

Mar. 2008, pp. 242–246.

June 12, 2009

Nitin Yogi - Doctoral Defense

39

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

40

Spectral TPG for BIST

• We propose a novel design methodology

for a Test Pattern Generator (TPG) for

Built-In Self Test (BIST) environments

• Primary goals:

– Given pre-generated test vectors, replicate

their effects in hardware

– Support at-speed testing for non-scan circuits

– Low area overhead

– Low test application times

June 12, 2009

Nitin Yogi - Doctoral Defense

41

Proposed Design Methodology

Pre-generated

test vectors

Step 1

Spectral properties

Step 2

Preprocess test

vectors

(for combinational

circuits)

Determine

prominent spectral

components by

spectral analysis

June 12, 2009

BIST

implementation

BIST TPG

gate-level

netlist

Nitin Yogi - Doctoral Defense

42

Pre-processing of Test Vectors

• Pre-processing of test vectors convenient

for combinational circuits

– Order of application of test vectors is

immaterial

• Method employed

– Reshuffling of test vectors to enhance the

spectral properties

June 12, 2009

Nitin Yogi - Doctoral Defense

43

Reshuffling Algorithm

Input Data and Parameters:

NI: No of inputs

NV: No. of vectors

V(1:NV,1:NI): Test vector Set of dimensions NV x NI

hd: Dimension of Hadamard matrix

H: Hadamard transform matrix of dimension 2hd x 2hd

Procedure:

Vector set V appended with redundant vectors to make weighting

of bit-streams of all inputs = 0.5

for i=1 to NI

Perform spectral analysis on bit-stream of input i: S = V(:,i) x H;

Pick the prominent spectral component Sp(i) from S

Rearrange vector set V such that maximum bits in the

bit-streams of inputs 1 to i match with the picked prominent

spectral components Sp(1 to i) respectively.

end

June 12, 2009

Nitin Yogi - Doctoral Defense

44

Spectral TPG Architecture

System

clock

To

CUT

Clock divider and holding circuit (for sequential CUTs)

BIST

clock

Hadamard

wave generator

Weighted pseudo-random

pattern generator

2

System clock

3

BIST clock

1

Hadamard

Components

1

Input 1

Input 2

Randomizer

1

Weighted

pseudo-random

bit-streams

June 12, 2009

Spectral

component

synthesizer

Nitin Yogi - Doctoral Defense

To

CUT

Input 3

45

Reseeding

• Reseeding: Setting memory elements (flip-flops)

of TPG to values such that fault detection

capability of generated test vectors improves.

• Reseeding effectively used in earlier works for

LFSRs, CARs, etc.

June 12, 2009

Nitin Yogi - Doctoral Defense

46

Reseeding of Spectral TPG

Flip-flops

Data from

external

tester

Parallel interface

Spectral BIST /

Decompressor

BIST /

Decompressor

Logic

To

CUT

Serial

scan

interface

Mode of operation

Function

External Tester Mode (ETM)

One-seed-per-test vector operation

Hybrid BIST Mode (HBM)

Used to generate test vectors and reseed the flip-flops occasionally

June 12, 2009

Nitin Yogi - Doctoral Defense

47

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Results without reseeding

– Results for combinational circuits

– Results for sequential circuits

• Results with reseeding

– Results for combinational circuits

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

48

Spectral BIST Results and Area Overhead

Test coverage comparison (64000 vectors)

Circuit

Random

vectors

Weighted

Random

vectors

Spectral BIST

ATPG Coverage

(No. of vecs)

c7552

97.41%

97.86%

99.81%

100% (247)

s15850

(combinational)

96.81%

97.41%

98.77%

100% (530)

Area overhead comparison

Spectral BIST

PRPG

Circuit

No. of gates

in circuit

No. of gates

% Area

overhead

No. of gates

% Area

overhead

c7552

3513

976

27.78

830

23.63

s15850

(combinational)

9772

2672

27.34

2400

24.56

N. Yogi and V. D. Agrawal, “BIST/Test-Decompressor Design using Combinational Test Spectrum,” in Proc. 13th VLSI

Design and Test Symp., Aug. 2009.

June 12, 2009

Nitin Yogi - Doctoral Defense

49

Test Coverage vs Number of Vectors

c7552

100

Spectral

BIST

Test coverage

99

98

97

Weighted

Random

96

95

94

Random

93

0

10000

20000

30000

40000

50000

60000

Test vectors

June 12, 2009

Nitin Yogi - Doctoral Defense

50

Test Coverage vs Number of Vectors

s15850

100

Spectral

BIST

98

Test coverage

96

94

Weighted

Random

92

90

Random

88

86

0

10000

20000

30000

40000

50000

60000

Test vectors

June 12, 2009

Nitin Yogi - Doctoral Defense

51

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Results without reseeding

– Results for combinational circuits

– Results for sequential circuits

• Results with reseeding

– Results for combinational circuits

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

52

Hadamard BIST Results

Number of faults detected

Circuit

Total

No. of

faults

Flex

Test

ATPG

64k

random

vectors

64k

weighted

random

vectors

Hadamard

Haar

BIST (64k BIST1 (64k

vectors)

vectors)

s298

308

273

273

273

273

273

s820

850

793

449

764

777

710

s1423

1515

1443

1217

1469

1468

1468

s1488

1486

1446

1369

1443

1443

1441

s5378

4603

3547

3424

3537

3603

3609

s9234

6927

1588

1305

1303

1729

1413

s15850

13863

7323

6270

6696

6844

5888

s38417

31180

15472

4185

4949

17020

4244

Equal or more faults

1. S. K. Devanathan and M. L. Bushnell, “Test Pattern Generation Using Modulation by Haar Wavelets and Correlation for Sequential BIST,” in

detected than ATPG in

Proc. 20th International Conf. VLSI Design, 2007, pp. 485–491.

5 / 8 circuits

N. Yogi and V. D. Agrawal (2008), “Sequential Circuit BIST Synthesis Using Spectrum and Noise from ATPG Patterns,”

Proc. 27th IEEE Asian Test Symp., pp. 69-74.

June 12, 2009

Nitin Yogi - Doctoral Defense

53

Hadamard BIST Results

Number of faults detected

Circuit

Total

No. of

faults

Flex

Test

ATPG

64k

random

vectors

64k

weighted

random

vectors

Hadamard

Haar

BIST (64k BIST1 (64k

vectors)

vectors)

s298

308

273

273

273

273

273

s820

850

793

449

764

777

710

s1423

1515

1443

1217

1469

1468

1468

s1488

1486

1446

1369

1443

1443

1441

s5378

4603

3547

3424

3537

3603

3609

s9234

6927

1588

1305

1303

1729

1413

s15850

13863

7323

6270

6696

6844

5888

s38417

31180

15472

4185

4949

17020

4244

1. S. K. Devanathan and M. L. Bushnell, “Test Pattern Generation Using Modulation by Haar Wavelets

and Correlation

Maximum

faults for Sequential BIST,” in

Proc. 20th International Conf. VLSI Design, 2007, pp. 485–491.

detected in

6 / 8 circuits

N. Yogi and V. D. Agrawal (2008), “Sequential Circuit BIST Synthesis Using Spectrum

and Noise from ATPG Patterns,”

Proc. 27th IEEE Asian Test Symp., pp. 69-74.

June 12, 2009

Nitin Yogi - Doctoral Defense

54

Longer BIST Sequences

FlexTest

Circuit

Fault

coverage

(%)

Hadamard BIST

No. of

vectors

Fault

coverage

(%) at 64K

vectors

Fault

coverage

(%) at 128K

vectors

BIST vecs.

for FlexTest

ATPG cov.

s298

88.64

153

88.64

88.64

757

s820

93.29

1127

91.41

91.88

(!)

s1423

95.25

3882

96.90

96.90

22345

s1488

97.31

736

97.11

97.11

(!)

s5378

77.06

739

78.27

78.67

8984

s9234

22.92

15528

24.96

25.25

8835

s15850

52.82

61687

49.37

52.15

198061

s38417

49.62

55110

54.59

63.07

43240

ATPG fault coverage

in 6 ATPG

/ 8 circuits

N. Yogi and V. D. Agrawal (2008), “Sequential Circuit BIST Synthesis Using Spectrum achieved

and Noise from

Patterns,”

Proc. 27th IEEE Asian Test Symp., pp. 69-74.

June 12, 2009

Nitin Yogi - Doctoral Defense

55

Area Overhead

Circuit

No. of

transistors

in circuit

Haar BIST1

Hadamard BIST

No. of

transistors

% Area

overhead

No. of

transistors

% Area

overhead

s298

890

908

102.02

834

93.71

s820

1896

1472

77.64

1612

85.02

s1423

4624

1637

35.40

1555

33.63

s1488

4006

1069

26.68

1078

26.91

s5378

12840

2342

18.24

2487

19.37

s9234

23356

2700

11.56

2552

10.93

s15850

43696

4908

11.23

4595

10.52

s38417

108808

3606

3.31

2135

1.96

Approximately

1. S. K. Devanathan and M. L. Bushnell, “Test Pattern Generation Using Modulation

by Haar Wavelets and Correlation for

similar area overheads

Sequential BIST,” in Proc. 20th International Conf. VLSI Design, 2007, pp. 485–491.

N. Yogi and V. D. Agrawal (2008), “Sequential Circuit BIST Synthesis Using Spectrum and Noise from ATPG Patterns,”

Proc. 27th IEEE Asian Test Symp., pp. 69-74.

June 12, 2009

Nitin Yogi - Doctoral Defense

56

Outline

• Test challenges & primary goals of this work

• Spectral analysis fundamentals

• Contributions of this thesis

Spectral RTL Test generation

Minimization of N-model tests

Spectral TPG for BIST

• Results without reseeding

– Results for combinational circuits

– Results for sequential circuits

• Results with reseeding

– Results for combinational circuits

• Conclusion

June 12, 2009

Nitin Yogi - Doctoral Defense

57

Spectral TPG Results with Reseeding

Comparison of test data volume and test time for c7552

No. of

inputs

Test

data

volume

(bits)

No. of

tester

cycles

No. of

system

clock

cycles

Test

time

(us)†

247

207

51129

247

0

2

247

1

51129

51129

0

511

ETM (parallel)

197

30

5910

197

0

2

ETM (serial)

197

1

5910

5910

0

59

HBM (parallel)

33

30

990

33

8034

8

HBM (serial)

33

1

990

990

8034

18

Mode of test application

No. of

vecs./

seeds

Conventional (parallel)

Conventional (serial)

Spectral

BIST

† assuming tester clock period Ttester=10ns and on-chip system clock period Tclk=1ns

N. Yogi and V. D. Agrawal, “BIST/Test-Decompressor Design using Combinational Test Spectrum,” in Proc. 13th VLSI

Design and Test Symp., Aug. 2009.

June 12, 2009

Nitin Yogi - Doctoral Defense

58

Spectral TPG Results with Reseeding

Comparison of test data volume and test time for s15850 (combinational)

No. of

inputs

Test

data

volume

(bits)

No. of

tester

cycles

No. of

system

clock

cycles

Test

time

(us)†

530

600

318000

530

0

5

530

1

318000

318000

0

3180

ETM (parallel)

455

35

15925

455

0

5

ETM (serial)

455

1

15925

15925

0

159

HBM (parallel)

134

35

4690

134

20129

21

HBM (serial)

134

1

4690

4690

20129

67

Mode of test application

No. of

vecs./

seeds

Conventional (parallel)

Conventional (serial)

Spectral

BIST

† assuming tester clock period Ttester=10ns and on-chip system clock period Tclk=1ns

N. Yogi and V. D. Agrawal, “BIST/Test-Decompressor Design using Combinational Test Spectrum,” in Proc. 13th VLSI

Design and Test Symp., Aug. 2009.

June 12, 2009

Nitin Yogi - Doctoral Defense

59

Conclusion

• Proposed methods using spectral techniques for

– Test generation using RTL information

– Designing a TPG for BIST

• Proposed Spectral RTL test generation

– Generated test vectors exhibited:

• High fault coverage for most circuits

• Low test generation complexity

• Moderate number of test vectors

• N-model test defined

– Proposed an ILP-based minimization approach with high compression ratio

• Proposed design methodology for TPG in BIST

– Generated test vectors in hardware exhibited:

•

•

•

•

Equal or higher fault coverage that ATPG vectors in most circuits

Higher fault coverage then existing TPGs in most circuits

Moderate area overhead compared to existing TPGs

High test compression capabilities

June 12, 2009

Nitin Yogi - Doctoral Defense

60

List of Publications

•

N. Yogi and V. D. Agrawal, “BIST/Test-Decompressor Design using Combinational

Test Spectrum,” in Proc. 13th VLSI Design and Test Symp., Aug. 2009.

•

N. Yogi and V. D. Agrawal, “Sequential Circuit BIST Synthesis using Spectrum and

Noise from ATPG Patterns,” 17th Asian Test Symposium, Nov. 2008

•

N. Yogi and V. D. Agrawal, “N-Model tests for VLSI circuits,” 40th Southeastern

Symposium on System Theory, March 2008

•

N. Yogi and V. D. Agrawal, “Transition Delay Fault Testing of Microprocessors by

Spectral Method,” in Proc. 39th IEEE Southeastern Symp. System Theory, Mar.

2007, pp. 283–287.

•

N. Yogi and V. D. Agrawal, “Spectral RTL Test Generation for Microprocessors,”

20th Int’l Conf. on VLSI Design, Jan. 2007

•

N. Yogi and V. D. Agrawal, “Spectral RTL Test Generation for Gate-Level Stuck-at

Faults,” 15th Asian Test Symp., Nov. 2006

•

N. Yogi and V. D. Agrawal, “Spectral Characterization of Functional Vectors for

Gate-Level Fault Coverage Tests," in Proc. 9th VLSI Design and Test Symp., Aug.

2006

June 12, 2009

Nitin Yogi - Doctoral Defense

61

Thank you.

Questions?

June 12, 2009

Nitin Yogi - Doctoral Defense

62