Lecture 1: Introduction VLSI Testing Dr. Vishwani D. Agrawal

advertisement

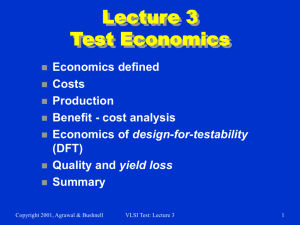

VLSI Testing Lecture 1: Introduction Dr. Vishwani D. Agrawal James J. Danaher Professor of Electrical and Computer Engineering Auburn University, Alabama 36849, USA vagrawal@eng.auburn.edu http://www.eng.auburn.edu/~vagrawal IIT Delhi, July 24, 2012, 3:00-4:00PM Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 1 Course Description This course is designed for the MTech program in VLSI at IIT, Delhi. It is patterned after a onesemester graduate-level course offered at Auburn University. A set of 17 lectures that include classroom exercises provide understanding of theoretical and practical aspects of VLSI testing. The course fulfills the needs of today’s industrial design environment, which demands knowledge of testing concepts of digital, memory, analog and radio frequency (RF) subsystems often implemented on a system-on-chip (SoC). Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 2 Outline Lecture 1: Lecture 2: Lecture 3: Lecture 4: Lecture 5: Lecture 6: Lecture 7: Lecture 8: Lecture 9: Lecture 10: Lecture 11: Lecture 12: Lecture 13: Lecture 14: Lecture 15: Lecture 16: Lecture 17: Introduction (19*+1) * Number of slides Yield and quality (17+2) Fault modeling (20+2) Testability analysis (27) Logic simulation (15) Fault simulation (19) Combinational ATPG (24+3) Sequential ATPG (19+2) Delay test (26) Memory test (26) Analog test (27) Model-Based and Alternate Test (15) DFT and Scan (23+2) BIST (29) System diagnosis (21) RF Testing: Introduction, gain measurement (39) RF Testing: Intermodulation and noise measurements (34) Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 3 Schedule July 24, 2012 – 3-5PM Lectures 1 and 2 July 24, 2012 – Homework 1 assigned, due July 26 July 25, 2012 – 3-5PM Lectures 3 and 4 July 26, 2012 – 3-5PM Lectures 5 and 6 July 27, 2012 – 3-5PM Lectures 7 and 8 July 28, 2012 – 8-10AM Lectures 9 and 10 July 30, 2012 – 3-5PM Lectures 11 and 12 July 30, 2012 – Homework 2 assigned, due Aug 1 July 31, 2012 – 3-5PM Lectures 13 and 14 Aug 1, 2012 – 3-5PM Lectures 15 and 16 Aug 1, 2012 – Take-Home Exam assigned Aug 3, 2012 – 3-4PM Lectures 17 Aug 3, 2012 –Take-Home Exam due 5PM Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 4 Introduction VLSI realization process Verification and test Ideal and real tests Costs of testing Roles of testing A modern VLSI device - system-on-a-chip Testing Digital Memory Analog RF Textbook Problem to solve Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 5 VLSI Realization Process Customer’s need Determine requirements Write specifications Design synthesis and Verification Test development Fabrication Manufacturing test Chips to customer Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 6 Definitions Design synthesis: Given an I/O function, develop a procedure to manufacture a device using known materials and processes. Verification: Predictive analysis to ensure that the synthesized design, when manufactured, will perform the given I/O function. Test: A manufacturing step that ensures that the physical device, manufactured from the synthesized design, has no manufacturing defect. Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 7 Verification vs. Test Verification Test Verifies correctness of design. Performed by simulation, hardware emulation, or formal methods. Performed once prior to manufacturing. Responsible for quality of design. Copyright 2001, Agrawal & Bushnell Verifies correctness of manufactured hardware. Two-part process: 1. Test generation: software process executed once during design 2. Test application: electrical tests applied to hardware Test application performed on every manufactured device. Responsible for quality of devices. Lecture 1 Introduction 8 Problems of Ideal Tests Ideal tests detect all defects produced in the manufacturing process. Ideal tests pass all functionally good devices. Very large numbers and varieties of possible defects need to be tested. Difficult to generate tests for some real defects. Defect-oriented testing is an open problem. Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 9 Real Tests Based on analyzable fault models, which may not map on real defects. Incomplete coverage of modeled faults due to high complexity. Some good chips are rejected. The fraction (or percentage) of such chips is called the yield loss. Some bad chips pass tests. The fraction (or percentage) of bad chips among all passing chips is called the defect level. Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 10 Testing as Filter Process Good chips Prob(good) = y Prob(pass test) = high Tested chips Fabricated chips Defective chips Prob(bad) = 1- y Copyright 2001, Agrawal & Bushnell Mostly good chips Prob(fail test) = high Lecture 1 Introduction Mostly bad chips 11 Costs of Testing Design for testability (DFT) Chip area overhead and yield reduction Performance overhead Software processes of test Test generation and fault simulation Test programming and debugging Manufacturing test Automatic test equipment (ATE) capital cost Test center operational cost Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 12 Present and Future* * SIA Roadmap from www.siaonline.org, July 23, 2012 Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 13 Design for Testability (DFT) DFT refers to hardware design styles or added hardware that reduces test generation complexity. Motivation: Test generation complexity increases exponentially with the size of the circuit. Example: Test hardware applies tests to blocks A and B and to internal bus; avoids test generation for combined A and B blocks. Int. Primary Primary Logic bus Logic outputs inputs block A block B (PO) (PI) Test input Copyright 2001, Agrawal & Bushnell Test output Lecture 1 Introduction 14 Cost of Manufacturing Test in 2000AD 0.5-1.0GHz digital clock; analog instruments; 1,024 digital pins: ATE purchase price = $1.2M + 1,024 x $3,000 = $4.272M Annual running cost (five-year linear depreciation) = Depreciation (20%) + Maintenance (2%) + Operation ($0.5M) = $0.854M + $0.085M + $0.5M = $1.439M/year Test cost (24 hour ATE operation) = $1.439M/(365 x 24 x 3,600) = 4.5 cents/second Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 15 Roles of Testing Detection: Determination whether or not the device under test (DUT) has some fault. Diagnosis: Identification of a specific fault that is present on DUT. Device characterization: Determination and correction of errors in design and/or test procedure. Failure mode analysis (FMA): Determination of manufacturing process errors that may have caused defects on the DUT. Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 16 A Modern VLSI Device System-on-Chip (SOC) Data terminal Copyright 2001, Agrawal & Bushnell DSP core RAM ROM Interface logic Mixedsignal Codec Lecture 1 Introduction Transmission medium 17 Textbooks Digital, memory and mixed-signal: M. L. Bushnell and V. D. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, Springer, 2000. http://www.eng.auburn.edu/~vagrawal/BOOK/books.html RF testing J. Kelly and M. Engelhardt, Advanced Production Testing of RF, SoC, and SiP Devices, Boston: Artech House, 2007. B. Razavi, RF Microelectronics, Upper Saddle River, New Jersey: Prentice Hall PTR, 1998. K. B. Schaub and J. Kelly, Production Testing of RF and Systemon-a-chip Devices for Wireless Communications, Boston: Artech House, 2004. 1. 2. 3. Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 18 A Problem to Solve Using the testing cost obtained in Slide 15, determine what is the component of test in the cost of a mixed-signal VLSI chip for the following data: Analog test time = 1.5 s Digital test clock = 200MHz Number of digital test vectors = 109 Chip yield = 70% Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 19 Solution Assuming that one vector is applied per clock cycle during the digital test, the rate of test application is 200 million vectors per second. Therefore, Digital test time = (1000 × 106)/(200× 106) = 5 seconds Adding the analog test time, we get, Total test time = 1.5 + 5.0 = 6.5 seconds The testing cost for a 500 MHz, 1,024 pin tester was obtained as 4.56 cents in Slide 15. Thus, Cost of testing a chip = 6.5 × 4.56 = 29.64 cents The cost of testing bad chips should also be recovered from the price of good chips. Since the yield of good chips is 70%, we obtain Test cost per each good chip = 29.64/0.7 ≈ 42 cents 42 cents should be included as the cost of testing while figuring out the price of chips. Copyright 2001, Agrawal & Bushnell Lecture 1 Introduction 20